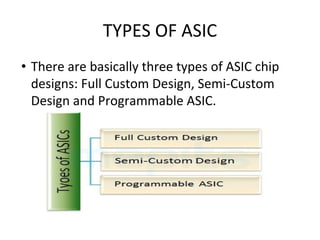

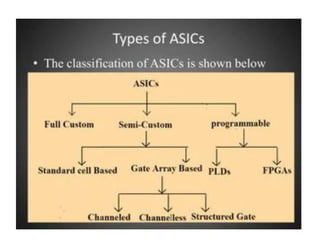

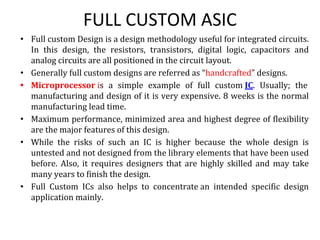

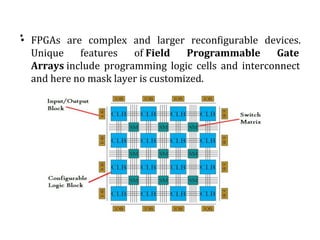

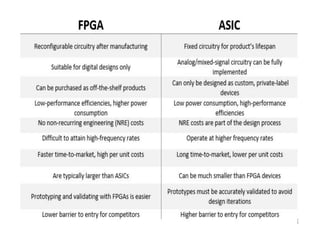

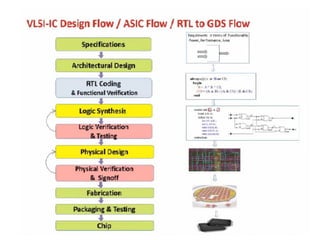

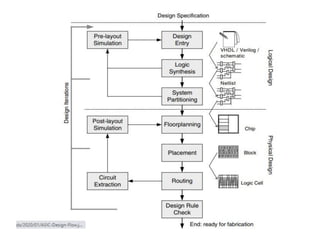

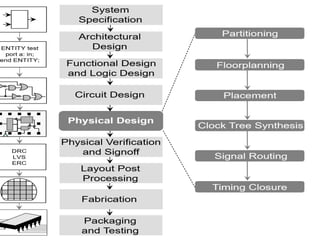

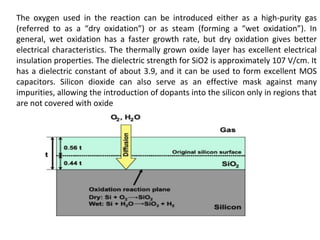

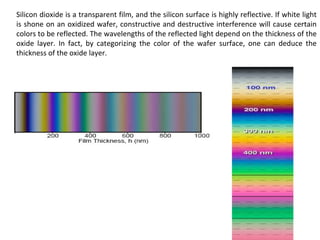

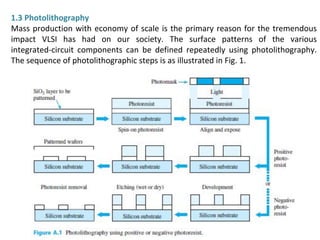

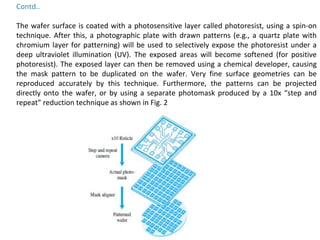

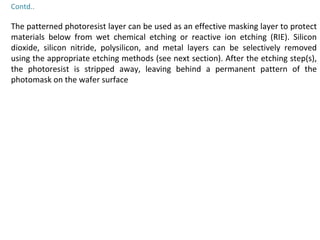

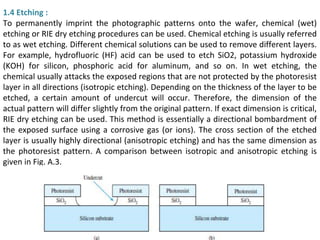

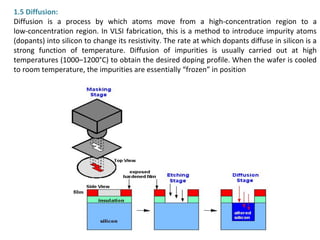

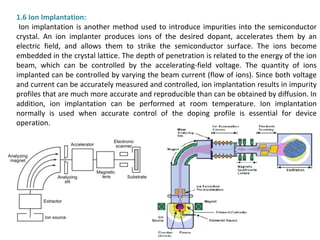

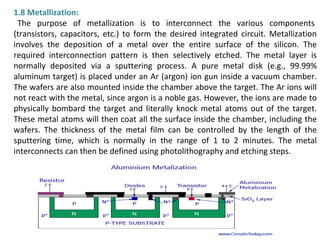

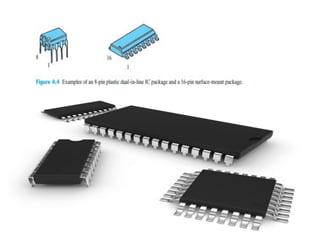

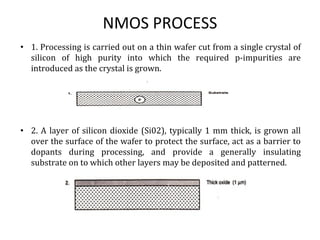

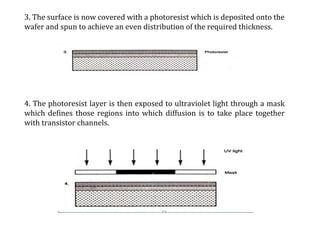

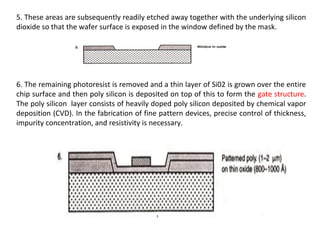

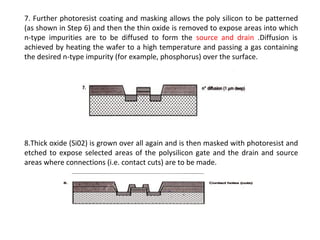

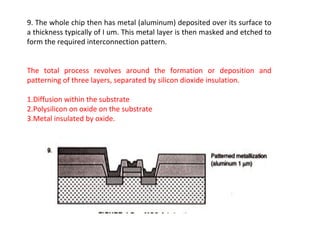

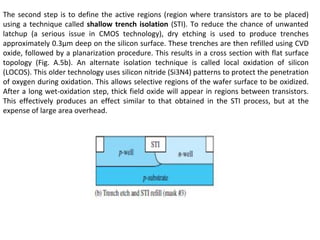

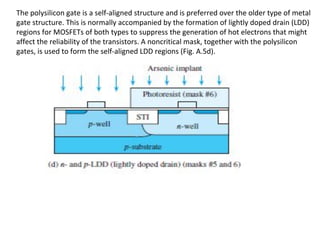

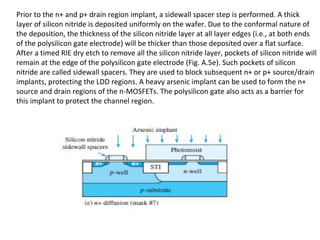

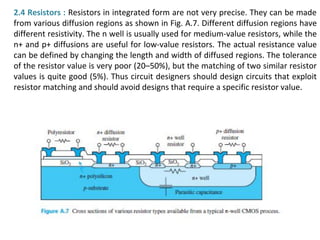

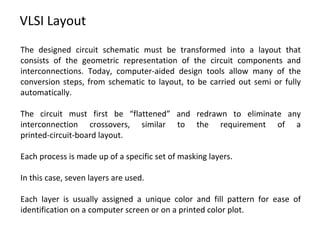

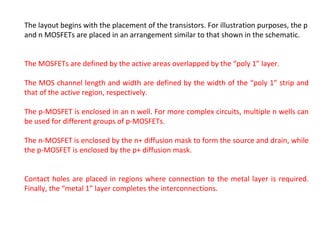

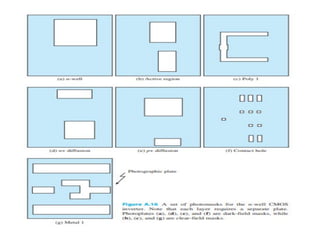

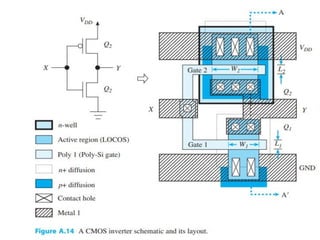

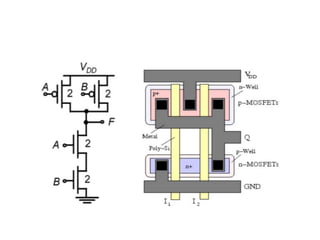

The document outlines VLSI fabrication technology, detailing the evolution of integrated circuits (ICs) from SSI to ULSI, highlighting key fabrication steps and the development of ASICs. It categorizes ASICs into full custom, semi-custom, and programmable designs, elaborating on their characteristics and advantages. IC fabrication steps include silicon wafer preparation, oxidation, photolithography, etching, and metallization, essential for modern IC production.