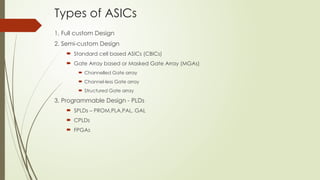

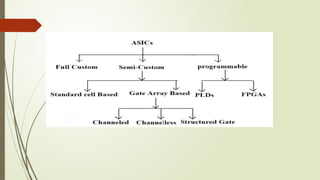

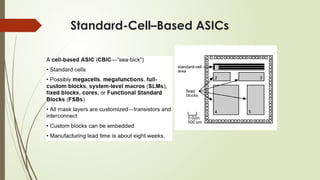

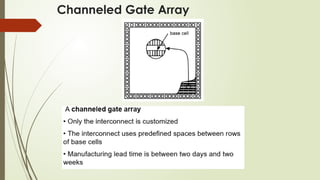

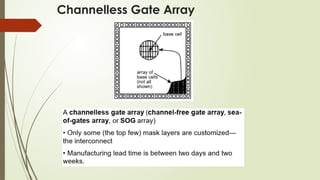

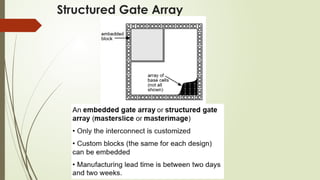

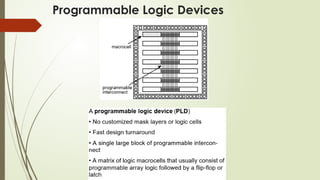

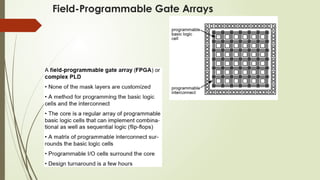

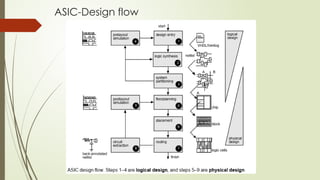

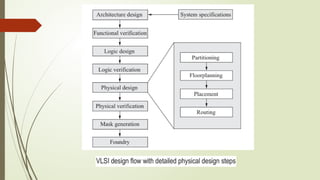

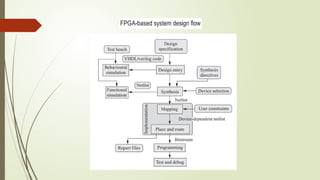

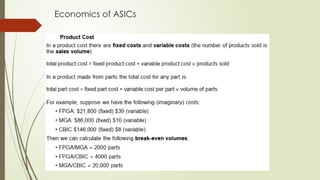

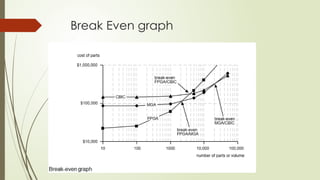

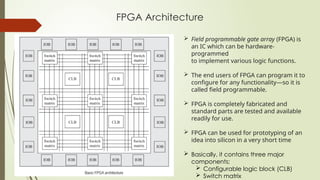

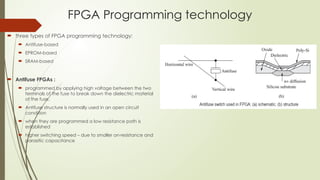

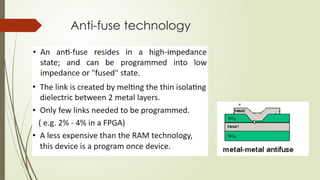

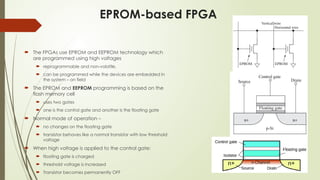

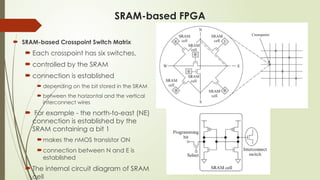

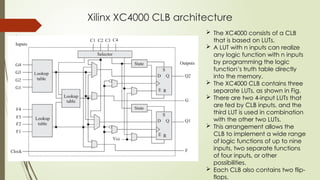

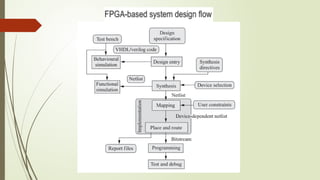

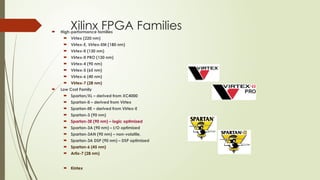

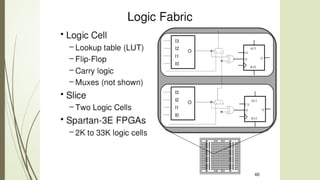

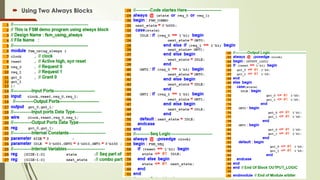

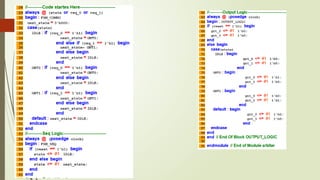

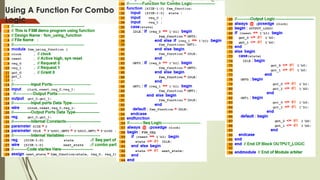

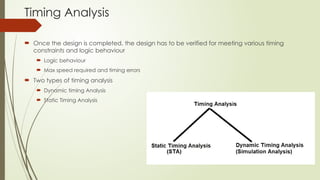

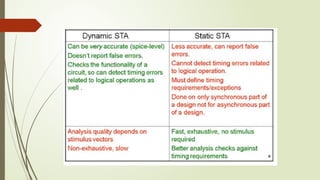

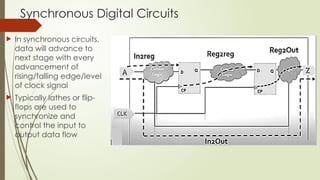

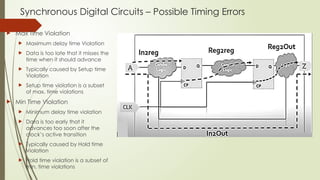

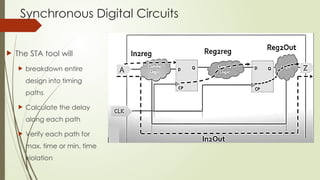

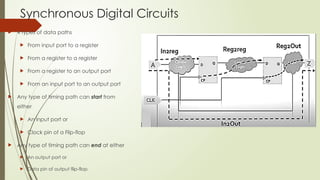

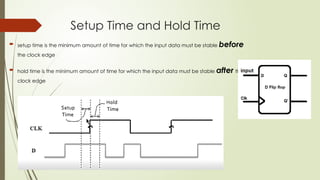

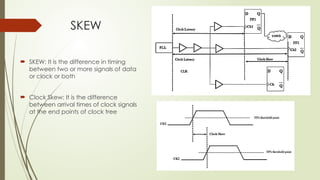

The document provides an overview of ASICs and FPGAs, detailing their types, design flows, and architectures. It discusses various programming technologies for FPGAs, such as antifuse, EPROM, and SRAM-based options, alongside the essential components like logic blocks and switch matrices. Additionally, it covers timing analysis, synchronous digital circuits, and relevant design considerations in FPGA implementation.