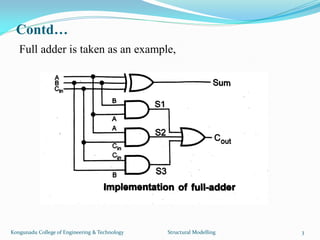

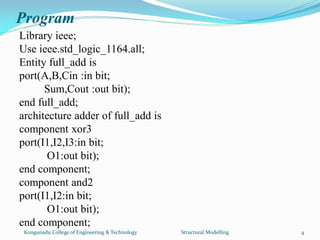

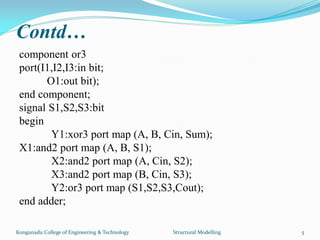

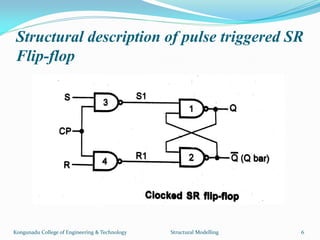

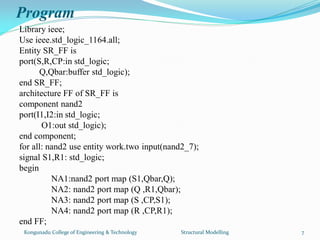

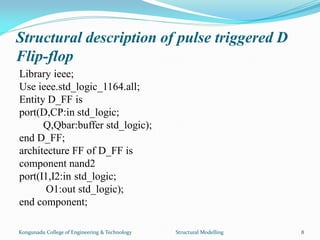

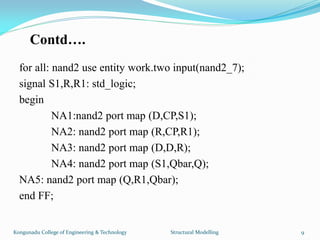

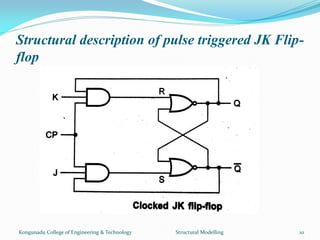

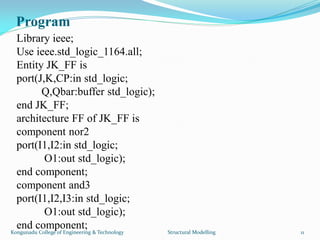

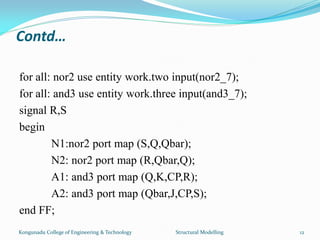

The document discusses structural modeling in VHDL. It provides examples of structurally modeling full adders, SR flip-flops, D flip-flops, and JK flip-flops by using components like XOR gates, AND gates, OR gates, and NAND gates. The structural modeling breaks down a design into its constituent components, allows each component to be simulated separately, and connects them using signals.