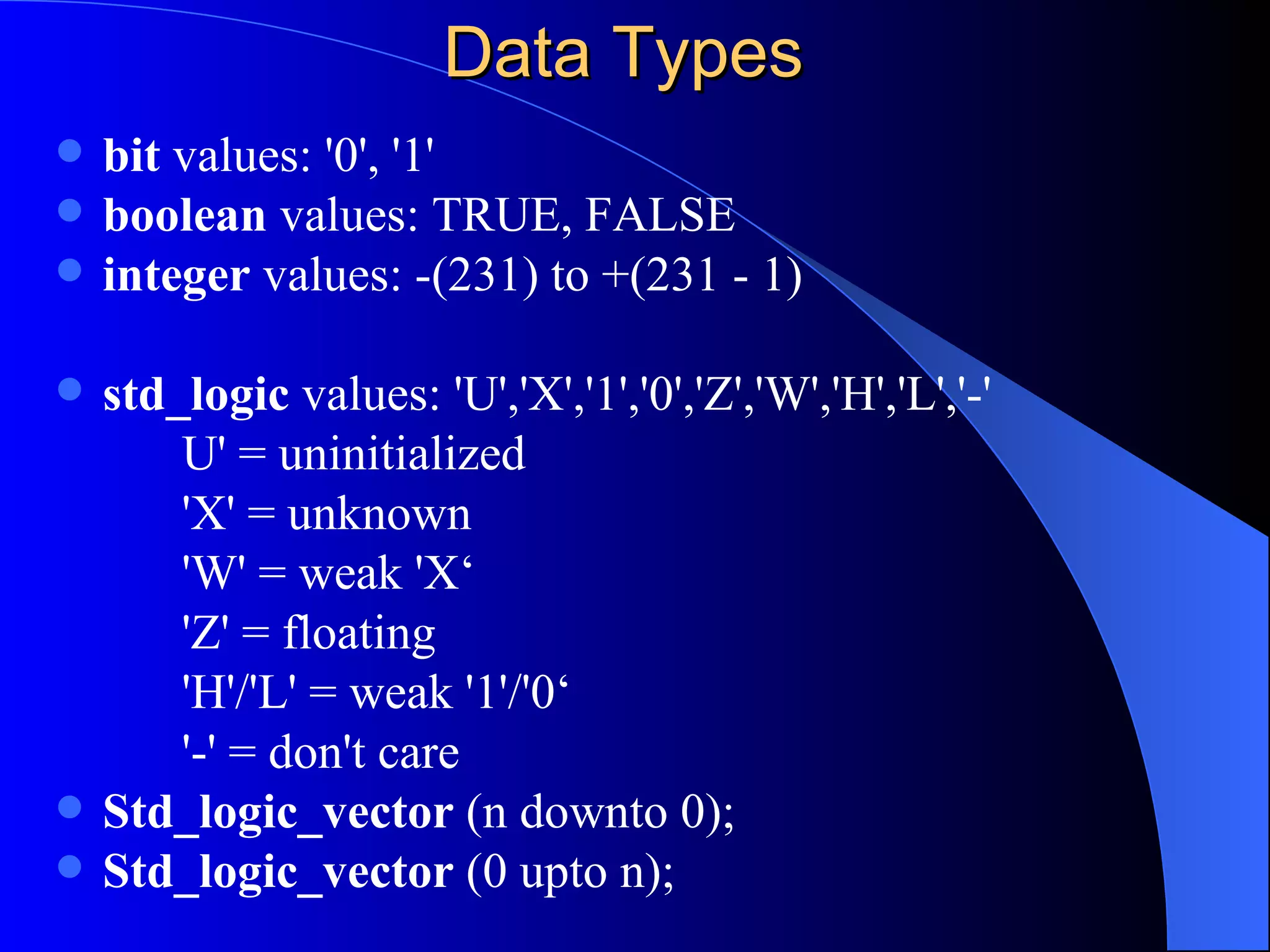

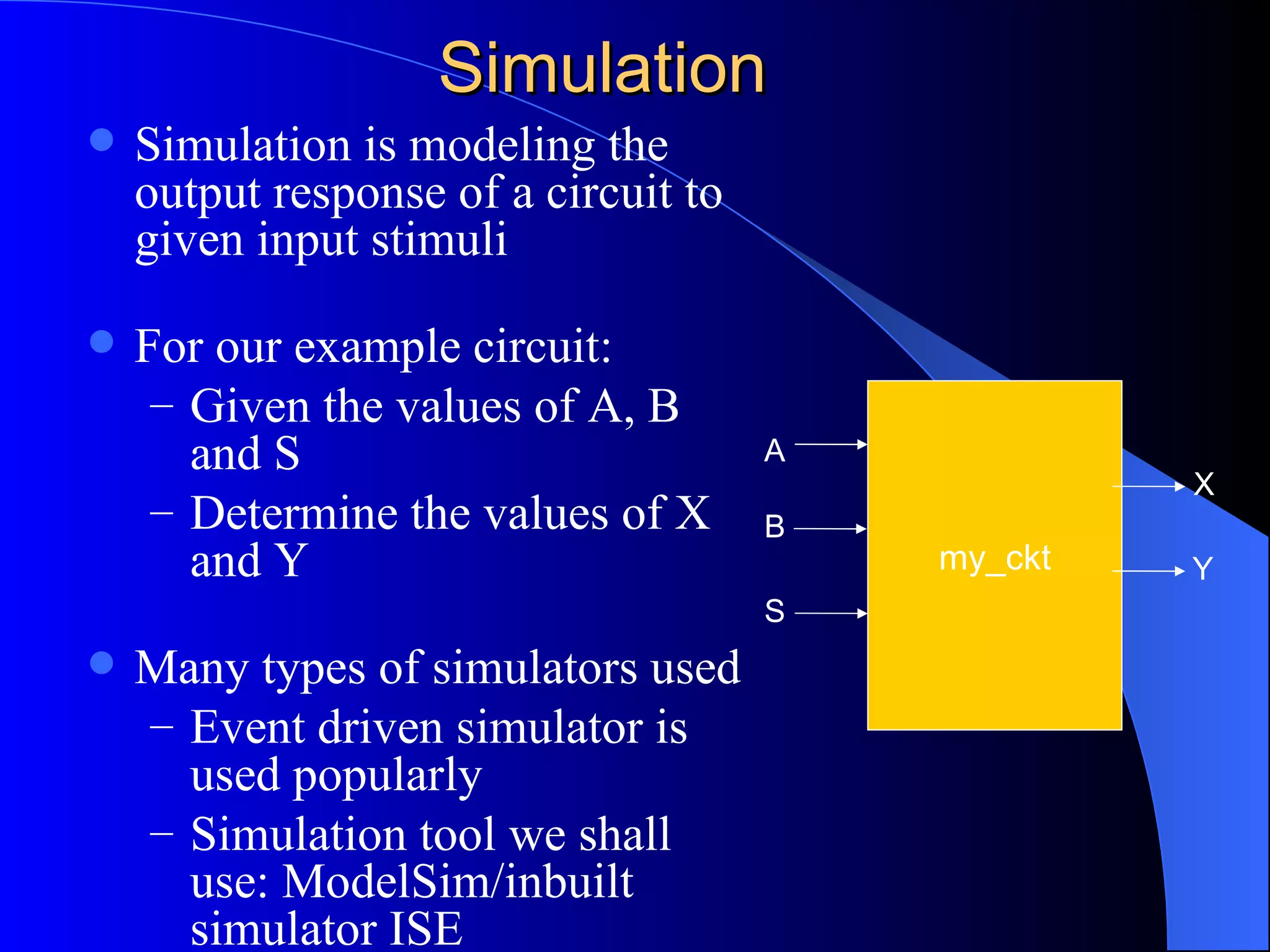

VHDL is a hardware description language used to model and design digital circuits. It can be used for simulation, synthesis, and verification of circuits. VHDL has different language elements like entities, architectures, processes, and packages that allow modeling at different levels of abstraction like behavioral, dataflow, and structural. Common data types in VHDL include std_logic, std_logic_vector, and integers. VHDL supports modeling concurrency using processes and signal assignments.