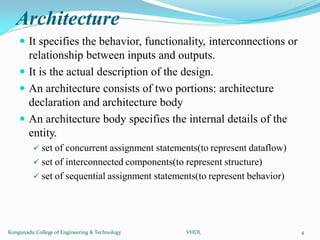

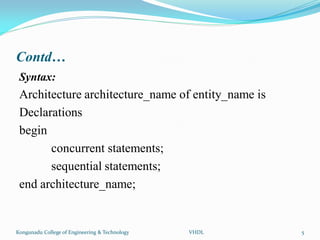

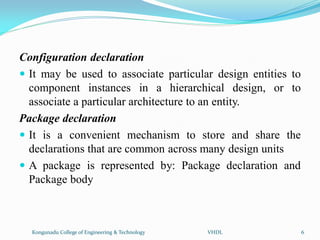

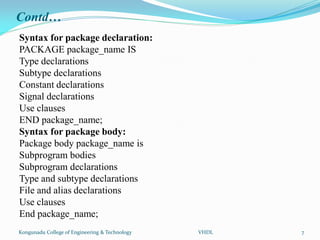

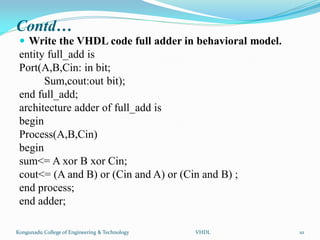

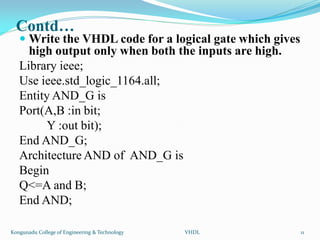

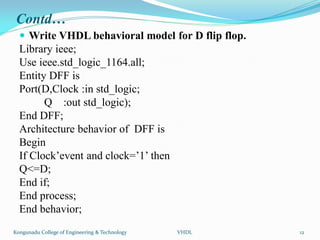

The document discusses the structure and behavioral modeling of VHDL. It explains the main components of VHDL structure including entity, architecture, package, and configuration. It provides examples of how to write behavioral models for half adder, full adder, AND gate, and D flip flop in VHDL. The document concludes with references for further reading on VHDL design.