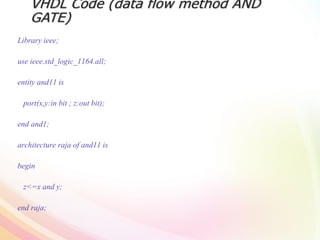

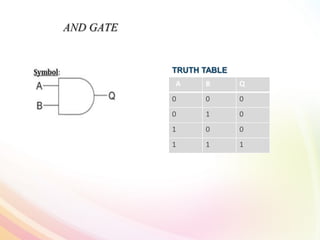

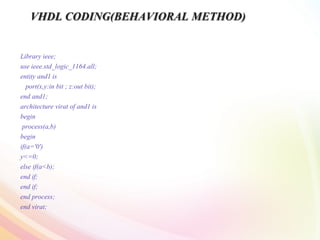

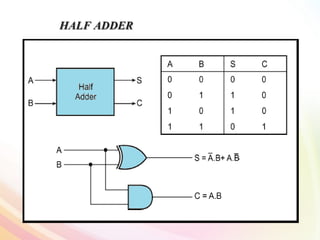

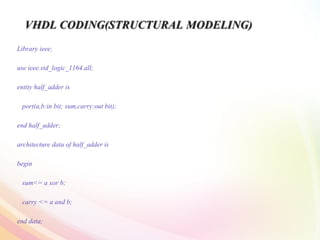

This document provides an introduction to basic coding in VHDL using Quartus software. It describes VHDL as a hardware description language used to model digital systems. It explains some key concepts in VHDL including entities, architectures, ports, processes, and the different modeling styles of structural, dataflow and behavioral. It provides examples of coding half adders and AND gates in VHDL.

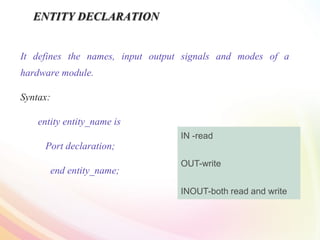

![entity entity-name is

[port(interface-signal-declaration);]

end [entity] [entity-name];

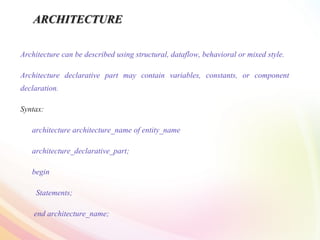

architecture architecture-name of entity-name is

[declarations]

begin

architecture body

end [architecture] [architecture-name];](https://image.slidesharecdn.com/0threview-171230052217/85/Basic-Coding-In-VHDL-COding-7-320.jpg)