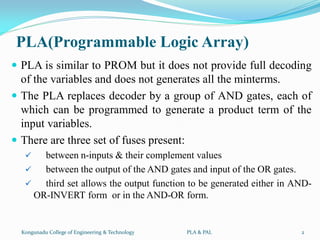

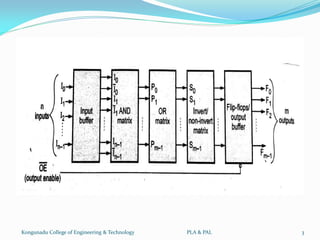

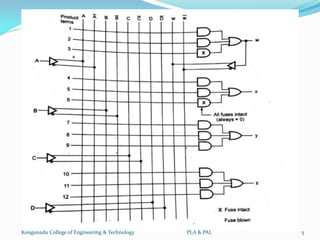

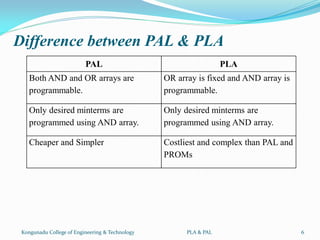

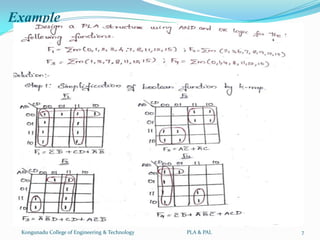

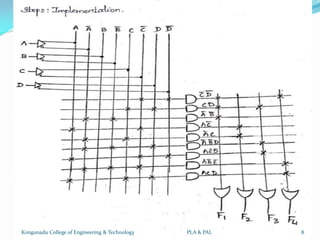

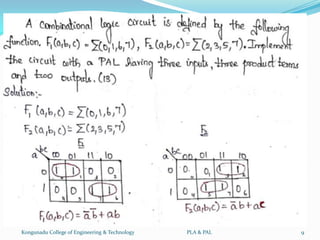

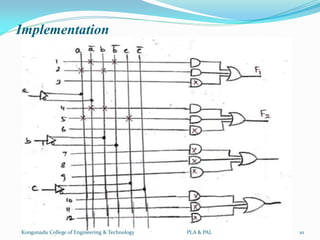

The document discusses Programmable Logic Arrays (PLAs) and Programmable Array Logic (PALs). It explains that a PLA is similar to a PROM but does not provide full decoding and generates only some minterms. It has three sets of fuses to program the AND gates, OR gates, and output function. A PAL has a fixed OR array and programmable AND array, making it easier to program but less flexible than a PLA. The differences between PLA and PAL are described, along with an example and implementation details.