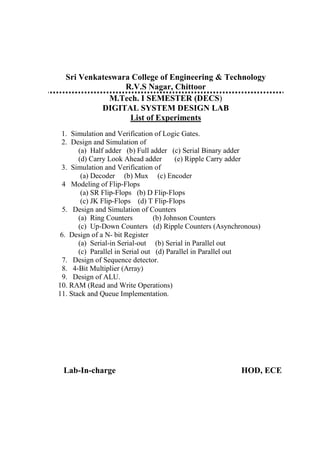

The document contains the list of experiments for the Digital System Design lab at Sri Venkateswara College of Engineering & Technology. The experiments include simulation and verification of logic gates, modeling of adders like half adder, full adder, ripple carry adder, carry look ahead adder and serial adder. Other experiments involve modeling of decoders, multiplexers, encoders and flip-flops. Additional experiments are design of counters, registers, sequence detectors, multipliers and ALU. The document also lists experiments on RAM operations and implementation of stacks and queues.