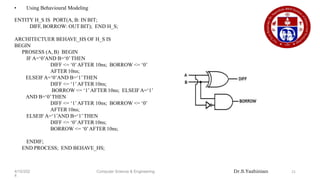

This document outlines the course content for the Digital Electronics course taught by Dr. S. Yazhinian during the summer semester of 2023-2024. The course covers combination logic circuits, HDL modeling styles including structural, dataflow and behavioral, and provides examples of modeling common combinational logic circuits like adders, subtractors, multiplexers and decoders in VHDL. It also demonstrates modeling priority encoders using conditional and sequential signal assignments.