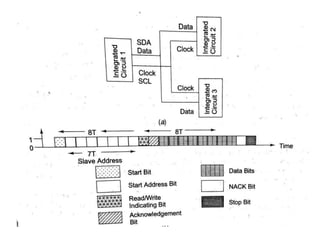

I2C is a popular serial bus standard developed by Philips for connecting integrated circuits. There are three I2C standards with different speeds. The I2C bus uses two lines - one for a clock signal and one for bidirectional data. Communication on the I2C bus follows a specific protocol with defined fields for the start bit, address, read/write control bits, data, and acknowledgement bits. A master device generates the clock signal and initiates data transfers by addressing slave devices to read from or write to.