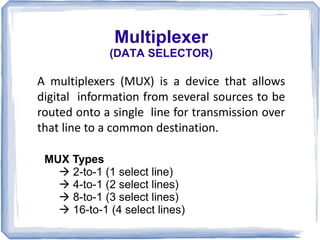

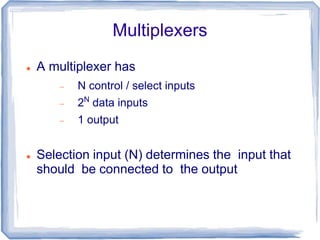

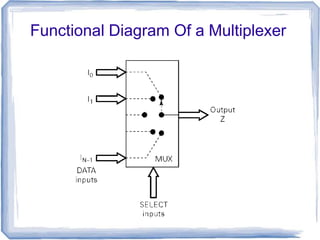

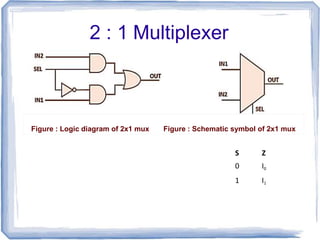

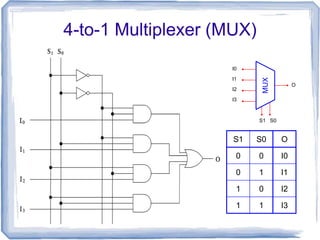

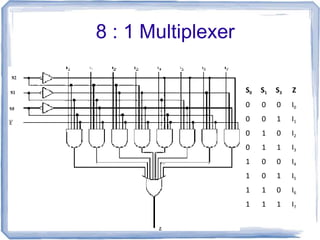

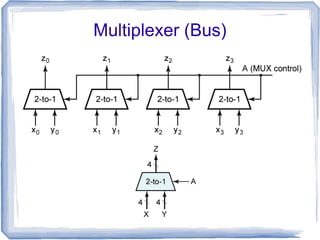

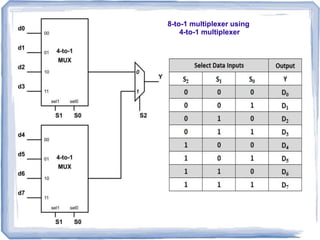

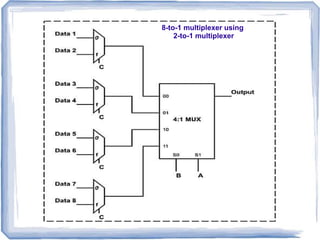

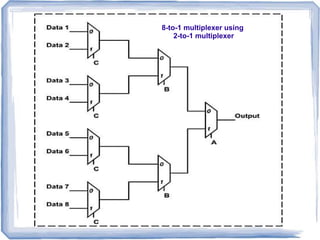

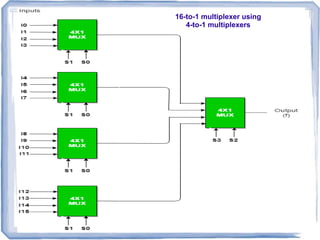

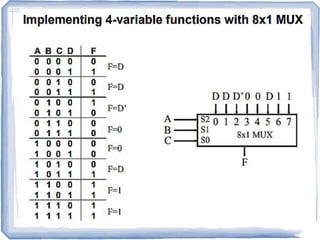

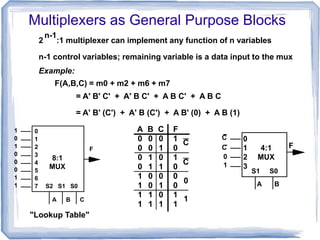

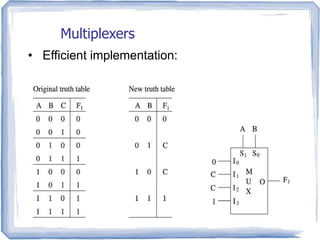

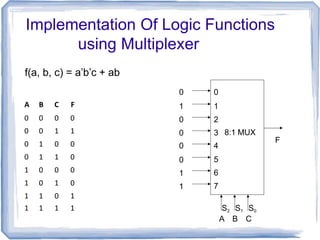

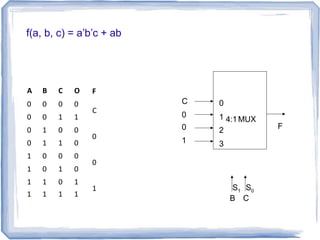

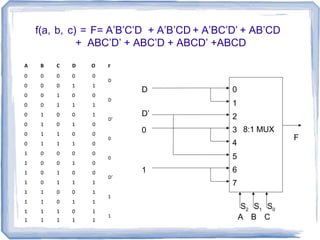

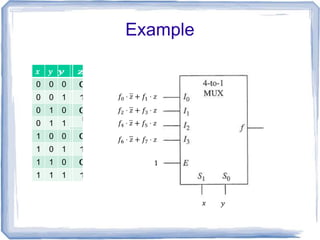

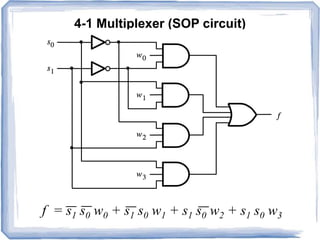

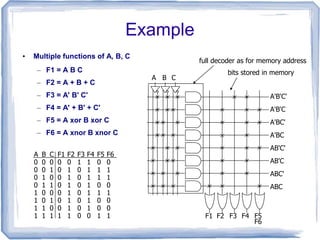

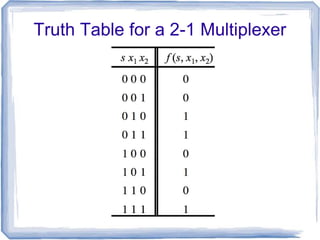

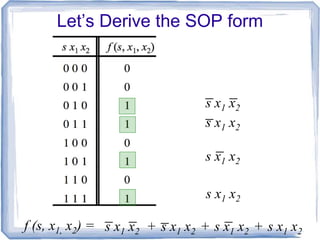

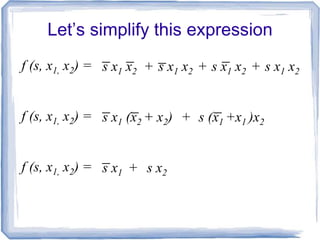

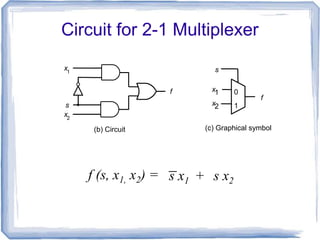

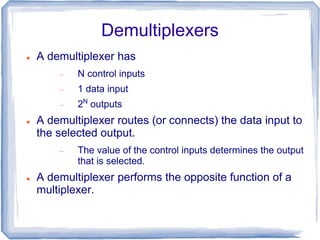

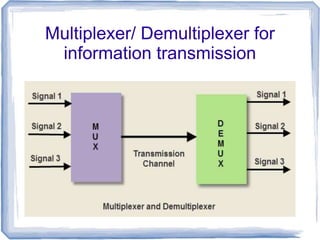

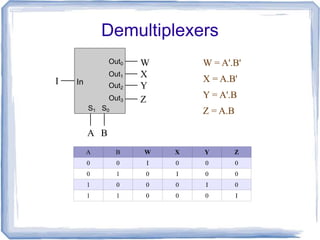

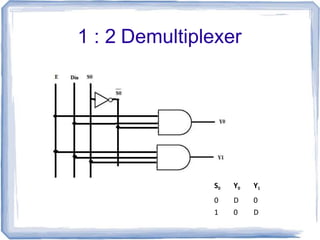

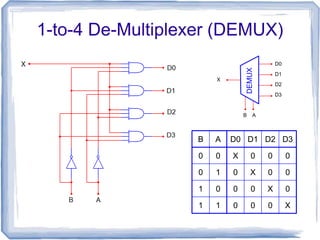

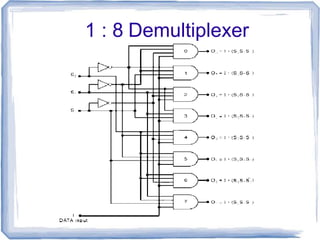

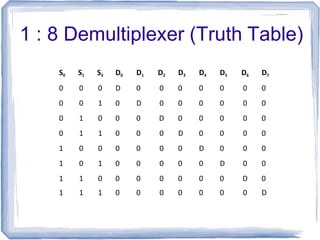

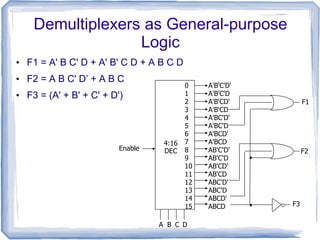

This document discusses multiplexers and demultiplexers. It defines them as devices that allow digital information from several sources to be routed onto a single line (multiplexers) or distributed to multiple output lines (demultiplexers). The key properties of multiplexers and demultiplexers are described, including the relationship between the number of inputs, outputs, and selection lines. Examples of implementing multiplexers and demultiplexers using logic gates are provided.