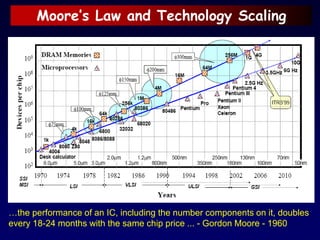

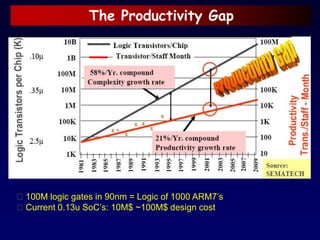

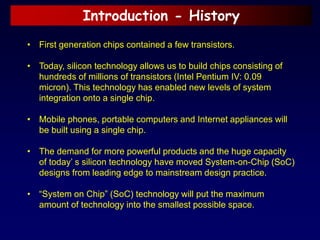

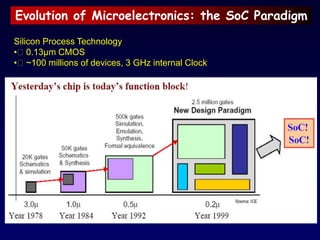

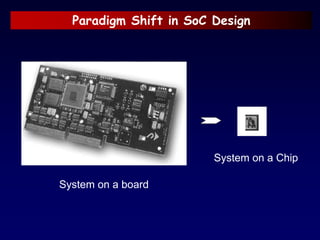

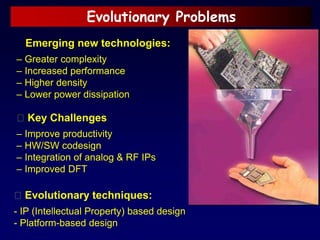

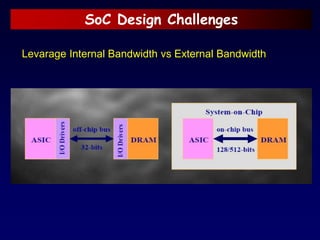

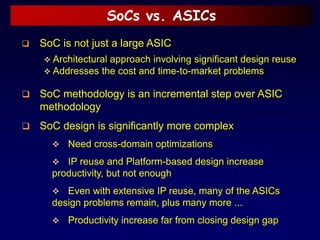

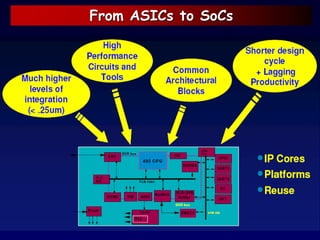

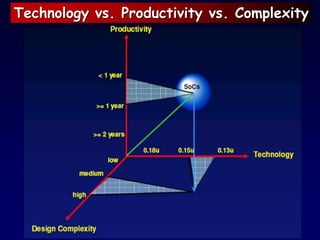

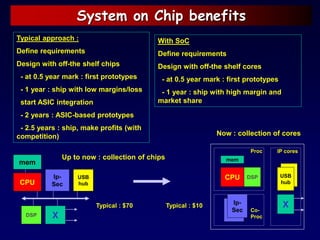

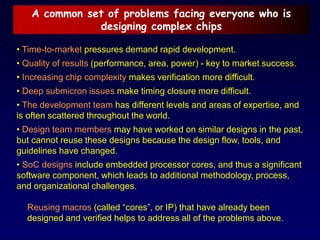

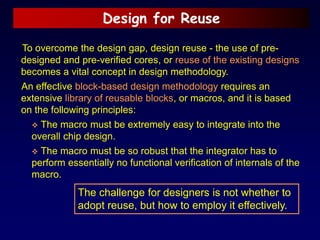

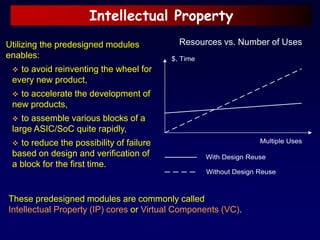

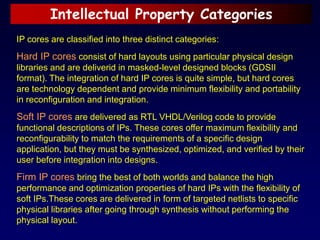

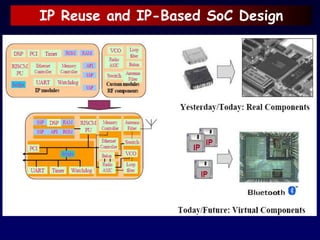

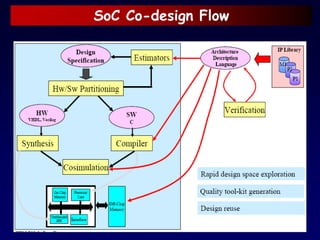

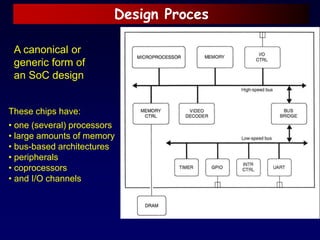

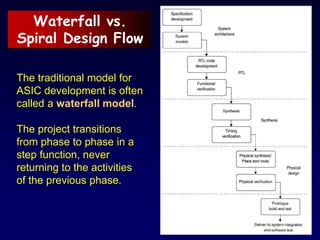

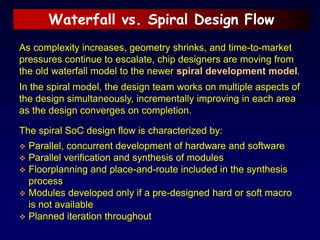

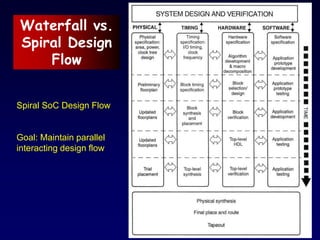

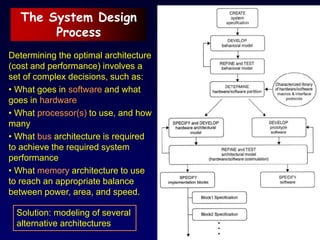

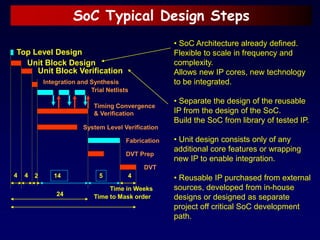

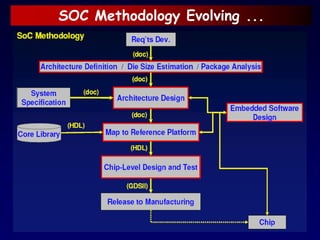

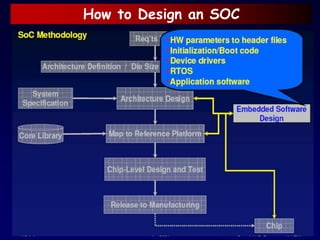

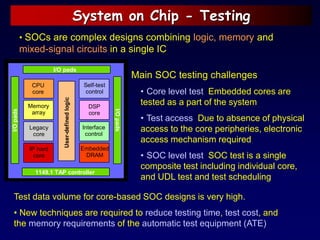

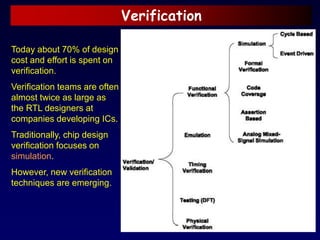

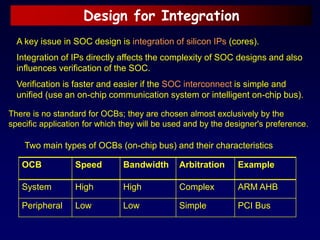

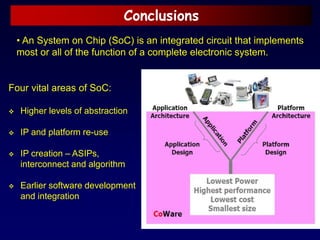

System on Chip (SoC) designs integrate multiple components, such as processors, memory, and I/O, onto a single chip. This consolidation provides benefits like reduced cost and power consumption compared to using multiple discrete chips. The SoC design process involves specifying system functionality, defining an architecture to implement it using reusable intellectual property cores, and employing techniques like hardware-software codesign and spiral development models to improve productivity. Key challenges in SoC design include managing complexity, meeting tight schedules, and ensuring high design quality and verification.