The document discusses trends and challenges in IP-based SoC design, highlighting modern design considerations such as power management, multi-processor systems, and reconfigurable logic. It emphasizes the necessity for testability and verification while addressing future challenges like embedded memory and network-on-chip architectures. The conclusion advocates for packet-switched networks-on-chip as a solution to complex SoC interconnect issues, projecting advancements in quality-of-service, fault-tolerance, and secure communication.

![Multi-Processor SoC

To further increase performance without substantially increasing power

consumption parallel processing can be used at the instruction level (e.g., VLIW

[27]) and at the data level (e.g., SIMD [65]).

Reconfigurable logic

To create high-performance, versatile platforms, some architectures start

logic operations and interconnects that can be reconfigured during run time.

Adding reconfigurable logic to the SoC provides flexibility for changing functionality

after fabrication. Compared to programmable processors, these architectures offer the

potential to achieve higher performance and power-efficiency with greater flexibility.

To boost the impact of reconfigurable SoCs, some research work has been done to

extract the parallelism from the applications/ algorithms and map the parallelism into

reconfigurable architecture efficiently.](https://image.slidesharecdn.com/trendsandchallengesinipbasedsocdesign-201211124330/85/Trends-and-challenges-in-IP-based-SOC-design-5-320.jpg)

![Scalable or Reusable Architecture

To ensure fast design turnaround time without completely redesigning the whole system, a

architecture is highly desired.

Just as we shifted our IC design paradigm from full custom design to standard cells, even to IP

reuse, the next-generation system design paradigm shift should be the reuse of architecture. That

to cope with the growing complexity of SoCs, IP reuse may not be enough.

Reuse must happen at a much higher level than it used to, e.g., architecture reuse [25]. However,

creating a design that can be efficiently reused requires a great deal of effort.

Network-on-Chip

While many communication architectures make use of buses or crossbars, there are some recent

proposals on network-on-chip (NoC) architectures.

One approach is to employ a packet-switched interconnect. The concept is similar to traditional

large-scale wide-area networks, but in this case, onchip router-based networks are used.](https://image.slidesharecdn.com/trendsandchallengesinipbasedsocdesign-201211124330/85/Trends-and-challenges-in-IP-based-SOC-design-8-320.jpg)

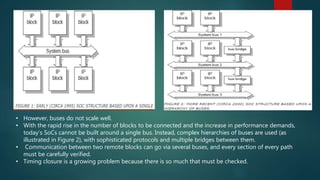

![• An example of a complex system-on-chip that employs the hierarchical bus solution is the DRACO

DECT-ISDN controller chip (see Figure 3) which was based around the Amulet3i asynchronous

processing subsystem [1].

• This chip incorporates two local processor buses serving the instruction and data requirements of the

Harvard architecture Amulet3 processor core, the asynchronous multi-master MARBLE bus with

production test support [2], and a bridge to a synchronous on-chip bus (SOCB in Figure 4) that serves

the clocked telecommunication peripherals.](https://image.slidesharecdn.com/trendsandchallengesinipbasedsocdesign-201211124330/85/Trends-and-challenges-in-IP-based-SOC-design-17-320.jpg)

![FUTURE REQUIREMENTS

The Silistix tools will provide designer-friendly support for selftimed networks-on-chip that

will deliver a robust and cost-effective solution to the requirement for a systematic approach

to on-chip interconnect for complex systems-on-chip. Beyond this, the future presents many

design challenges for on-chip interconnect.

Quality-of-Service (QoS) support is an obvious next-step, and the feasibility of providing QoS

support on an asynchronous NoC has already been demonstrated [6]. At present the cost of

implementing QoS is high compared with a best-effort network such as CHAIN, where it is

always possible to provide dedicated links for specific connections that require guaranteed

performance.

The current CHAIN technology assumes that on-chip logic is reliable. It is tolerant to delay

variations, but it is not designed to recover from logic faults or failures. It may become

necessary to design on the basis that on-chip logic is fallible, so that faulttolerance becomes

a requirement for all on-chip functions, including interconnect. Interconnect could be made

fault-tolerant by building redundancy into the fabric, but it is likely to be more cost-effective

(at the low expected error rates) to implement error detection and retry capabilities into the

interfaces, effectively adding faulttolerance as a layer on top of an unreliable fabric (as is the

case with off-chip networks).](https://image.slidesharecdn.com/trendsandchallengesinipbasedsocdesign-201211124330/85/Trends-and-challenges-in-IP-based-SOC-design-18-320.jpg)