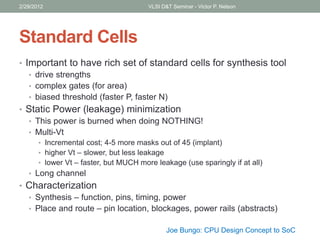

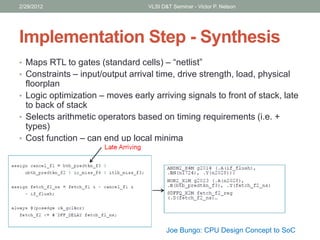

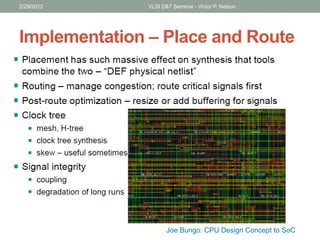

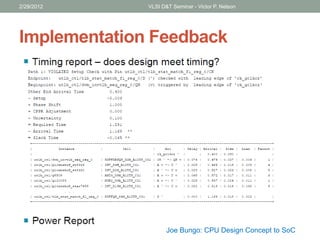

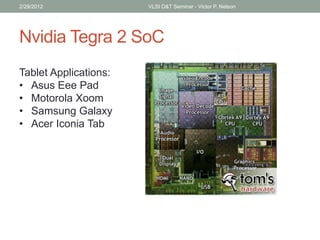

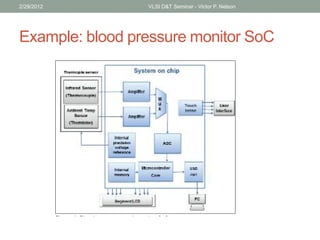

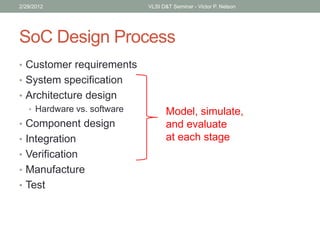

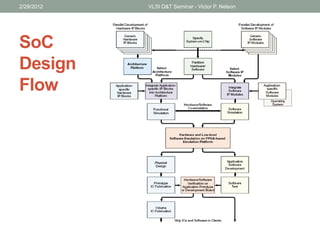

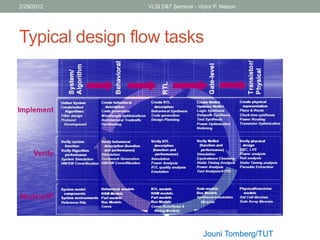

This document discusses systems on chip (SoCs) for embedded applications. It begins with an overview of what an embedded SoC is and then discusses intellectual property (IP) cores commonly used in SoCs, such as ARM processors and support modules. The document outlines the typical SoC design flow, including modeling and simulation, physical design, and integration. Examples of commercial SoCs are provided. Challenges in SoC design are discussed, such as increasing complexity, requirements for faster design times, and power management. The use of reusable IP blocks is described as a way to reduce costs and risks in SoC design.

![Implementation Style

• Custom

• Squeeze last % of performance from design

• Larger teams required

• Best suited to datapath elements:

• adders

• memories

• search [CAM] structures; reservation stations

• Automated Flow

• Synthesis, place and route

• Time to market

• Tools have gotten pretty good

• Dependent on good libraries (standard cell)

• Initial RTL is portable between processes

These are not mutually exclusive; even teams that use “custom” design

will use automated flow for non-critical or control blocks.

2/29/2012 VLSI D&T Seminar - Victor P. Nelson

Joe Bungo: CPU Design Concept to SoC](https://image.slidesharecdn.com/systemsonchipsoc-171130165813/85/Systems-on-chip-so-c-40-320.jpg)