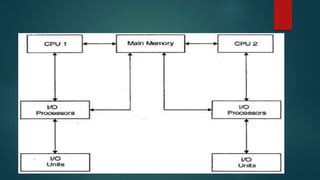

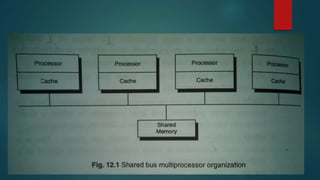

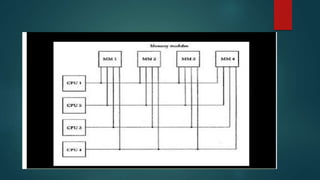

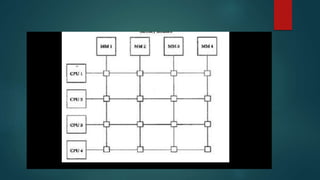

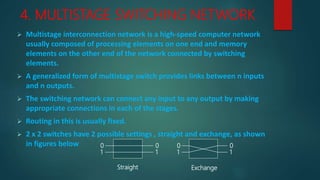

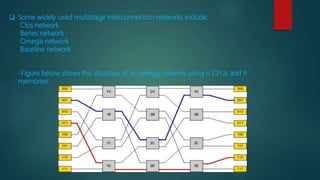

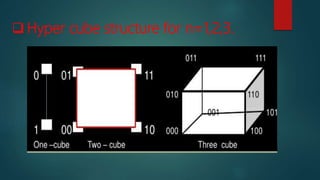

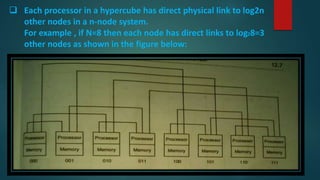

The document discusses multiprocessor systems, which consist of multiple CPUs sharing memory to enhance performance and reliability. It classifies these systems into tightly coupled and loosely coupled multiprocessors based on memory organization and interconnection structures, including bus-oriented systems, multiport memory, crossbar connection systems, multistage switching networks, and hypercube configurations. Each interconnection method has its advantages and disadvantages regarding performance and complexity.