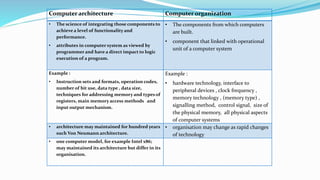

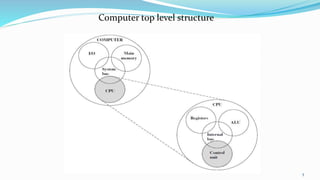

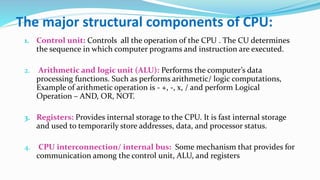

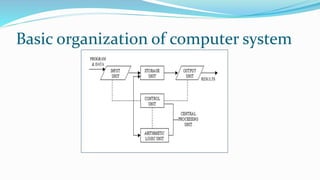

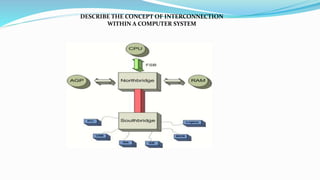

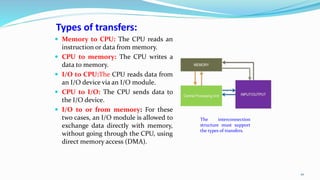

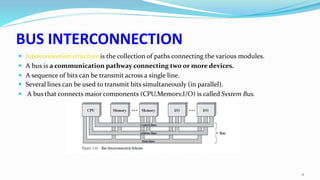

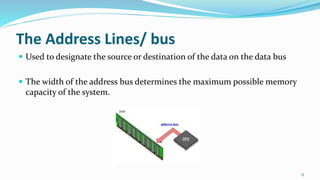

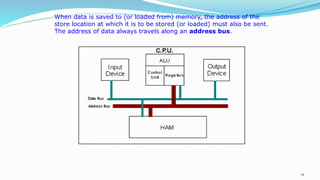

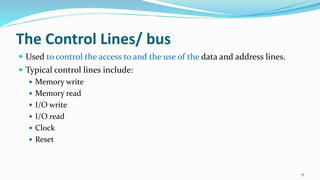

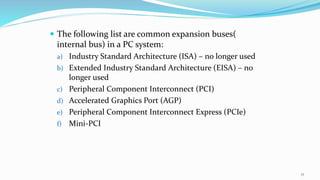

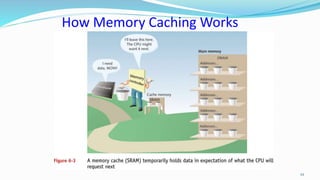

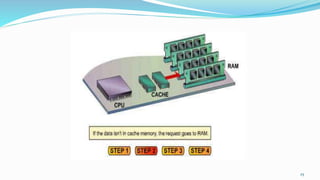

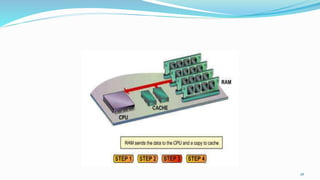

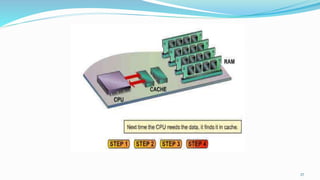

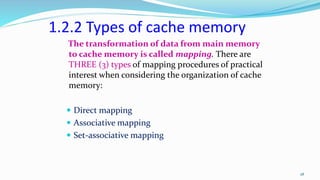

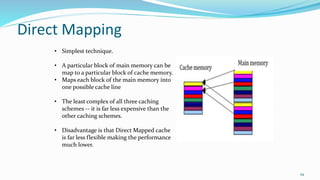

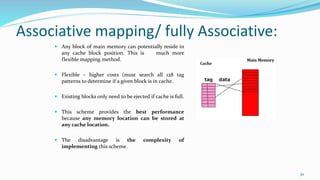

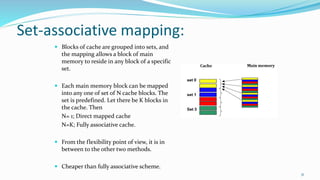

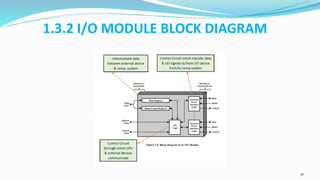

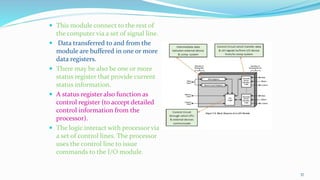

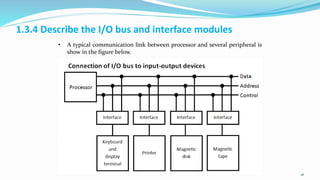

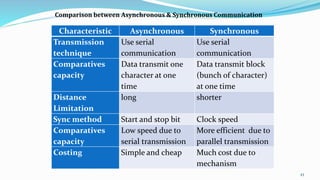

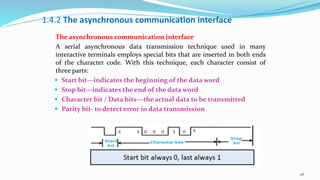

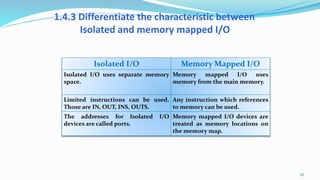

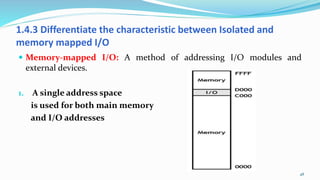

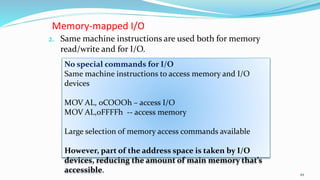

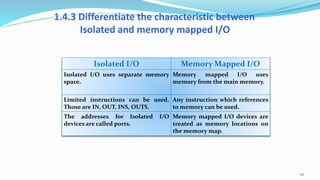

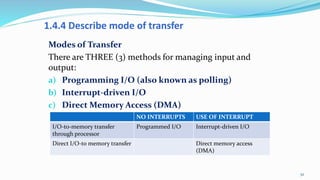

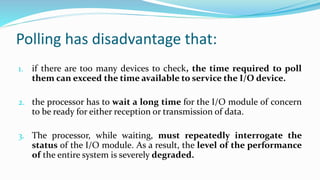

This document discusses computer architecture and organization concepts such as cache memory and input/output in computer systems. It defines computer architecture and organization, describes the major components of the CPU and their functions. It also explains the concept of interconnection within a computer system including bus interconnection, describes different types of cache memory mapping (direct, associative, set-associative) and cache initialization. Finally, it defines input/output modules, lists common I/O devices and describes I/O buses and interface modules.