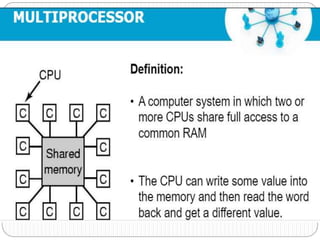

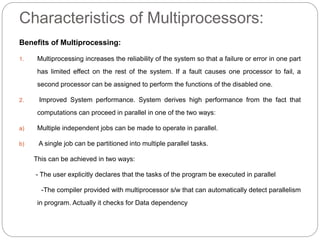

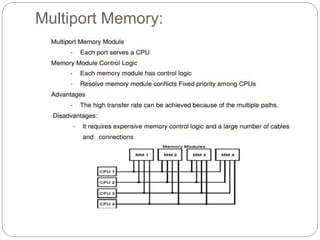

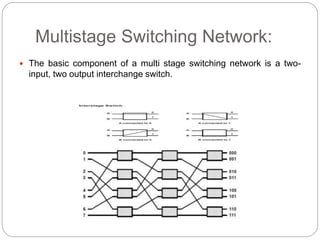

A multiprocessor system connects two or more CPUs with shared memory and I/O devices. It can be classified as MIMD, with multiple instruction streams and data streams allowing independent jobs or single jobs to run in parallel. Multiprocessors provide improved reliability and performance over single processors. They can be tightly coupled with shared memory or loosely coupled with distributed memory and message passing. Common interconnection structures include bus, multistage switching, and hypercube networks.