General/Digital up conversion

•Download as PPTX, PDF•

3 likes•3,311 views

digital down-converter (DDC) converts a digitized real signal centered at an intermediate frequency (IF) to a basebanded complex signal centered at zero frequency. In addition to downconversion

Report

Share

Report

Share

Recommended

Planar Passive Components and Filters (MMICs)

Monolithic Microwave integrated circuits devices and filters

Psk, qam, fsk different modulation

introduce the basic modulation tech (PSK, FSK, QAM etc)

and comparison between them.

ref : Communication System (4ed, Haykin)

this ppt is for my seminar

OFDM for LTE

Orthogonal Frequency Division Multiplexing, OFDM uses a large number of narrow sub-carriers for multi-carrier transmission to overcome the effect of multi path fading problem. LTE uses OFDM for the downlink, from base station to terminal to transmit the data over many narrow band careers of 180 KHz each instead of spreading one signal over the complete 5MHz career bandwidth. OFDM meets the LTE requirement for spectrum flexibility and enables cost-efficient solutions for very wide carriers with high peak rates.

The primary advantage of OFDM over single-carrier schemes is its ability to cope with severe channel conditions. Channel equalization is simplified. The low symbol rate makes the use of a guard interval between symbols affordable, making it possible to eliminate inter symbol interference (ISI).

Recommended

Planar Passive Components and Filters (MMICs)

Monolithic Microwave integrated circuits devices and filters

Psk, qam, fsk different modulation

introduce the basic modulation tech (PSK, FSK, QAM etc)

and comparison between them.

ref : Communication System (4ed, Haykin)

this ppt is for my seminar

OFDM for LTE

Orthogonal Frequency Division Multiplexing, OFDM uses a large number of narrow sub-carriers for multi-carrier transmission to overcome the effect of multi path fading problem. LTE uses OFDM for the downlink, from base station to terminal to transmit the data over many narrow band careers of 180 KHz each instead of spreading one signal over the complete 5MHz career bandwidth. OFDM meets the LTE requirement for spectrum flexibility and enables cost-efficient solutions for very wide carriers with high peak rates.

The primary advantage of OFDM over single-carrier schemes is its ability to cope with severe channel conditions. Channel equalization is simplified. The low symbol rate makes the use of a guard interval between symbols affordable, making it possible to eliminate inter symbol interference (ISI).

Design and implementation of qpsk modulator using digital subcarrier

The digitally implemented QPSK modulator is developed for satellite communication for future satellite missions. As we know that for space application power and bandwidth are most important parameters.The size of PCB and component count are also important parameters. To reduce these all parameters we design new approach. The new approach also minimizes the component count and hence reduces the PCB size. In this modulator summation, orthogonal sub-carrier generation and mixing of subcarrier with data are all digitally implemented inside the FPGA

Multirate DSP

link of a reference : http://www.slideshare.net/zena_mohammed/advanced-digital-signal-processing-bookcomputer.

Broadside array vs end fire array

Broadside Array vs end-fire array

Higher directivity.

Provide increased directivity in

elevation and azimuth planes.

Generally used for reception.

Impedance match difficulty in

high power transmissions.

Variants are:

Horizontal Array of Dipoles

RCA Fishborne Antenna

Series Phase Array

Hardware Implementation Of QPSK Modulator for Satellite Communications

QPSK Modulator is simulated on Matlab , FPGA is designed on Xilinx ISE and Implemented on Xilinx Virtex - 4 Development kit

Small scale fading

Channel issues

Accuracy of Models

Large-scale: Path loss

Medium-scale: Shadowing

Small-scale: Multipath fading

AIRCOM LTE Webinar 2 - Air Interface

This second webinar discusses LTE Air Interface, the link between a mobile device and the network, and a fundamental driver of the quality of the network.

Small scale fading and multipath measurements

Small-Scale Fading and Multipath measurements consists of PPT of UPTU Unit-1 Part 2

More Related Content

What's hot

Design and implementation of qpsk modulator using digital subcarrier

The digitally implemented QPSK modulator is developed for satellite communication for future satellite missions. As we know that for space application power and bandwidth are most important parameters.The size of PCB and component count are also important parameters. To reduce these all parameters we design new approach. The new approach also minimizes the component count and hence reduces the PCB size. In this modulator summation, orthogonal sub-carrier generation and mixing of subcarrier with data are all digitally implemented inside the FPGA

Multirate DSP

link of a reference : http://www.slideshare.net/zena_mohammed/advanced-digital-signal-processing-bookcomputer.

Broadside array vs end fire array

Broadside Array vs end-fire array

Higher directivity.

Provide increased directivity in

elevation and azimuth planes.

Generally used for reception.

Impedance match difficulty in

high power transmissions.

Variants are:

Horizontal Array of Dipoles

RCA Fishborne Antenna

Series Phase Array

Hardware Implementation Of QPSK Modulator for Satellite Communications

QPSK Modulator is simulated on Matlab , FPGA is designed on Xilinx ISE and Implemented on Xilinx Virtex - 4 Development kit

Small scale fading

Channel issues

Accuracy of Models

Large-scale: Path loss

Medium-scale: Shadowing

Small-scale: Multipath fading

AIRCOM LTE Webinar 2 - Air Interface

This second webinar discusses LTE Air Interface, the link between a mobile device and the network, and a fundamental driver of the quality of the network.

Small scale fading and multipath measurements

Small-Scale Fading and Multipath measurements consists of PPT of UPTU Unit-1 Part 2

What's hot (20)

Design and implementation of qpsk modulator using digital subcarrier

Design and implementation of qpsk modulator using digital subcarrier

Hardware Implementation Of QPSK Modulator for Satellite Communications

Hardware Implementation Of QPSK Modulator for Satellite Communications

Power delay profile,delay spread and doppler spread

Power delay profile,delay spread and doppler spread

Viewers also liked

Data Conversion: Hard Problems Made Easy - VE2013

Data conversion for data acquisition is a two-part process that involves sampling and then converting signals into digital venues. These processes inherently remove part of the complete analog signal in exchange for the power and robustness of digital signal handling. This becomes especially difficult when trying to capture signals at the limits of the resolution and speed of our systems. In this session, learn how to design a data conversion system that minimizes the signal loss to match the signal handling requirements … even on the hard ones.

Integrated Software-Defined Radio (SDR) - VE2013

This session combines the high speed analog signal chain from RF to baseband with FPGA-based digital signal processing for wireless communications. Topics include the high speed analog signal chain, direct conversion radio architecture, the high speed data converter interface, and FPGA-based digital signal processing for software-defined radio. The demo board uses the latest generation of Analog Devices’ high speed data converters, RF, and clocking devices, along with the Xilinx Zynq-7000 SoC. Other topics of discussion include the imperfections introduced by the modulator/demodulator with particular focus on the effect of temperature and frequency changes. In-factory and in-field algorithms that reduce the effect of these imperfections, with particular emphasis on the efficacy of in-factory set-and-forget algorithms, are examined.

What is 16 qam modulation

In this video, I will explain what is QAM modulation and what is 16QAM.

QAM Stands for Quadrature Amplitude Modulation. QAM is both an analog and a digital modulation method. But here, we are only talking about QAM as a digital modulation.

Quadrature means that two carrier waves are being used, one sine wave and one cosine wave. These two waves are out of phase with each other by 90°, this is called quadrature.

At the receiving end, the sine and cosine wave can be decoded independently, this means that by using both a sine wave and a cosine wave, the communication channel's capacity is doubled comparing to using only one sine or one cosine wave. That is why quadrature is such a popular technique for digital modulation.

QAM modulation is a combination of Amplitude Shift Keying and Phase Shift Keying, both carrier wave is modulated by changing both its amplitude and phase. As shown in this 8QAM waveform, the top is the sine wave carrier, for bit 000, the sin wave has a phase shift of 0°, and an amplitude of 2. While for bit 110, the phase shift is 180°, and the amplitude now is 1. So both phase and amplitude are changed.

In 16QAM, the input binary data is combined into groups of 4 bits called QUADBITS.

As shown in this picture, the I and I' bits are sent to the sine wave modulation path, and the Q and Q' bits are sent to the cosine wave path. Since the bits are split and sent in parallel, so the symbol rate has been reduced to a quarter of the input binary bit rate. If the input binary data rate is 100 Gbps, then the symbol rate is reduced to only 25 Gbaud/second. This is the reason why 16QAM is under hot research for 100Gbps fiber optic communication.

The I and Q bits control the carrier wave's phase shift, if the bit is 0, then the phase shift is 180°, if the bit is 1, then the phase shift is 0°.

The I' and Q' bits control the carrier wave's amplitude, if bit is 0, then the amplitude is 0.22 volt, if the bit is 1, then the amplitude is 0.821 volt.

So each pair of bits has 4 different outputs. Then they are added up at the linear summer. 4X4 is 16, so there is a total of 16 different combinations at the output, that is why this is called 16QAM.

This illustration shows an example of how the QUADBIT 0000 is modulated onto the carrier waves.

Here I and I' is 00, so the output is -0.22 Volt at the 2-to-4-level converter, when timed with the sine wave carrier, we get -0.22sin(2πfct), here fc is the carrier wave's frequency. QQ' is also 00, so the other carrier wave output is -0.22cos(2πfct).

Here is the proof that quadbit 0000 is modulated as a sine wave with an amplitude of 0.311volt and a phase shift of -135°. You can now pause for a moment to study the proof.

This list shows the 16QAM modulation output with different amplitude and phase change for all 16 quadbits. On the right side is the constellation diagram which shows the positions of these quadbits on a I-Q diagram.

You can visit FO4SALE.com f

Digital Modulation Techniques ppt

The most fundamental digital modulation techniques are based on keying: PSK (phase-shift keying): a finite number of phases are used. FSK (frequency-shift keying): a finite number of frequencies are used. ... QAM (quadrature amplitude modulation): a finite number of at least two phases and at least two amplitudes are used.

Digital modulation

This slide describe the techniques of digital modulation and Bandwidth Efficiency:

The first null bandwidth of M-ary PSK signals decrease as M increases while Rb is held constant.

Therefore, as the value of M increases, the bandwidth efficiency also increases.

RF Front End modules and components for cellphones 2017 - Report by Yole Deve...

A dynamic market with high responsivity to technical innovation, the RF front end industry is set to grow at 14% CAGR to reach $22.7B in 2022.

A market that will more than double in six years!

The radio-frequency (RF) front end and components market for cellphones is highly dynamic. From being worth $10.1B last year, it is expected to reach $22.7B in 2022. Such high growth is definitely something that players in other semiconductor markets would envy. However, the growth is not evenly distributed.

Filters represent the biggest business in the RF front end industry, and the value of this business will more than triple from 2016 to 2022. Most of this growth will derive from additional filtering needs from new antennas as well as the need for more filtering functionality due to multiple carrier aggregation (CA).

Power amplifiers (PAs) and low noise amplifiers (LNAs), the second biggest business, will be almost flat over the same period. High-end LTE PA market growth will be balanced by a shrinking 2G/3G market. The LNA market will grow steadily, especially thanks to the addition of new antennas.

Switches, the third biggest business, will double. This market will mainly be driven by antenna switches.

Lastly, antenna tuners, a small business today with an estimated $36M market value, will expand 7.5-fold to reach $272M in 2022. This growth is mainly due to tuning being added to both the main and the diversity antennas.

For more discussion, please visit our website: http://www.i-micronews.com/reports.html

Deep Learning - The Past, Present and Future of Artificial Intelligence

In the last couple of years, deep learning techniques have transformed the world of artificial intelligence. One by one, the abilities and techniques that humans once imagined were uniquely our own have begun to fall to the onslaught of ever more powerful machines. Deep neural networks are now better than humans at tasks such as face recognition and object recognition. They’ve mastered the ancient game of Go and thrashed the best human players. “The pace of progress in artificial general intelligence is incredible fast” (Elon Musk – CEO Tesla & SpaceX) leading to an AI that “would be either the best or the worst thing ever to happen to humanity” (Stephen Hawking – Physicist).

What sparked this new hype? How is Deep Learning different from previous approaches? Let’s look behind the curtain and unravel the reality. This talk will introduce the core concept of deep learning, explore why Sundar Pichai (CEO Google) recently announced that “machine learning is a core transformative way by which Google is rethinking everything they are doing” and explain why “deep learning is probably one of the most exciting things that is happening in the computer industry“ (Jen-Hsun Huang – CEO NVIDIA).

Viewers also liked (14)

RF Front End modules and components for cellphones 2017 - Report by Yole Deve...

RF Front End modules and components for cellphones 2017 - Report by Yole Deve...

Deep Learning - The Past, Present and Future of Artificial Intelligence

Deep Learning - The Past, Present and Future of Artificial Intelligence

Similar to General/Digital up conversion

IEEE_RFIC 2007

Presentation of the work published in RFIC 2007 Conference. PLL and FSK modulator design in 130nm-CMOS

DSP_2018_FOEHU - Lec 07 - IIR Filter Design

Digital Signal Processing - 2018

Faculty of Engineering

Helwan University

Synchronous Time / Frequency Domain Measurements Using a Digital Oscilloscope...

Synchronous Time / Frequency Domain Measurements Using a Digital Oscilloscope...Rohde & Schwarz North America

Embedded systems increasingly employ digital, analog and RF signals all of which are tightly synchronized in time. Debugging these systems is challenging in that one needs to measure a number of different signals in one or more domains (time, digital, frequency) and with tight time synchronization. This session will discuss how a digital oscilloscope can be used to effectively debug these systems, and some of the instrumentation considerations that go along with this.AD8351.pdf

DIFFERENTIAL RF/IF AMPLIFIER, 26DB, 2.2GHZ, Frequency Max:2.2GHz, Gain:26dB, Supply Voltage Min:3V, Supply Voltage Max:5.5V

Design of Energy- and Area-Efficient Sensor Readout Circuits (Chih-Chan Tu)

PhD Defense

Chih-Chan Tu

Date: Apr. 13th, 2018

Ims2016 micro apps_robertbrennan_pll_frequencyplanning_v2

PLL Frequency Planning for Spurious Signal Elimination: IMS2016 Presentation

Fundamentals of Analog and Digital Modulation PPT.pptx

Fundamentals of Analog and Digital Modulation PPT

Frequency-Shift Keying

Frequency-Shift Keying, also known as FSK is a type of digital frequency modulation. It is also often called as binary frequency shift keying or BFSK

Similar to analog FM, it is a constant-amplitude angle modulation.

This presentation will discuss the concepts behind FSK

RT15 Berkeley | Requirements on Power Amplifiers and HIL Real-Time Processors...

RT15 Berkeley | Requirements on Power Amplifiers and HIL Real-Time Processors...OPAL-RT TECHNOLOGIES

Presented by Gernot Pammer at OPAL-RT RT15 User Group event in Berkeley on May 13-14, 20159420 datasheet

The 9420 series pulse generator was designed to meet the growing demand for an affordable yet flexible system synchronizer. This benchtop, lab ready, delay generator comes standard with a 10ns timing resolution and a low jitter of less than 400ps. The simple programming, high functionality, and easy memory recall makes this model ideal for multiple projects and a wide variety of applications.

Similar to General/Digital up conversion (20)

Synchronous Time / Frequency Domain Measurements Using a Digital Oscilloscope...

Synchronous Time / Frequency Domain Measurements Using a Digital Oscilloscope...

Design of Energy- and Area-Efficient Sensor Readout Circuits (Chih-Chan Tu)

Design of Energy- and Area-Efficient Sensor Readout Circuits (Chih-Chan Tu)

Ims2016 micro apps_robertbrennan_pll_frequencyplanning_v2

Ims2016 micro apps_robertbrennan_pll_frequencyplanning_v2

Fundamentals of Analog and Digital Modulation PPT.pptx

Fundamentals of Analog and Digital Modulation PPT.pptx

RT15 Berkeley | Requirements on Power Amplifiers and HIL Real-Time Processors...

RT15 Berkeley | Requirements on Power Amplifiers and HIL Real-Time Processors...

Recently uploaded

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.

Thank me later.

samsarthak31@gmail.com

Design and Analysis of Algorithms-DP,Backtracking,Graphs,B&B

Dynamic Programming

Backtracking

Techniques for Graphs

Branch and Bound

Nuclear Power Economics and Structuring 2024

Title: Nuclear Power Economics and Structuring - 2024 Edition

Produced by: World Nuclear Association Published: April 2024

Report No. 2024/001

© 2024 World Nuclear Association.

Registered in England and Wales, company number 01215741

This report reflects the views

of industry experts but does not

necessarily represent those

of World Nuclear Association’s

individual member organizations.

Water Industry Process Automation and Control Monthly - May 2024.pdf

Water Industry Process Automation and Control Monthly - May 2024.pdfWater Industry Process Automation & Control

Welcome to WIPAC Monthly the magazine brought to you by the LinkedIn Group Water Industry Process Automation & Control.

In this month's edition, along with this month's industry news to celebrate the 13 years since the group was created we have articles including

A case study of the used of Advanced Process Control at the Wastewater Treatment works at Lleida in Spain

A look back on an article on smart wastewater networks in order to see how the industry has measured up in the interim around the adoption of Digital Transformation in the Water Industry.Student information management system project report ii.pdf

Our project explains about the student management. This project mainly explains the various actions related to student details. This project shows some ease in adding, editing and deleting the student details. It also provides a less time consuming process for viewing, adding, editing and deleting the marks of the students.

Automobile Management System Project Report.pdf

The proposed project is developed to manage the automobile in the automobile dealer company. The main module in this project is login, automobile management, customer management, sales, complaints and reports. The first module is the login. The automobile showroom owner should login to the project for usage. The username and password are verified and if it is correct, next form opens. If the username and password are not correct, it shows the error message.

When a customer search for a automobile, if the automobile is available, they will be taken to a page that shows the details of the automobile including automobile name, automobile ID, quantity, price etc. “Automobile Management System” is useful for maintaining automobiles, customers effectively and hence helps for establishing good relation between customer and automobile organization. It contains various customized modules for effectively maintaining automobiles and stock information accurately and safely.

When the automobile is sold to the customer, stock will be reduced automatically. When a new purchase is made, stock will be increased automatically. While selecting automobiles for sale, the proposed software will automatically check for total number of available stock of that particular item, if the total stock of that particular item is less than 5, software will notify the user to purchase the particular item.

Also when the user tries to sale items which are not in stock, the system will prompt the user that the stock is not enough. Customers of this system can search for a automobile; can purchase a automobile easily by selecting fast. On the other hand the stock of automobiles can be maintained perfectly by the automobile shop manager overcoming the drawbacks of existing system.

COLLEGE BUS MANAGEMENT SYSTEM PROJECT REPORT.pdf

The College Bus Management system is completely developed by Visual Basic .NET Version. The application is connect with most secured database language MS SQL Server. The application is develop by using best combination of front-end and back-end languages. The application is totally design like flat user interface. This flat user interface is more attractive user interface in 2017. The application is gives more important to the system functionality. The application is to manage the student’s details, driver’s details, bus details, bus route details, bus fees details and more. The application has only one unit for admin. The admin can manage the entire application. The admin can login into the application by using username and password of the admin. The application is develop for big and small colleges. It is more user friendly for non-computer person. Even they can easily learn how to manage the application within hours. The application is more secure by the admin. The system will give an effective output for the VB.Net and SQL Server given as input to the system. The compiled java program given as input to the system, after scanning the program will generate different reports. The application generates the report for users. The admin can view and download the report of the data. The application deliver the excel format reports. Because, excel formatted reports is very easy to understand the income and expense of the college bus. This application is mainly develop for windows operating system users. In 2017, 73% of people enterprises are using windows operating system. So the application will easily install for all the windows operating system users. The application-developed size is very low. The application consumes very low space in disk. Therefore, the user can allocate very minimum local disk space for this application.

Quality defects in TMT Bars, Possible causes and Potential Solutions.

Maintaining high-quality standards in the production of TMT bars is crucial for ensuring structural integrity in construction. Addressing common defects through careful monitoring, standardized processes, and advanced technology can significantly improve the quality of TMT bars. Continuous training and adherence to quality control measures will also play a pivotal role in minimizing these defects.

HYDROPOWER - Hydroelectric power generation

Overview of the fundamental roles in Hydropower generation and the components involved in wider Electrical Engineering.

This paper presents the design and construction of hydroelectric dams from the hydrologist’s survey of the valley before construction, all aspects and involved disciplines, fluid dynamics, structural engineering, generation and mains frequency regulation to the very transmission of power through the network in the United Kingdom.

Author: Robbie Edward Sayers

Collaborators and co editors: Charlie Sims and Connor Healey.

(C) 2024 Robbie E. Sayers

Vaccine management system project report documentation..pdf

The Division of Vaccine and Immunization is facing increasing difficulty monitoring vaccines and other commodities distribution once they have been distributed from the national stores. With the introduction of new vaccines, more challenges have been anticipated with this additions posing serious threat to the already over strained vaccine supply chain system in Kenya.

Architectural Portfolio Sean Lockwood

This portfolio contains selected projects I completed during my undergraduate studies. 2018 - 2023

在线办理(ANU毕业证书)澳洲国立大学毕业证录取通知书一模一样

学校原件一模一样【微信:741003700 】《(ANU毕业证书)澳洲国立大学毕业证》【微信:741003700 】学位证,留信认证(真实可查,永久存档)原件一模一样纸张工艺/offer、雅思、外壳等材料/诚信可靠,可直接看成品样本,帮您解决无法毕业带来的各种难题!外壳,原版制作,诚信可靠,可直接看成品样本。行业标杆!精益求精,诚心合作,真诚制作!多年品质 ,按需精细制作,24小时接单,全套进口原装设备。十五年致力于帮助留学生解决难题,包您满意。

本公司拥有海外各大学样板无数,能完美还原。

1:1完美还原海外各大学毕业材料上的工艺:水印,阴影底纹,钢印LOGO烫金烫银,LOGO烫金烫银复合重叠。文字图案浮雕、激光镭射、紫外荧光、温感、复印防伪等防伪工艺。材料咨询办理、认证咨询办理请加学历顾问Q/微741003700

【主营项目】

一.毕业证【q微741003700】成绩单、使馆认证、教育部认证、雅思托福成绩单、学生卡等!

二.真实使馆公证(即留学回国人员证明,不成功不收费)

三.真实教育部学历学位认证(教育部存档!教育部留服网站永久可查)

四.办理各国各大学文凭(一对一专业服务,可全程监控跟踪进度)

如果您处于以下几种情况:

◇在校期间,因各种原因未能顺利毕业……拿不到官方毕业证【q/微741003700】

◇面对父母的压力,希望尽快拿到;

◇不清楚认证流程以及材料该如何准备;

◇回国时间很长,忘记办理;

◇回国马上就要找工作,办给用人单位看;

◇企事业单位必须要求办理的

◇需要报考公务员、购买免税车、落转户口

◇申请留学生创业基金

留信网认证的作用:

1:该专业认证可证明留学生真实身份

2:同时对留学生所学专业登记给予评定

3:国家专业人才认证中心颁发入库证书

4:这个认证书并且可以归档倒地方

5:凡事获得留信网入网的信息将会逐步更新到个人身份内,将在公安局网内查询个人身份证信息后,同步读取人才网入库信息

6:个人职称评审加20分

7:个人信誉贷款加10分

8:在国家人才网主办的国家网络招聘大会中纳入资料,供国家高端企业选择人才

TECHNICAL TRAINING MANUAL GENERAL FAMILIARIZATION COURSE

AIRCRAFT GENERAL

The Single Aisle is the most advanced family aircraft in service today, with fly-by-wire flight controls.

The A318, A319, A320 and A321 are twin-engine subsonic medium range aircraft.

The family offers a choice of engines

Recently uploaded (20)

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

AKS UNIVERSITY Satna Final Year Project By OM Hardaha.pdf

Design and Analysis of Algorithms-DP,Backtracking,Graphs,B&B

Design and Analysis of Algorithms-DP,Backtracking,Graphs,B&B

Water Industry Process Automation and Control Monthly - May 2024.pdf

Water Industry Process Automation and Control Monthly - May 2024.pdf

Student information management system project report ii.pdf

Student information management system project report ii.pdf

MCQ Soil mechanics questions (Soil shear strength).pdf

MCQ Soil mechanics questions (Soil shear strength).pdf

block diagram and signal flow graph representation

block diagram and signal flow graph representation

Quality defects in TMT Bars, Possible causes and Potential Solutions.

Quality defects in TMT Bars, Possible causes and Potential Solutions.

Planning Of Procurement o different goods and services

Planning Of Procurement o different goods and services

Vaccine management system project report documentation..pdf

Vaccine management system project report documentation..pdf

TECHNICAL TRAINING MANUAL GENERAL FAMILIARIZATION COURSE

TECHNICAL TRAINING MANUAL GENERAL FAMILIARIZATION COURSE

General/Digital up conversion

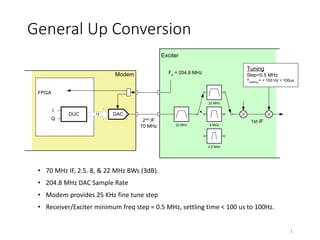

- 1. General Up Conversion • 70 MHz IF, 2.5. 8, & 22 MHz BWs (3dB). • 204.8 MHz DAC Sample Rate • Modem provides 25 KHz fine tune step • Receiver/Exciter minimum freq step = 0.5 MHz, settling time < 100 us to 100Hz. 1 Modem FPGA DAC14DUC Fs = 204.8 MHz I Q 2nd IF 70 MHz Exciter Tuning Step=0.5 MHz Tsettling = < 100 Hz < 100us 22 MHz 8 MHz 2.5 MHz 22 MHz 1st IF

- 2. Digital Up Converter • Baseband samples are converted to 70 MHz “digital IF” • Polyphase filter approach reduces required 204.8 Msps processing to simple data transfer. 2 18.8 MHz + 51.2 MHz = 70 MHz 14 x2 Interpolation DAC 2 1 sinc x2 Interpolation NCO sincos 2 1 sinc + - + + Complex MixerDAC Comp Fine Tune 18.8 MHz ± 250 KHz 25 KHz step Poly Phase FIR Poly Phase FIR Commutate I & Q 204.8 MHz I Q 102.4 Msps 204.8 Msps Baseband Waveform Processing 51.2 Msps -1 -1

- 3. DUC Continued • 204.8 Msps DAC sample rate required to reduce DAC sinx/x roll-off. • Final 2x interpolation process employs parallel FIR (polyphase) filters that process at 1x rate. • Number of filter taps is reduced by factor of two resulting from quarter wave frequency shift. 3 Equivalent 2 x2 Interpolation 2 14 sin( ) n cos( ) n Fs = 204.8 Msps 40 Taps 40 Taps 14 x2 Interpolation Poly Phase FIR Poly Phase FIR -1 Commutate I & Q Fs = 102.4 Msps Fs = 204.8 Msps -1 20 Taps 20 Taps

- 4. DUC Filters 4 14 x2 Interpolation DAC 2 x2 Interpolation NCO sincos 2 + - + + Complex Mixer Commutate I & Q 204.8 MHz I Q DUC Filter 1 Programmable FIR 47 Taps each DUC Filter 2 20 Taps each -1 -1

- 5. DUC Filter 1• 47 tap programmable FIR, 16 bit symmetric coefficients • BW is adjusted according to waveform mode, I.e., 20, 6, or 1 MHz modes. • Three sets of coefficients must be stored. The proper set of coefficients are downloaded upon change in waveform BW. 5

- 6. DUC Filter 2 Simplification • Original filter is split into even and odd phases and processed in parallel at 102.4Msps (half rate). • Each output is selected once per 1x sample period to provide x2 rate change. 6 2 2 Even coef Odd coef 102.4 Msps 204.8 Msps 102.4 Msps 204.8 Msps X2 Interploation X2 Interploation Even coef Odd coef Conversion I Q 40 taps 40 taps 40 taps 40 taps

- 7. DUC Filter 2 Simplification • One of two filter phases can be eliminated as a result of quarter wave frequency shift. • Number of taps is reduced by factor of two. • Real frequency mixer and quarter wave shift is reduced to simple commutation between I & q filter outputs. • Provides complex to reak conversion and fs/4 frequency shift. 7 Even coef Odd coef Even coef Odd coef -sin( ) n cos( ) n I Q ={1,0,-1,0} ={0,-1,0,1} Even coef -120 taps 20 taps -1Odd coef yi (n) -yi (n) -yq (n) yq(n) DUC Out Conversion 20 taps, each Output Sequence = { yi(n), -yq(n), -yi(n), yq(n), …}

- 8. DUC Filter 2 • 20 tap FIR, 16 bit symmetric coefficients. 8 40 taps h0 ,h2 ,h4 ,...h38 Even Coef Odd Coef h 1 ,h 3 ,h 5 ,...h 39 I Channel Q Channel 20 taps 20 taps

- 9. DUC Output After 1st Interpolation 9 14 x2 Interpolation DAC 2 x2 Interpolation 2 + - + + Complex Mixer Commutate I & Q 204.8 MHz I Q -1 -1 -120 -100 -80 -60 -40 -20 0 20 0 12.8 25.6 38.4 51.2 64 76.8 89.6 102.4 MHz dB DUC Filter1 Signal -120 -100 -80 -60 -40 -20 0 20 0 12.8 25.6 38.4 51.2 64 76.8 89.6 102.4 f/fs dB Shifted Signal

- 10. DUC Output Spectrum 10 DUC Output 20 MHz & 1 MHz Waveform Modes -120 -100 -80 -60 -40 -20 0 20 0 25.6 51.2 76.8 102.4 128 153.6 179.2 204.8 MHz dB 20 MHz 1 MHz NOTE: Analog IF Filters provide >80 dB additional rejection @ 30 MHz bandwidth.

- 11. General Down Conversion • 70 MHz IF, 2.5. 8, & 22 MHz BWs (3dB). • 102.4 MHz ADC Sample Rate • Modem provides 25 KHz fine tune step • Receiver/Exciter minimum freq step = 0.5 MHz, settling time < 100 us to 100Hz. 11 Modem FPGA 14DDC Fs = 102.4 MHz I Q 2nd IF 70 MHz Receiver 22 MHz 8 MHz 2.5 MHz 22 MHz 1st IF ADC Tuning Step=0.5 MHz Tsettling = < 100 Hz < 100us

- 12. Digital Down Converter 12 102.4 Msps51.2 Msps 12 ADC 102.4 MHz sincos NCO 47 tap FIR 47 tap FIR 2 2 I/Q FFT / PSAM Freq Error Tune Freq Freq Constant Digital Down Converter Sync Timing/Freq Timing/FreqError Baseband Waveform Processing

- 14. DDC / DUC Commonality • The DDC filter (47 tap) and DUC filter #1 are the same. The DDC and DUC can share the same FPGA filter structures. • The DDC and DUC share a single DDS FPGA instantiation. 14

- 15. DDC / DUC Commonality 15 14 DAC 2 2 + - + + 204.8 MHz I Q -1 -1 12 ADC 102.4 MHz -sin cos NCO 47 tap FIR 47 tap FIRI/Q Freq Constant Digital Down Converter Freq Error Tune Freq 2 2 Sync Timing/Freq Digital Up Converter I Q 47 tap FIR 47 tap FIR 20 tap FIR 20 tap FIR Common Filter. I/Q filter pair is instantiated once in FPGA and shared between DDC and DUC. Common NCO/DDS Shared between DUC and DDC.

- 16. Direct Digital Synthesizer (DDS) • DDS is implemented using Xilinx ip with Taylor series phase correction. • SFDR -115 dB • Df < 1 Hz • Phase Accumulator = 32 bits • cos & -sin outputs = 20 bits 16

- 17. Direct Digital Synthesizer (DDS) • Output frequency is a combination of a constant frequency term, tune frequency term, and error frequency term. 17 MHzf KHzfKHz KHzfKHz where f f fMHzf ffMHzf clk error tune clk out tuneout errortuneout 4.102 1111 sizestep25KHz,250250 : 2 8.18:CaseDUC 4.32:CaseDDC 32 D

- 18. Frequency Uncertainty/Error • Specifications • Reference Frequency = +/- 1 ppm • Max Doppler Velocity = 700 m/s 18 Hz HzMHz sme sm f c v HzMHzppm 833,10yUncertaintFrequencyTotal 58332500 /83 /700 ErrorDopplerMax 500022500*1ErrorReference

- 19. Frequency Correction Rx Packet • Frequency Error is determined during Synchronization process and applied prior to demodulating Rx packet. (See timing charts.) Tx Packet • Frequency error term = 0 for Tx slots. 19

- 20. DDC/DUC Processing • Maintain 16 bits in/out of DDC and DUC. • Complex mixer functions should maintain 18 bits at input and truncate to 16 bits at output. 20 DDS (NCO) 20 bits 18 bitscos -sin 20 bits Truncate 18 bits16 bits Filter/ Decimate 16 bits Baseband Processing DDC I or Q From ADC