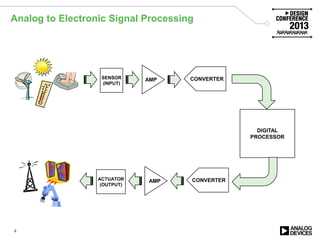

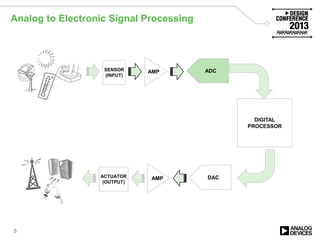

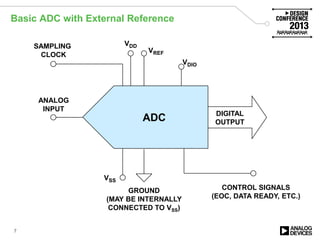

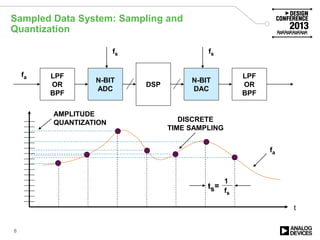

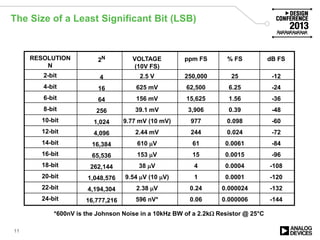

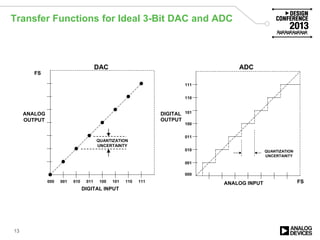

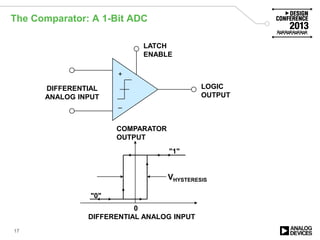

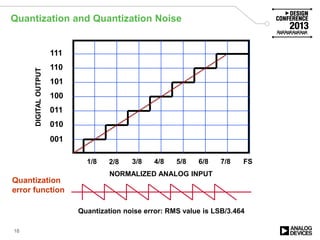

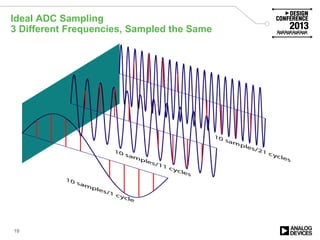

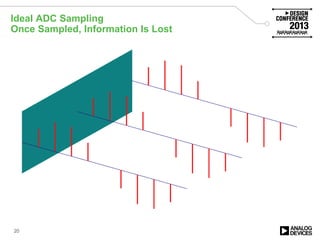

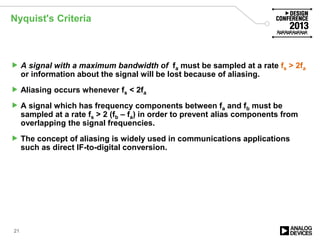

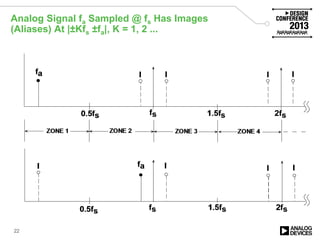

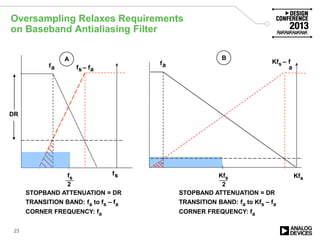

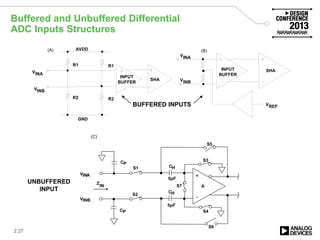

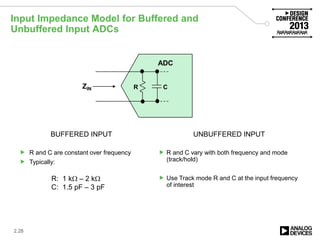

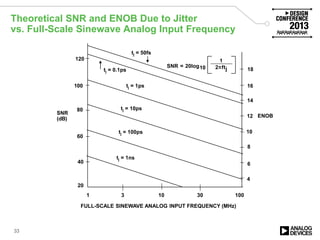

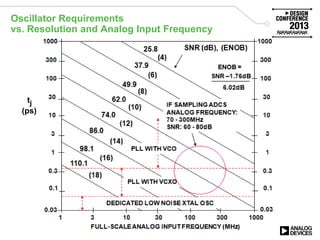

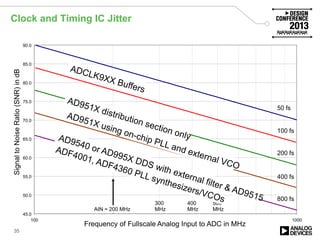

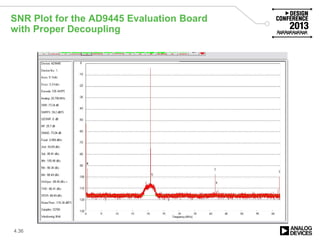

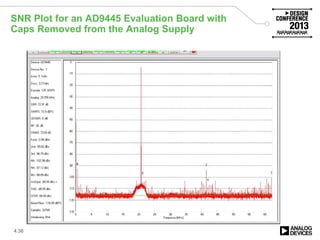

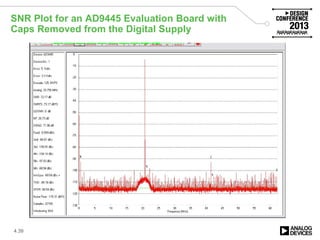

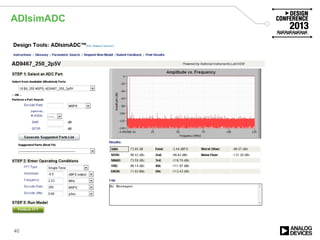

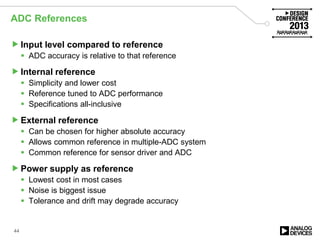

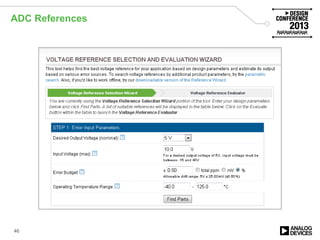

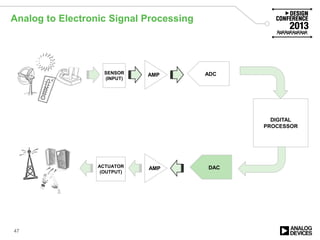

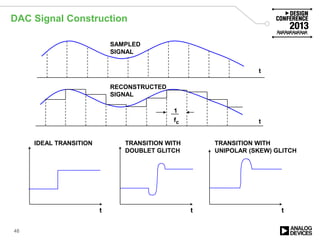

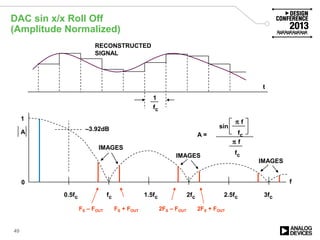

The document discusses advanced techniques for data converters in signal processing, focusing on elements like analog-to-digital converters (ADCs) and digital-to-analog converters (DACs). It outlines the advantages of digitizing analog signals, challenges related to cost and complexity, and the importance of various performance metrics such as signal-to-noise ratio and effective number of bits. It also emphasizes the relevance of differential inputs in improving signal integrity and reducing distortion in data conversion processes.