The document discusses using frequency planning to eliminate spurious signals from a PLL (Phase Locked Loop) and VCO (Voltage Controlled Oscillator). It describes:

- Integer boundary spurs that occur at integer multiples of the Phase Frequency Detector (PFD) frequency and are stronger near integer boundaries.

- How varying the PFD comparison frequency by changing the reference frequency or reference divider can change where integer boundary spurs occur, allowing frequencies furthest from the desired signal to be avoided.

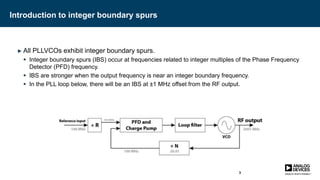

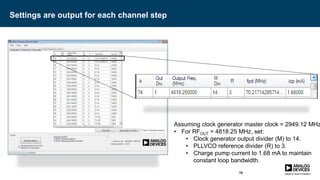

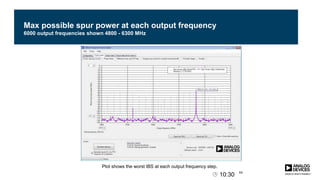

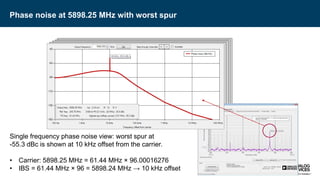

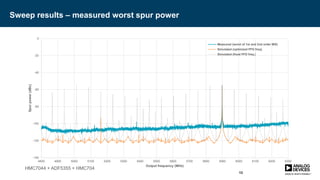

- ADIsimFrequencyPlanner, a tool that simulates spur powers over an output frequency range and selects the optimum PFD frequency at each step to minimize spurs.

![How to vary the PFD frequency

► Option 1: Programmable reference source (clock

distribution chip with programmable output dividers)

► Option 2: PLLVCO in integer mode (no integer

boundary spurs)

7

• Varying the R divider

fREF = 491.52 MHz

fPFD =

[98.304,

81.92,

70.217,

61.44,

54.613] MHz](https://image.slidesharecdn.com/ims2016microappsrobertbrennanpllfrequencyplanningv2-160808190320/85/Ims2016-micro-apps_robertbrennan_pll_frequencyplanning_v2-7-320.jpg)

![Cascaded mode – range of reference frequencies

► fPFD_1 = 61.44 MHz

► fREF_2 = [251.904, 253.44, 256, 258.048, 261.12, 264.192, 266.24, 268.8, 270.336, 276.48,

282.624, 284.16, 286.72, 288.768, 291.84, 294.912, 296.96, 299.52, 307.2, 314.88, 317.44,

322.56, 327.68, 330.24, 337.92, 345.6, 348.16] MHz

26](https://image.slidesharecdn.com/ims2016microappsrobertbrennanpllfrequencyplanningv2-160808190320/85/Ims2016-micro-apps_robertbrennan_pll_frequencyplanning_v2-26-320.jpg)