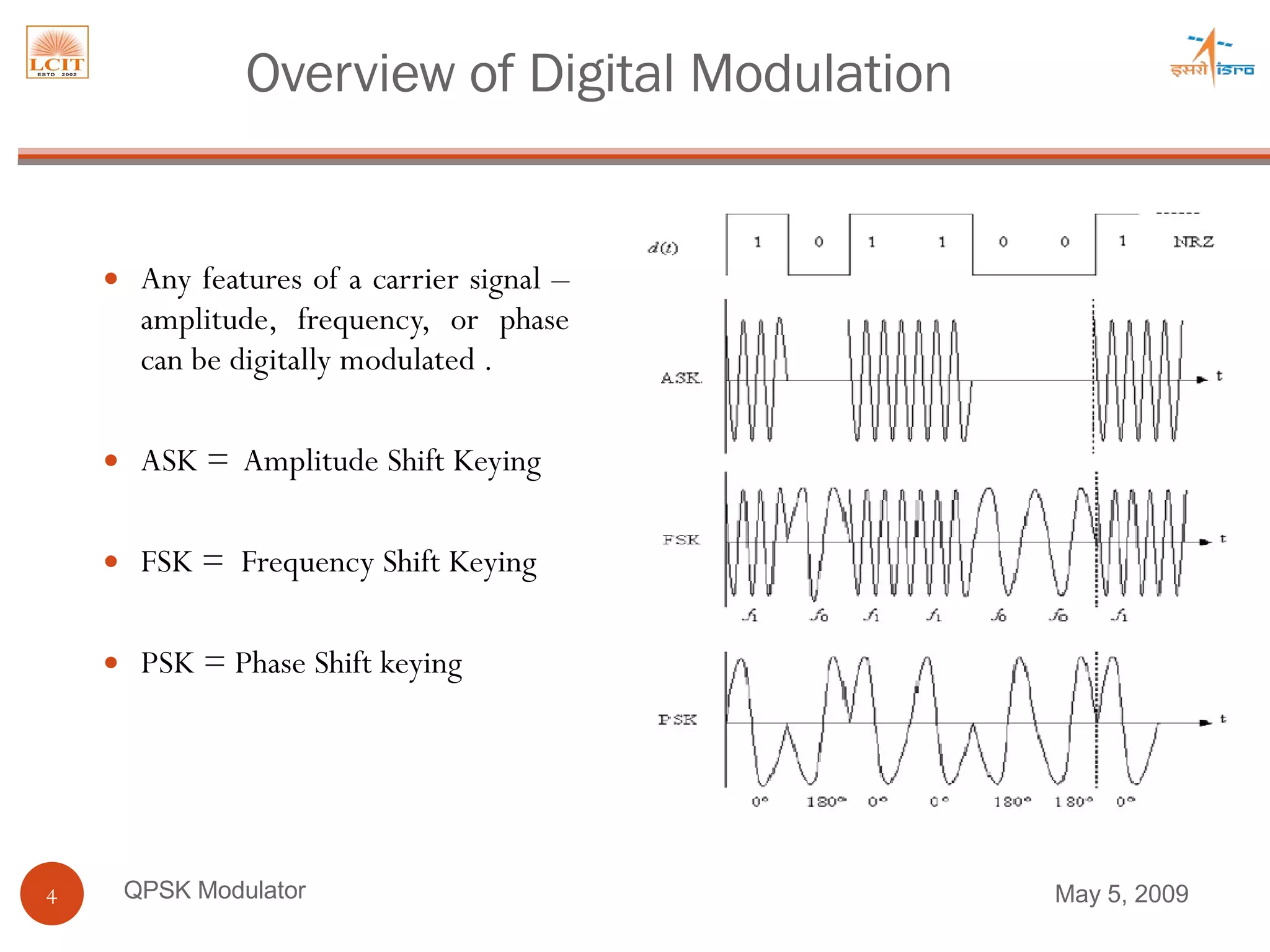

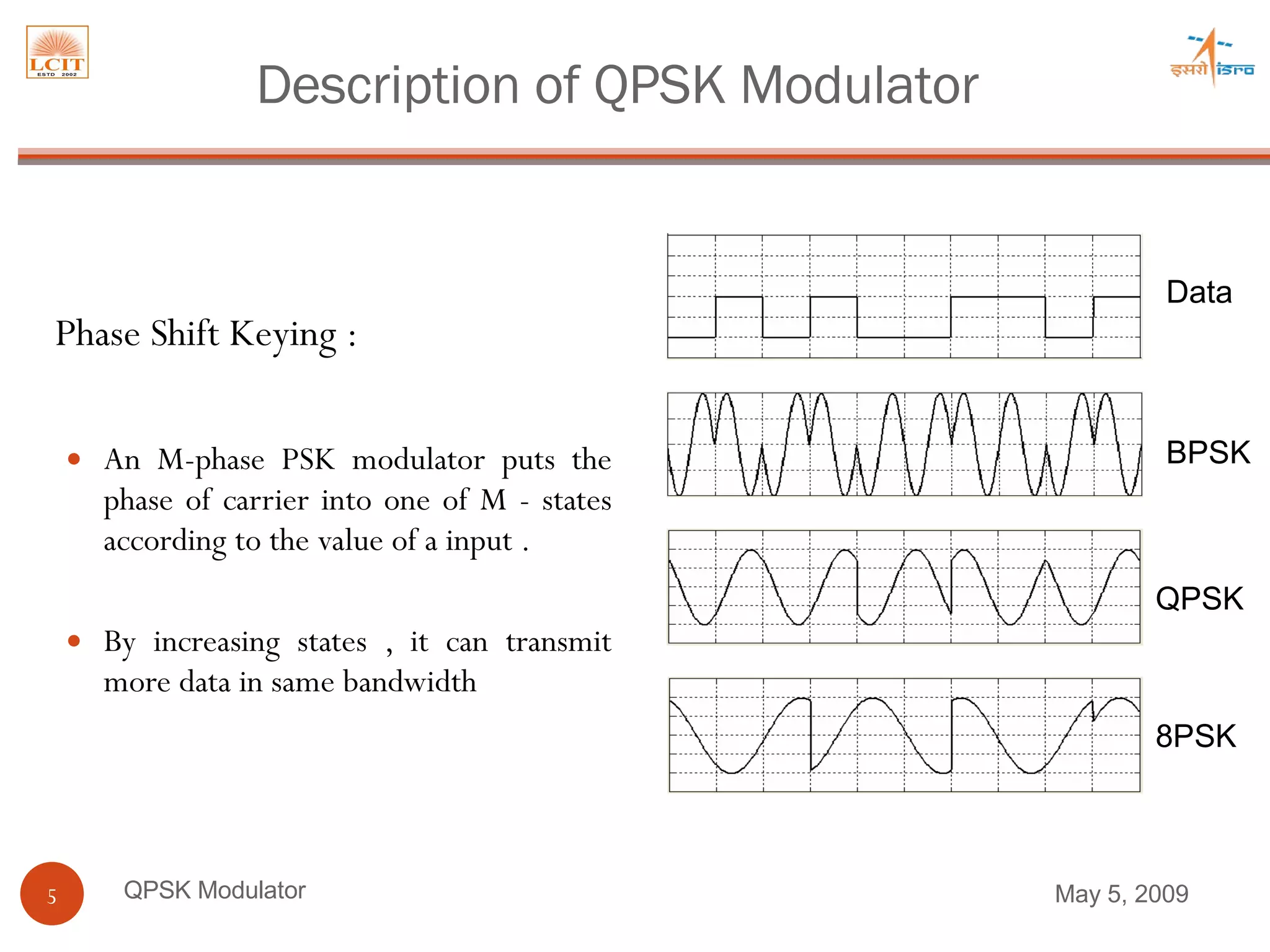

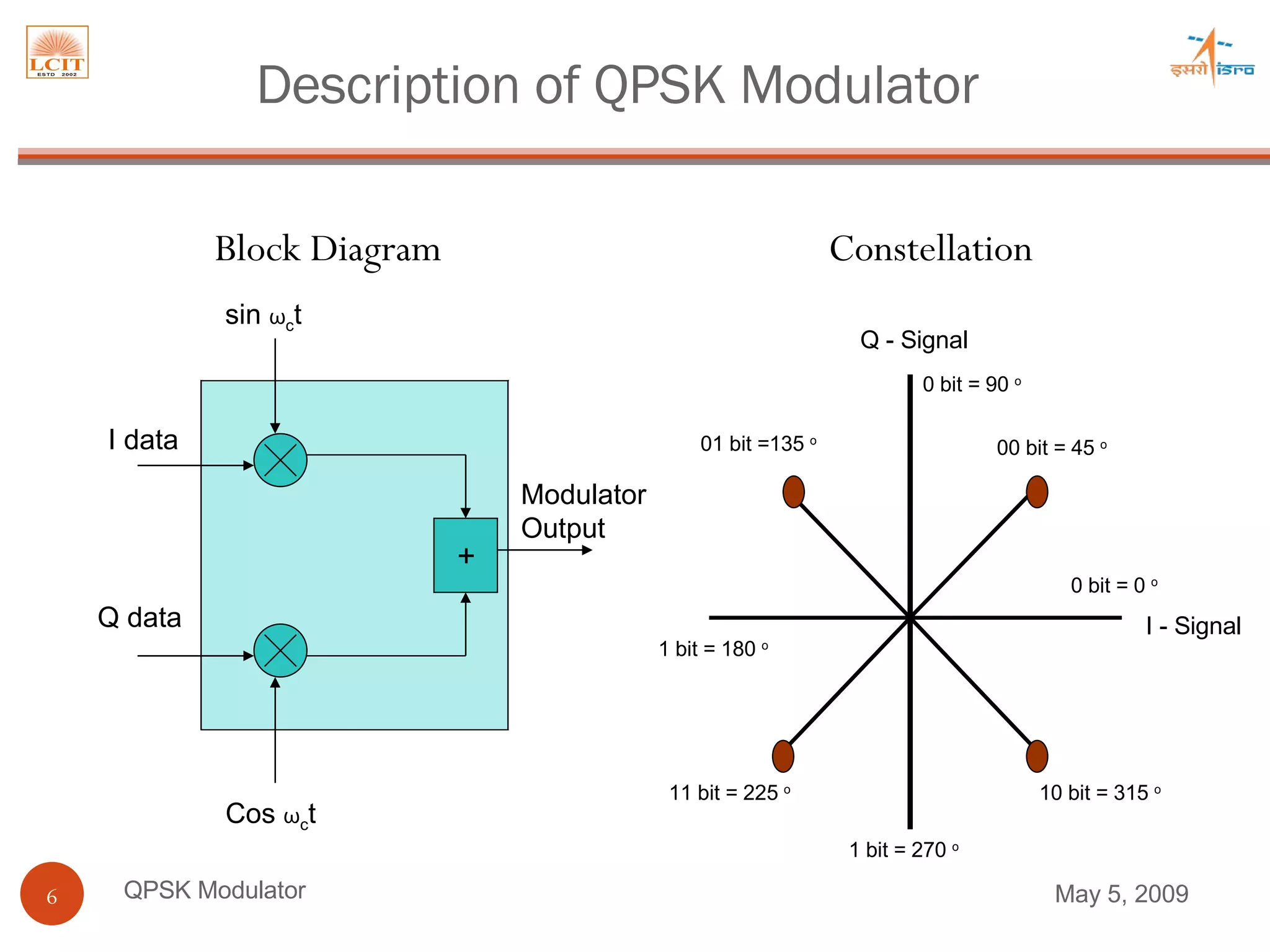

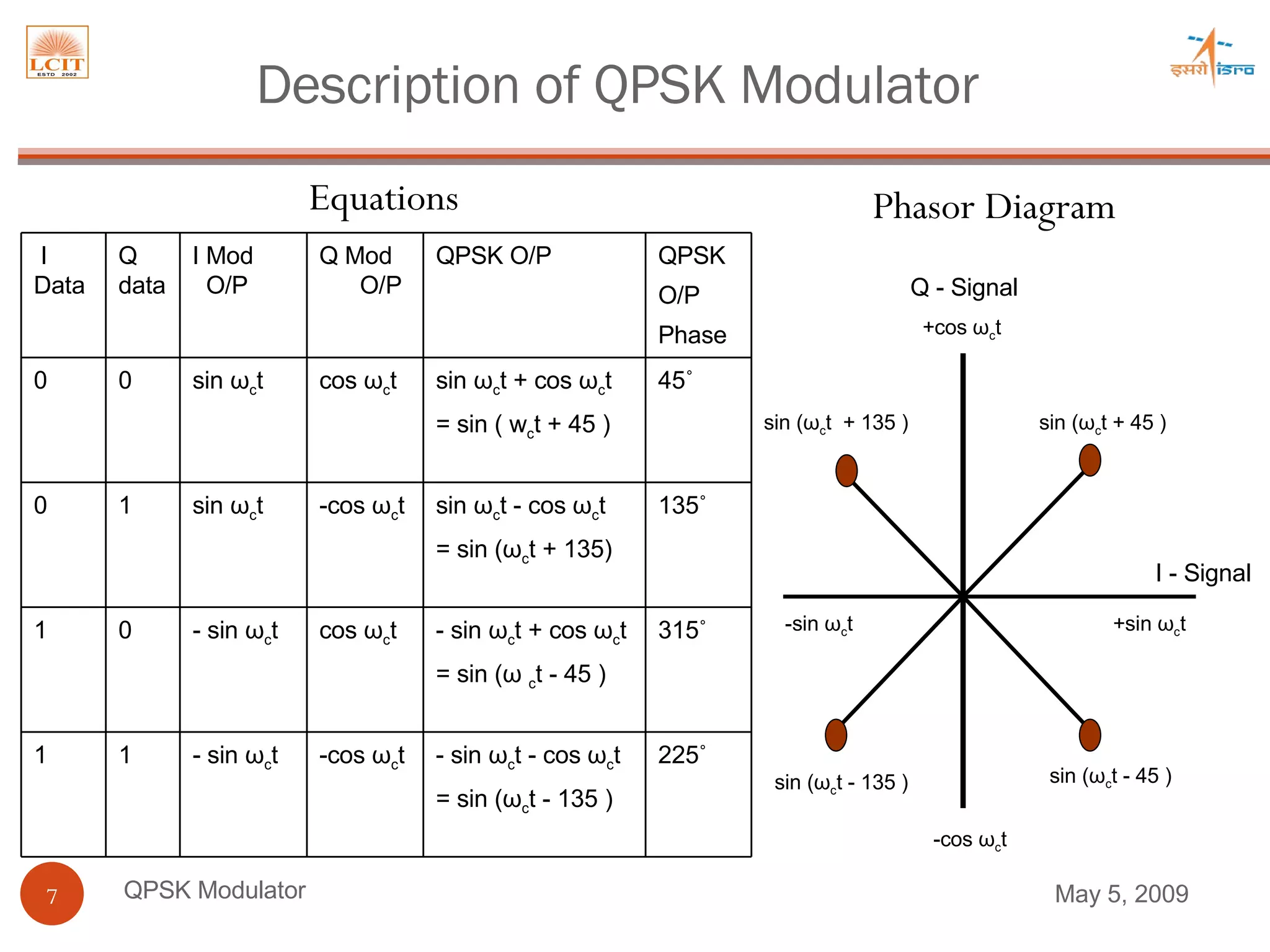

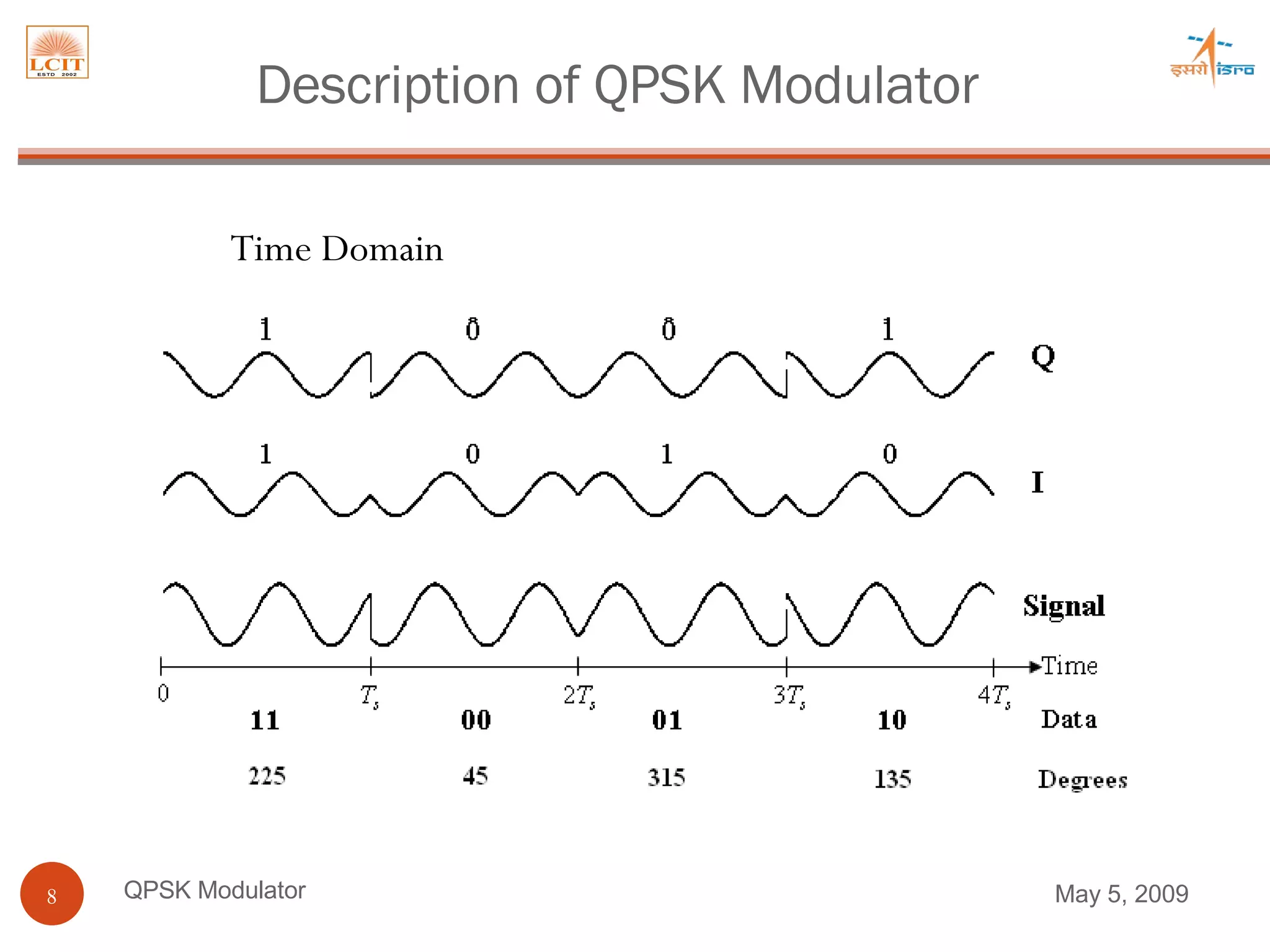

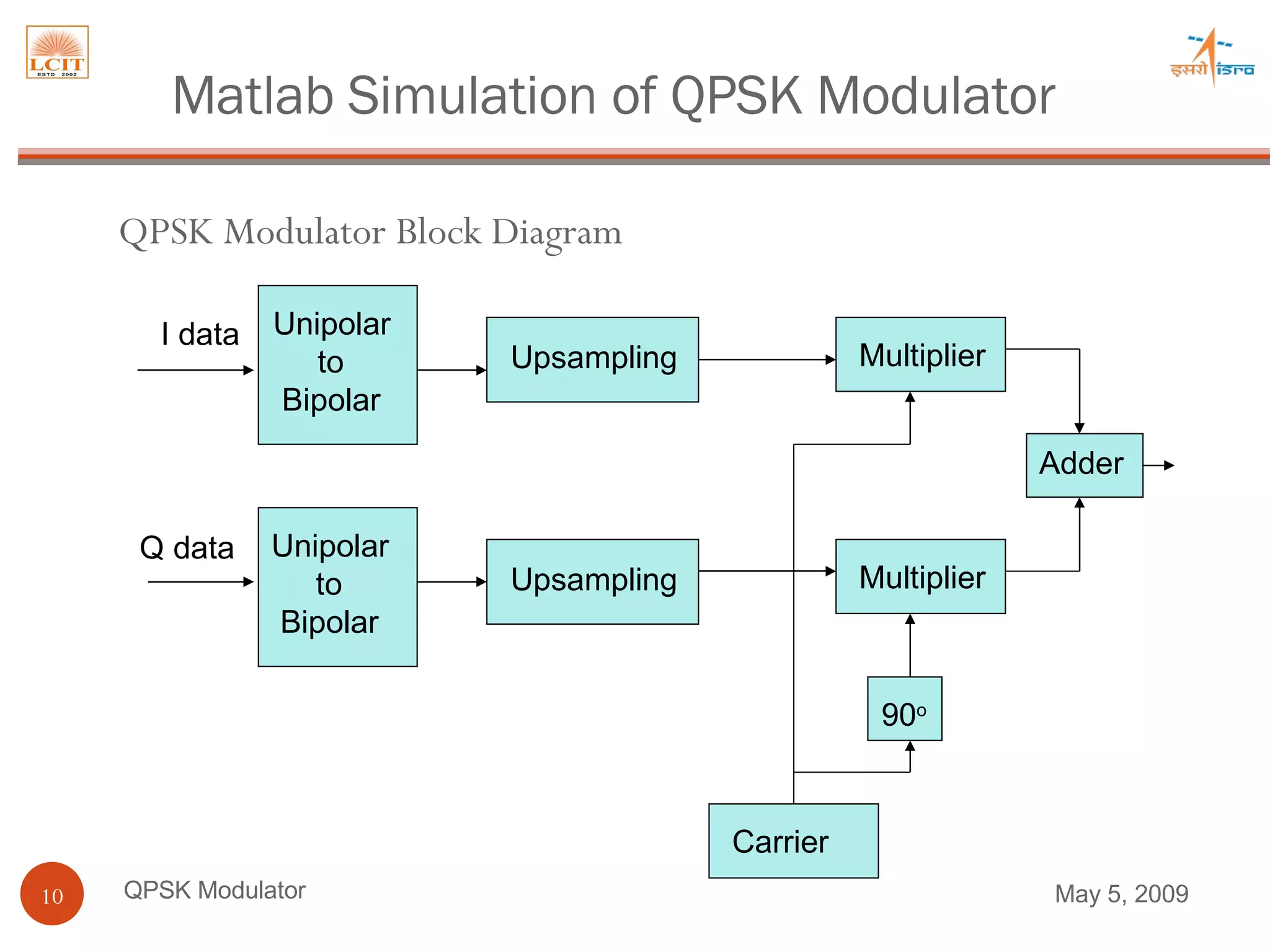

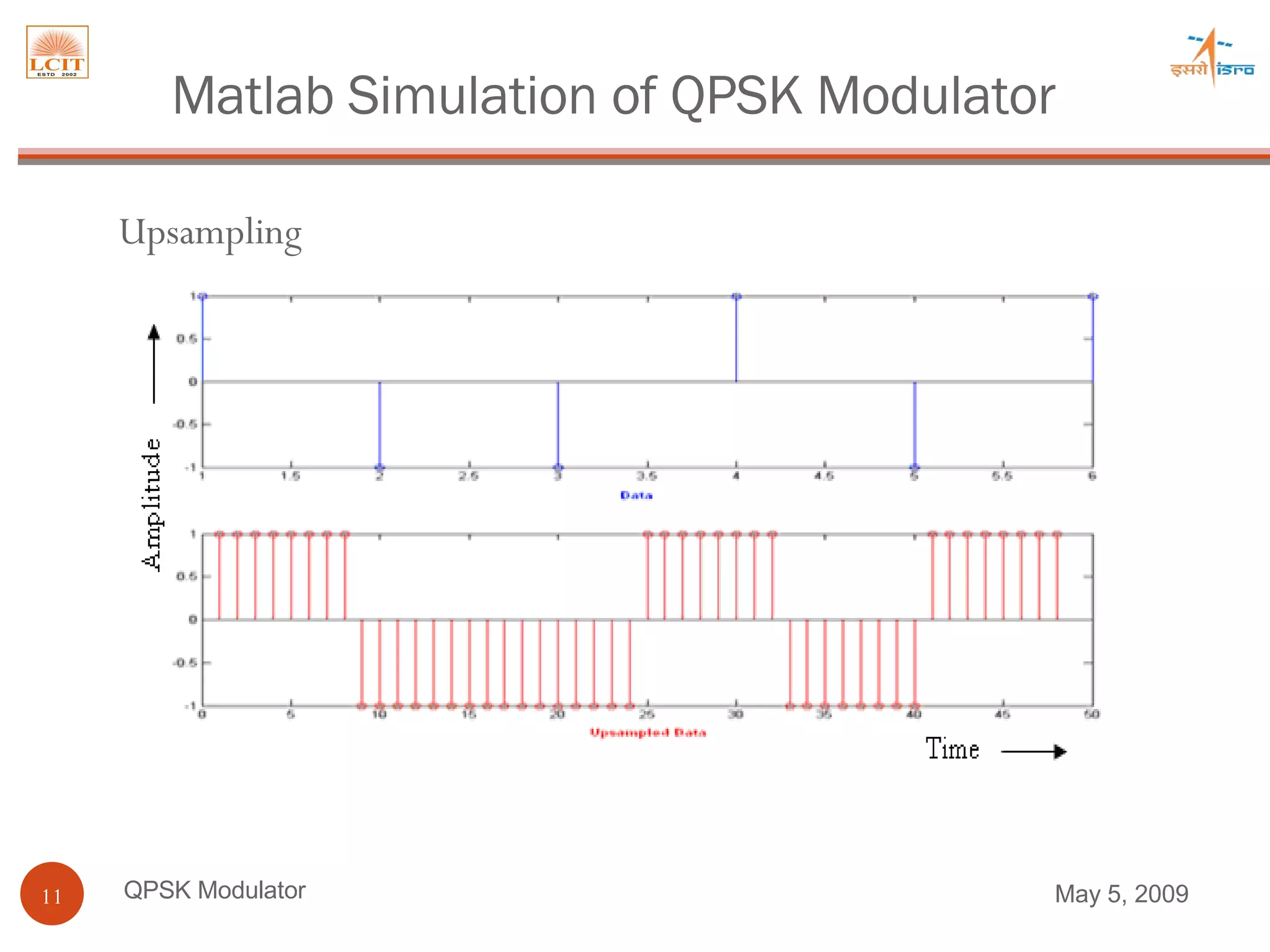

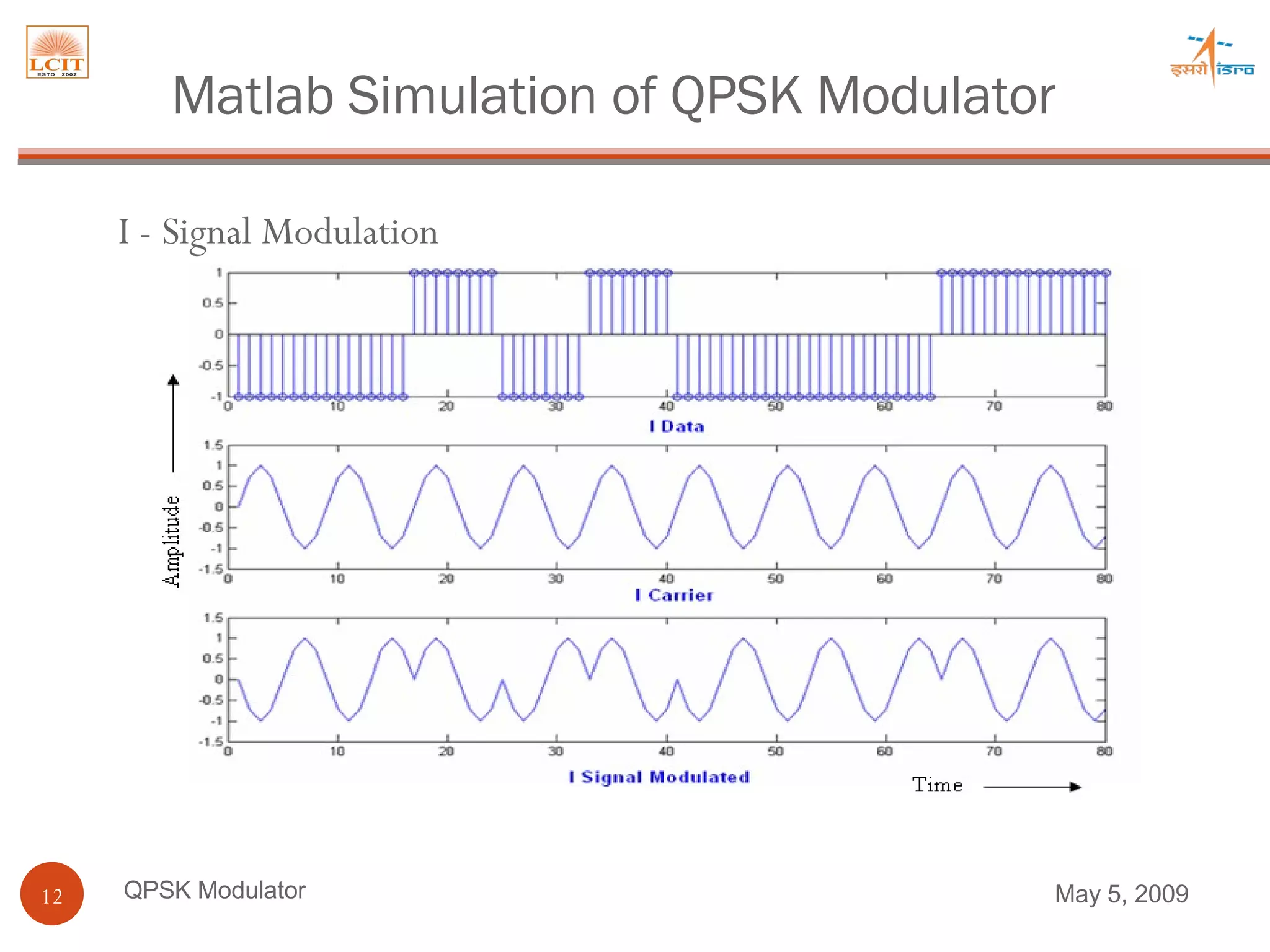

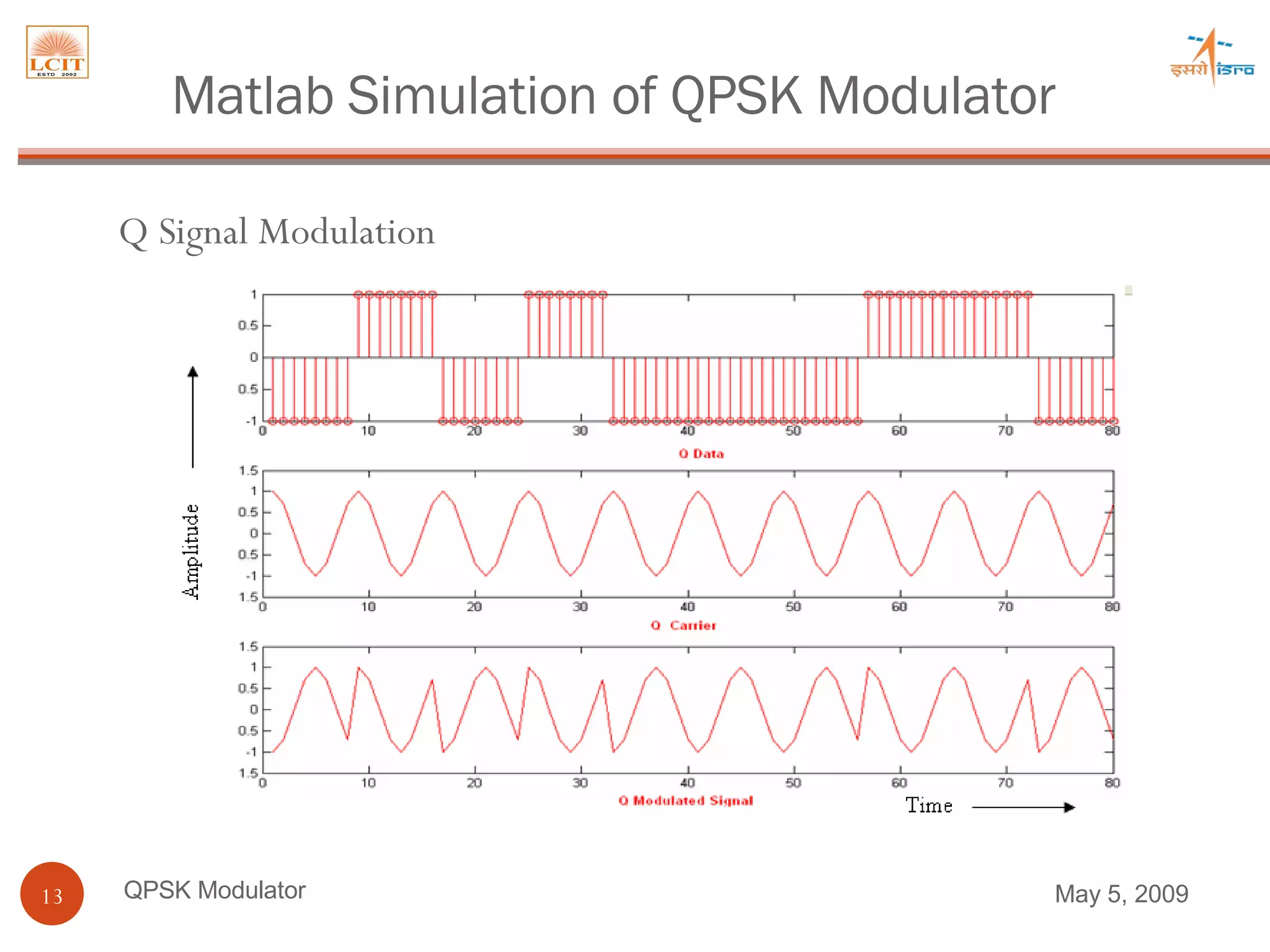

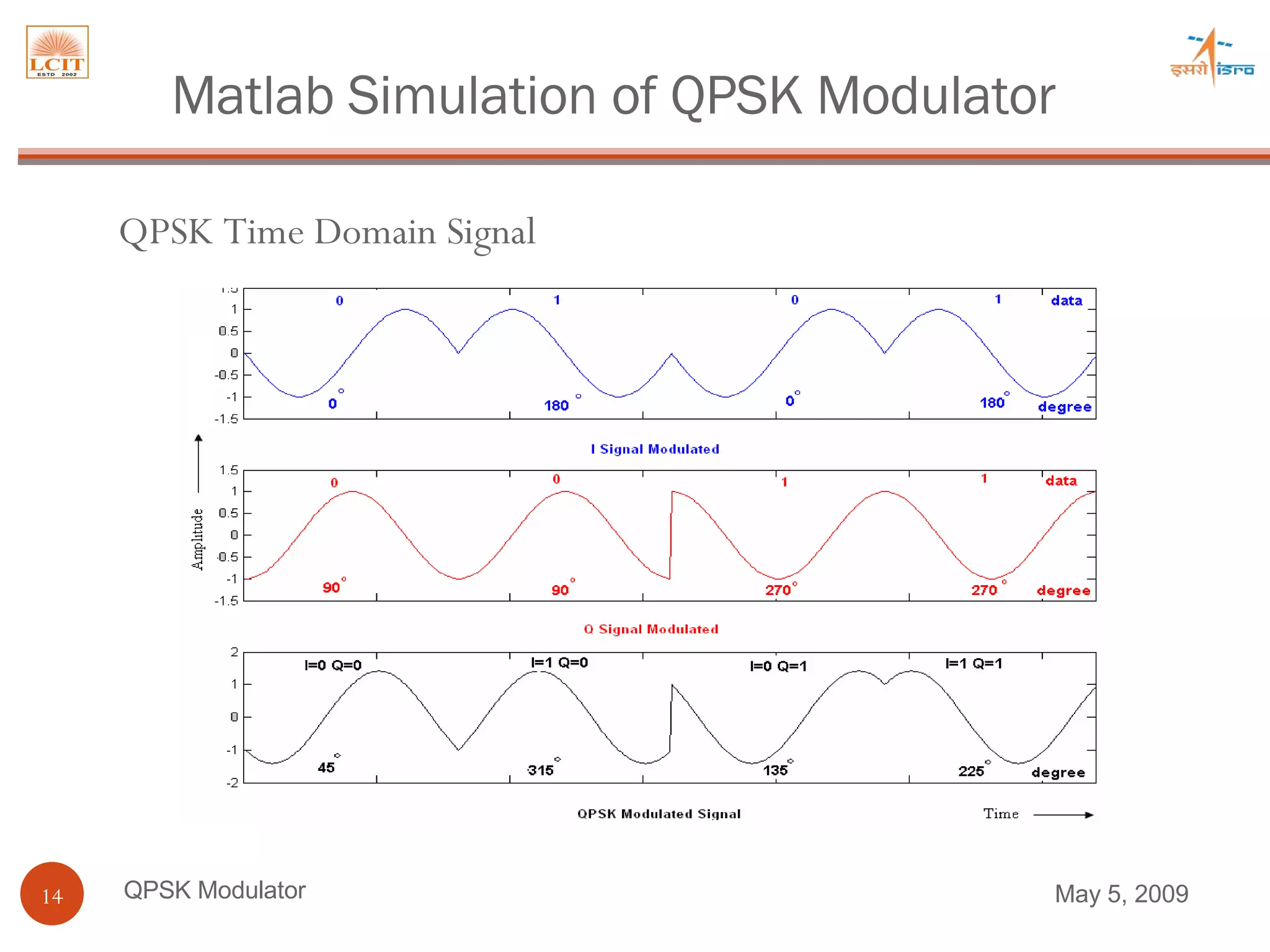

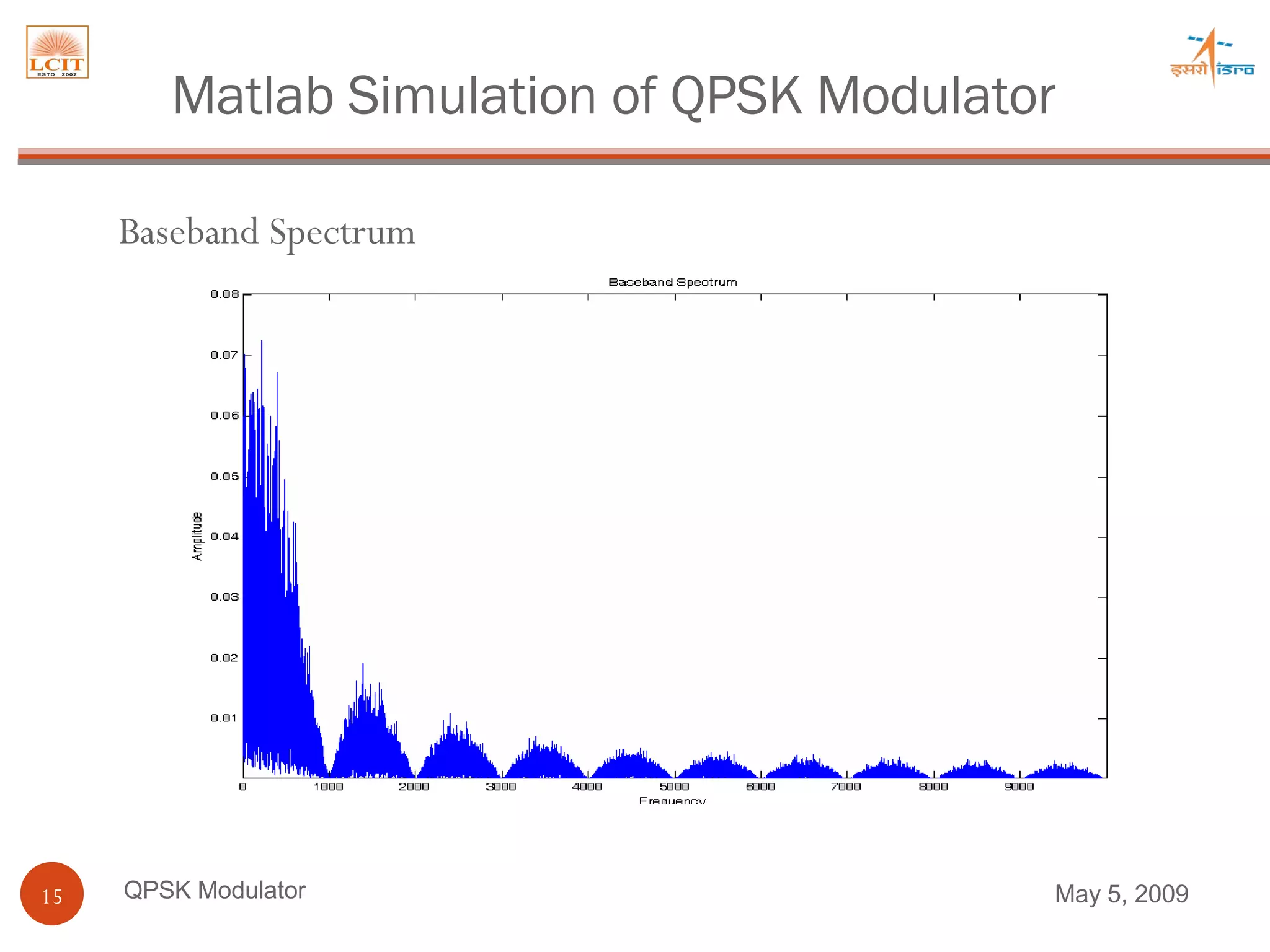

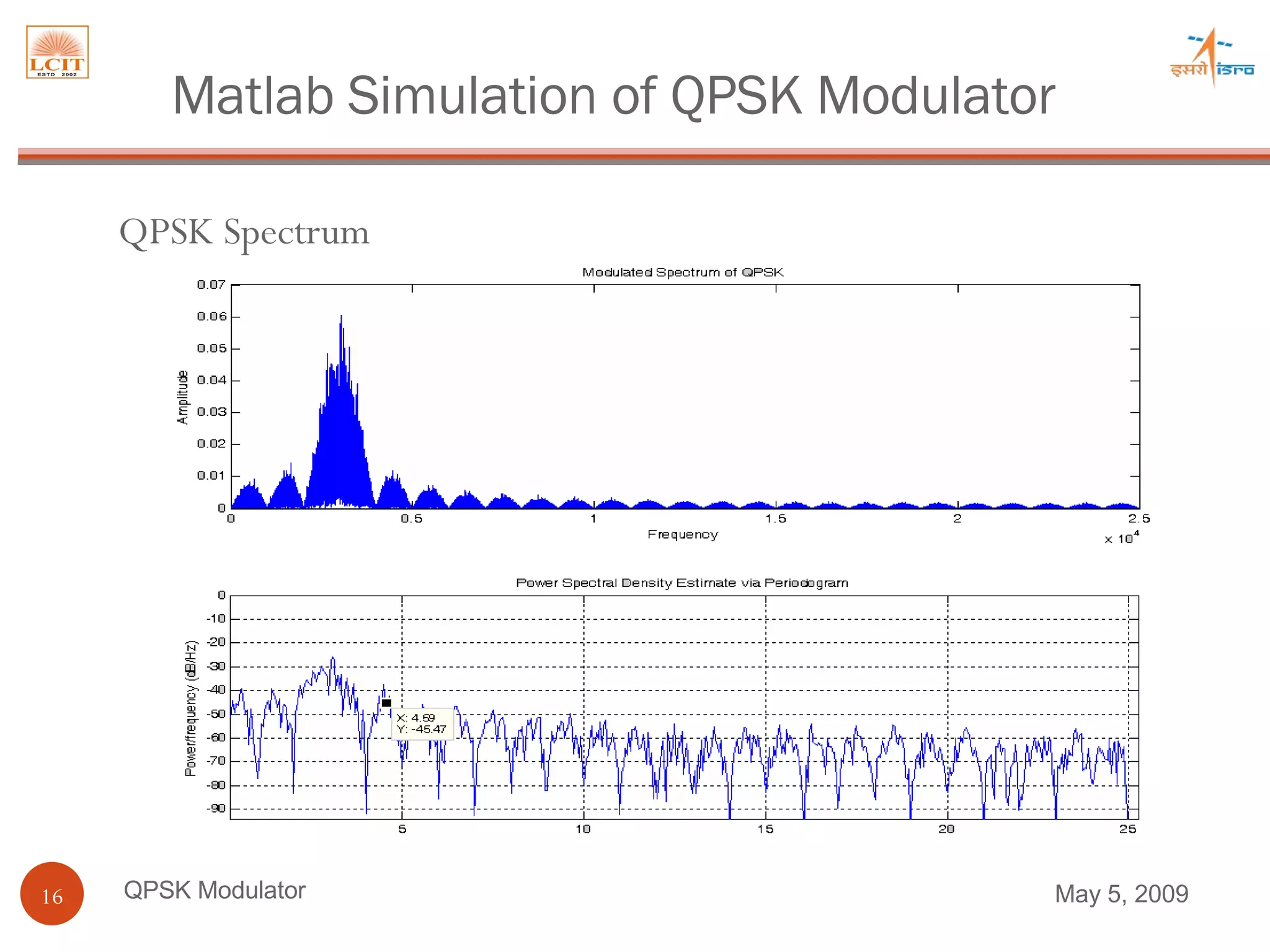

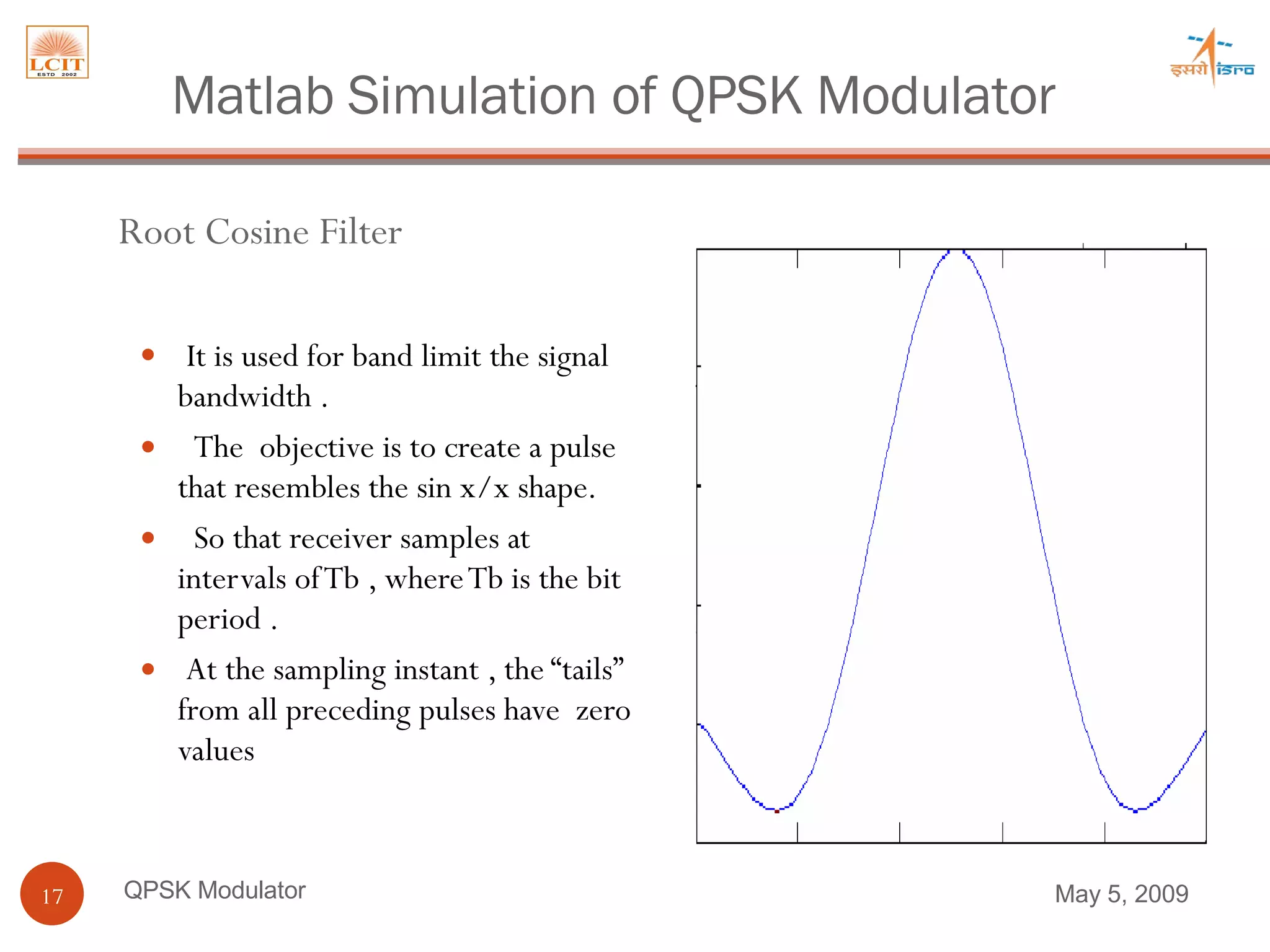

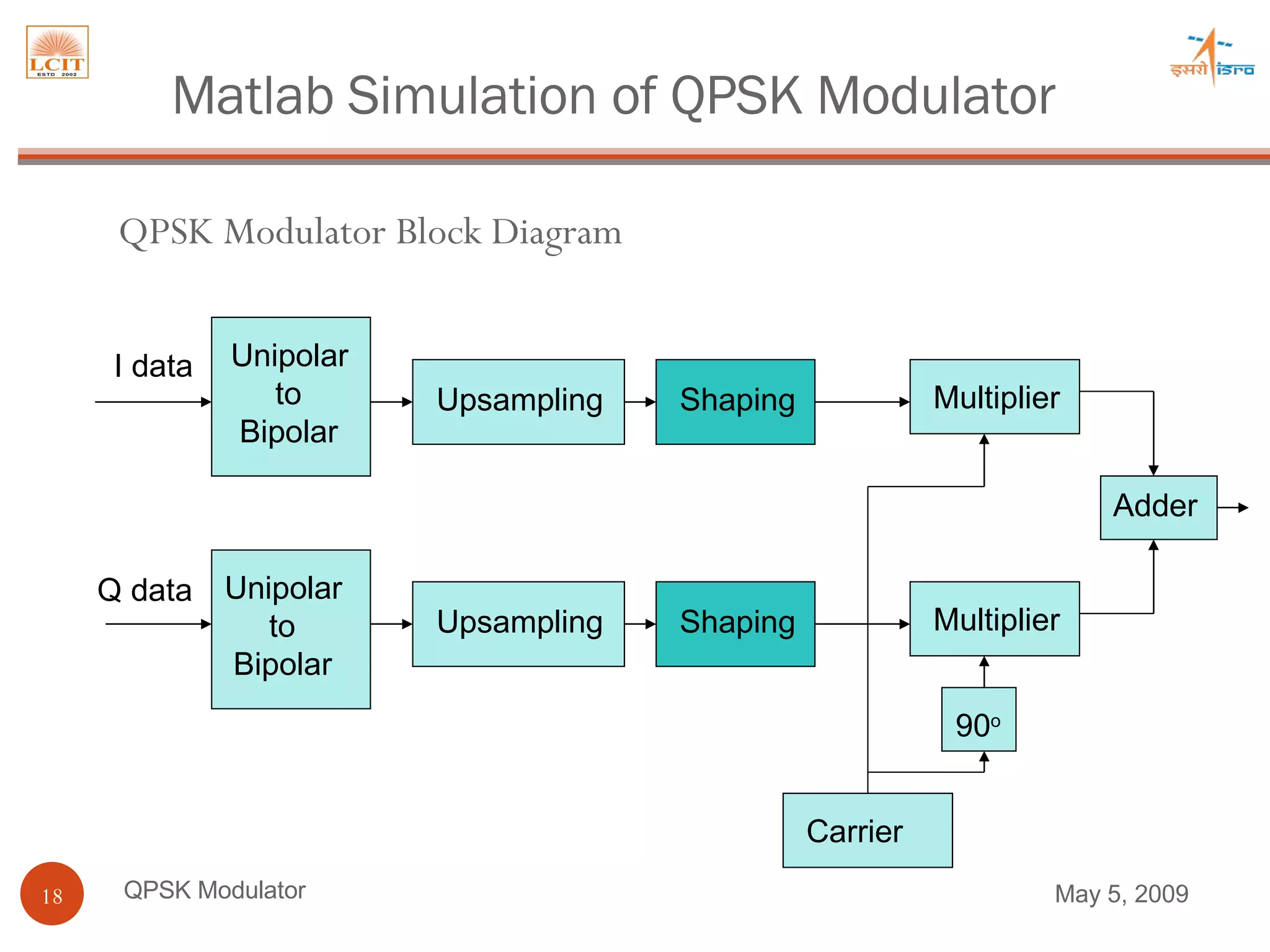

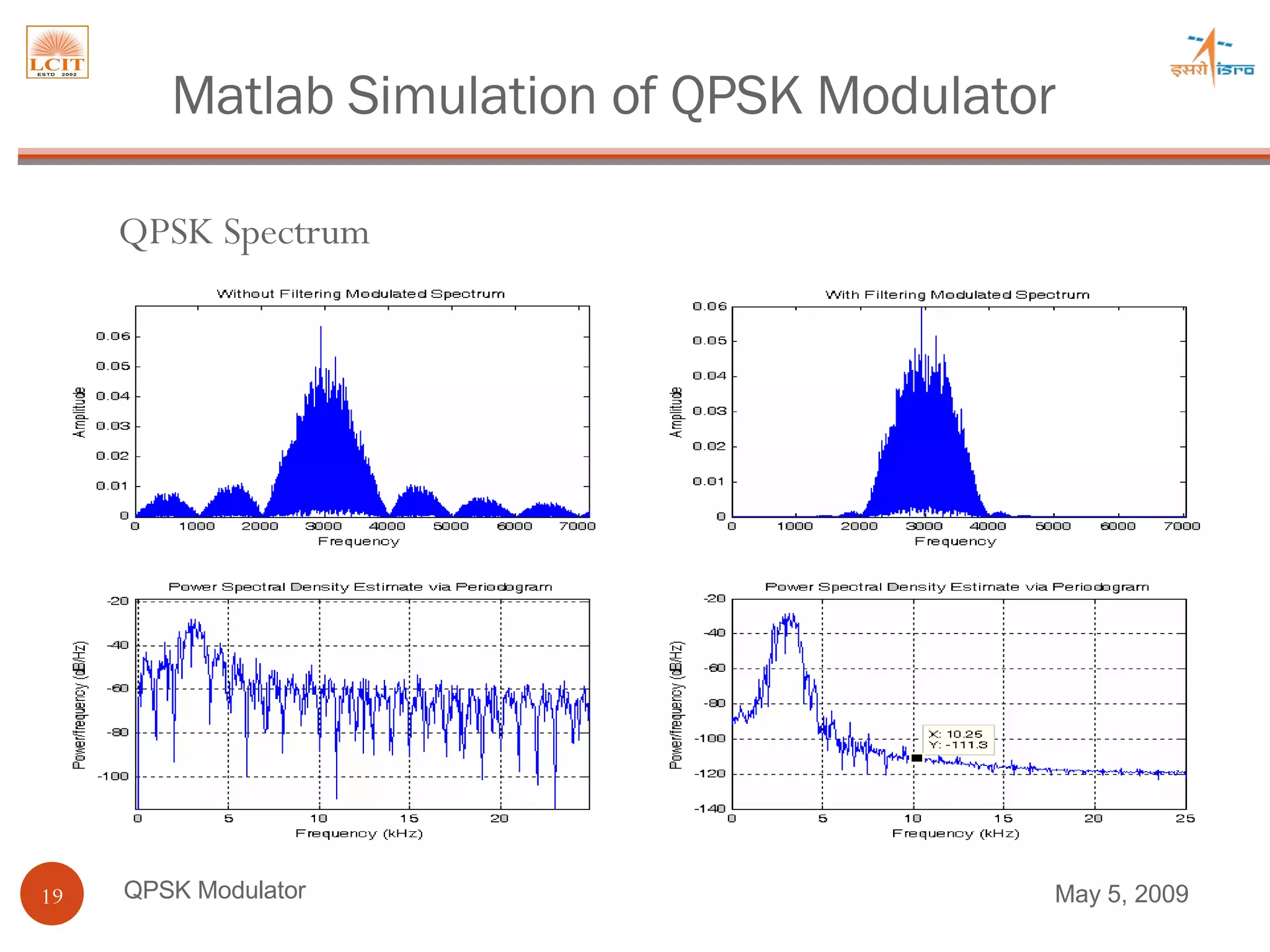

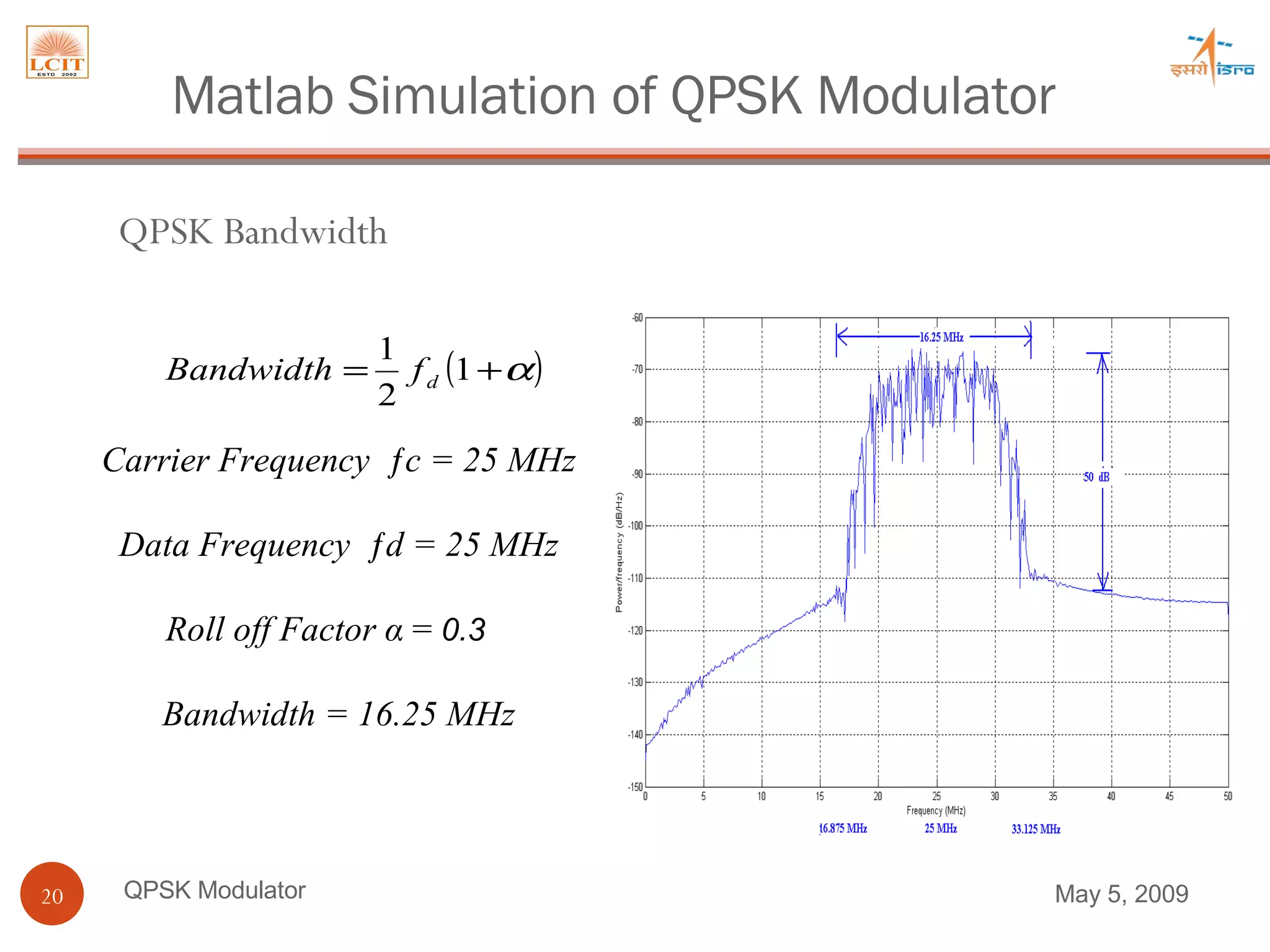

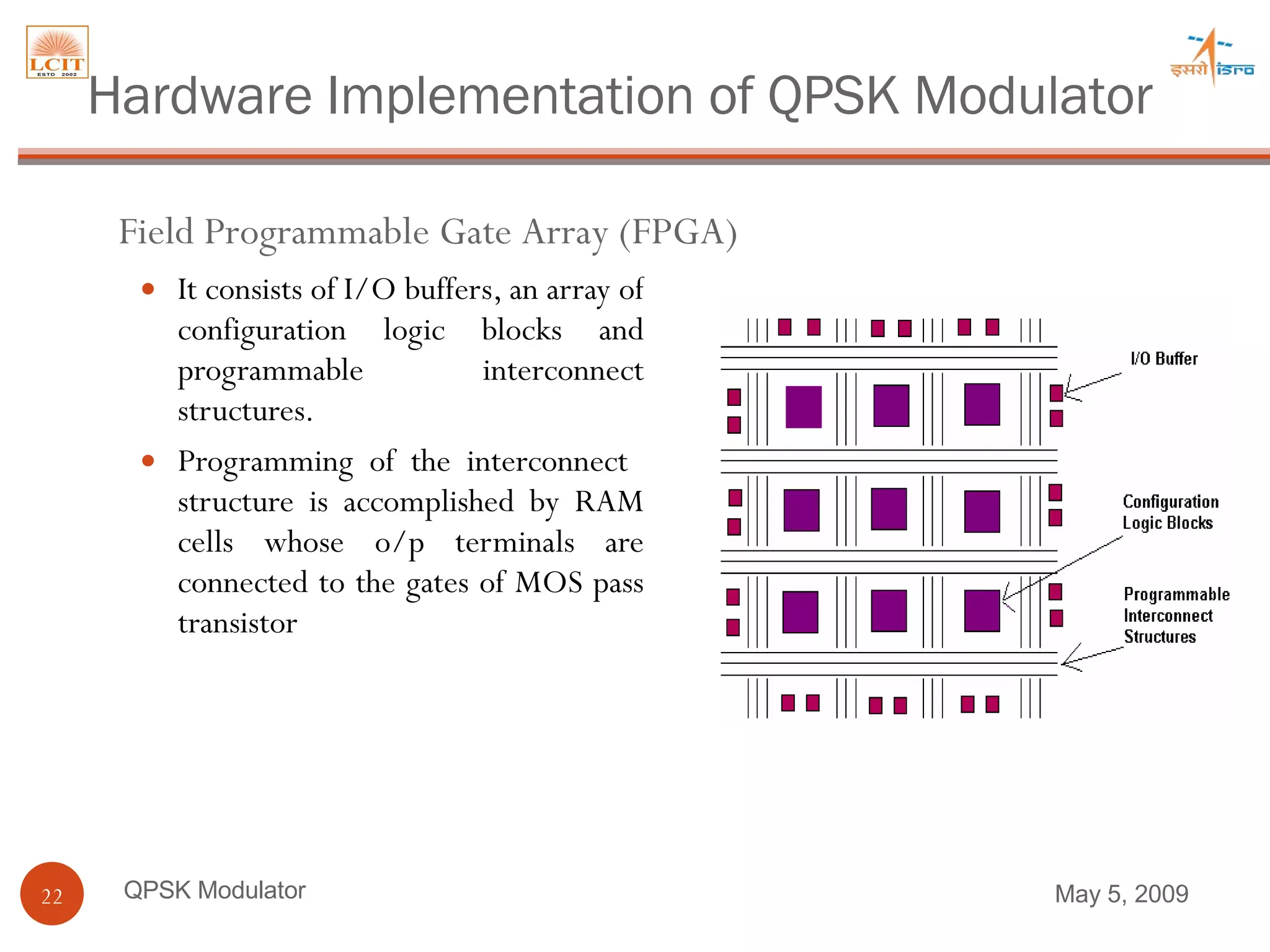

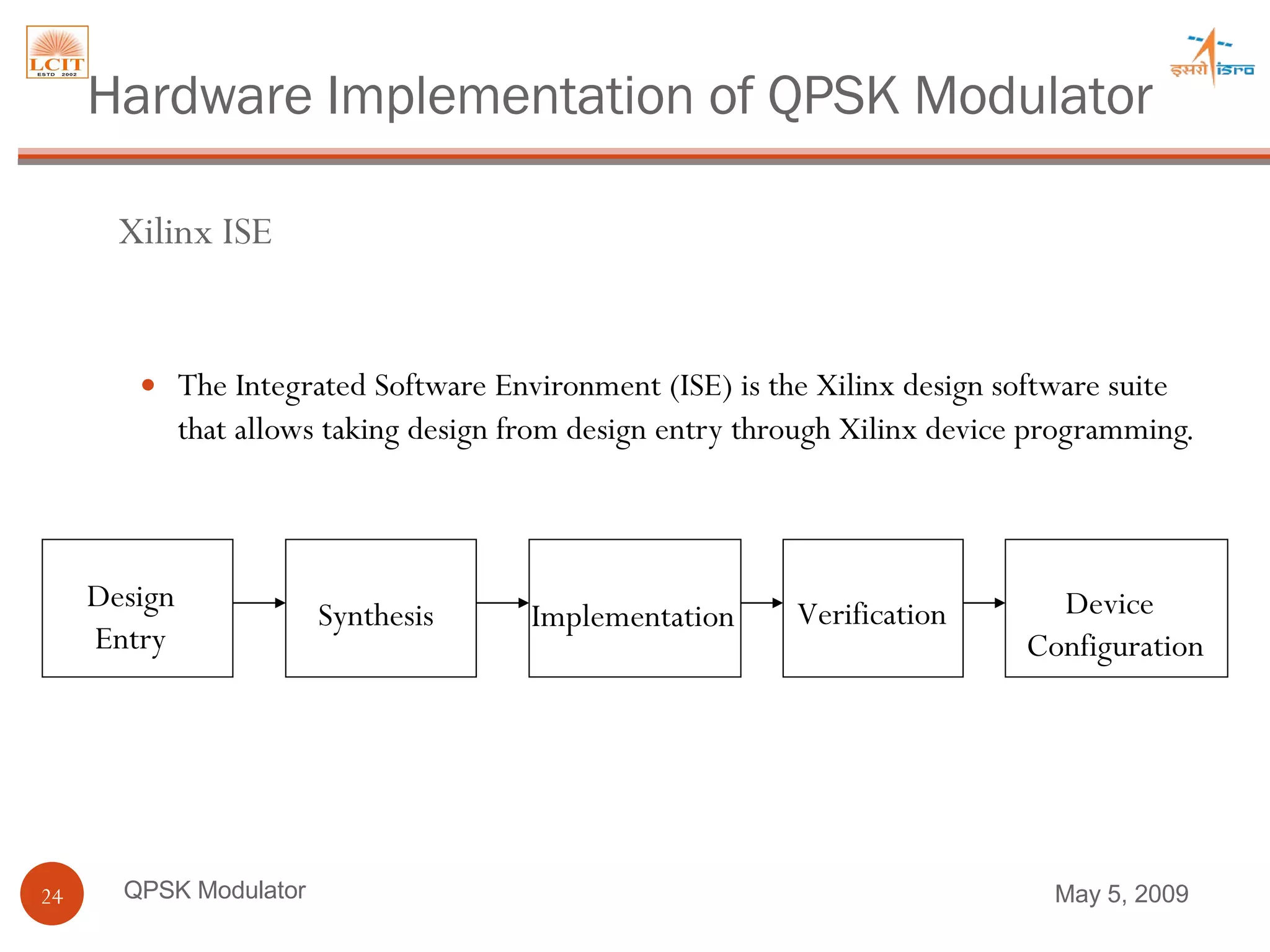

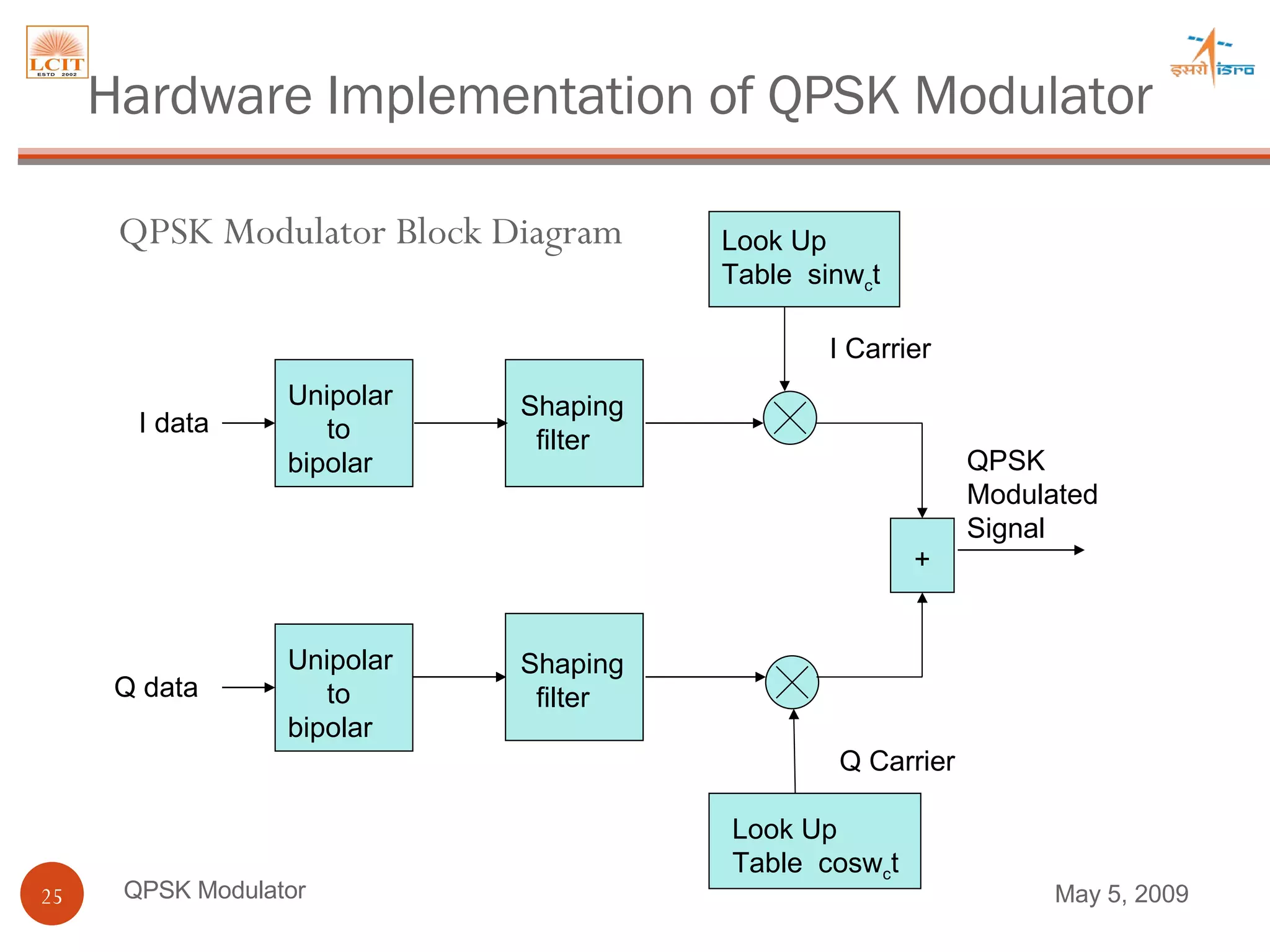

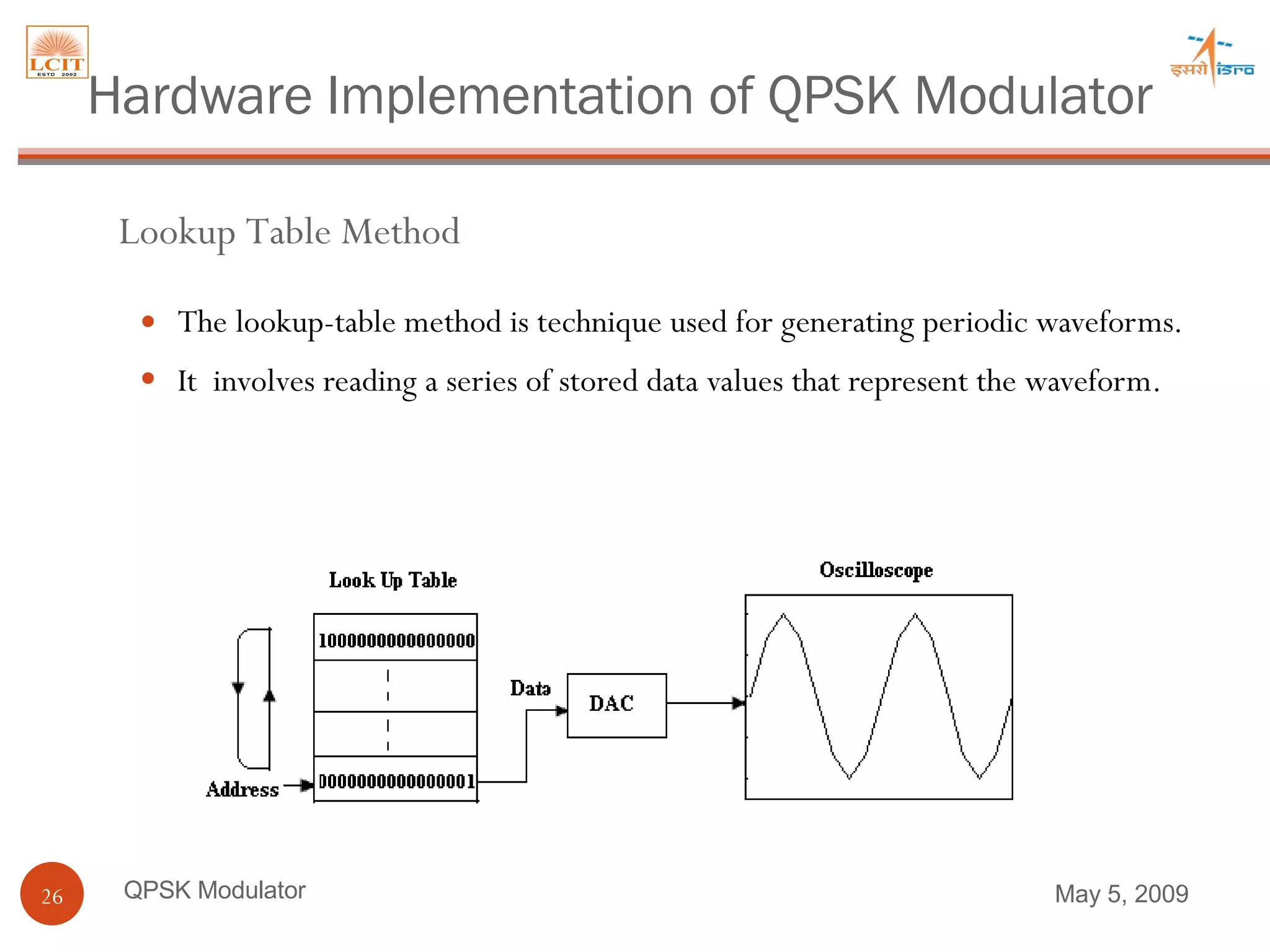

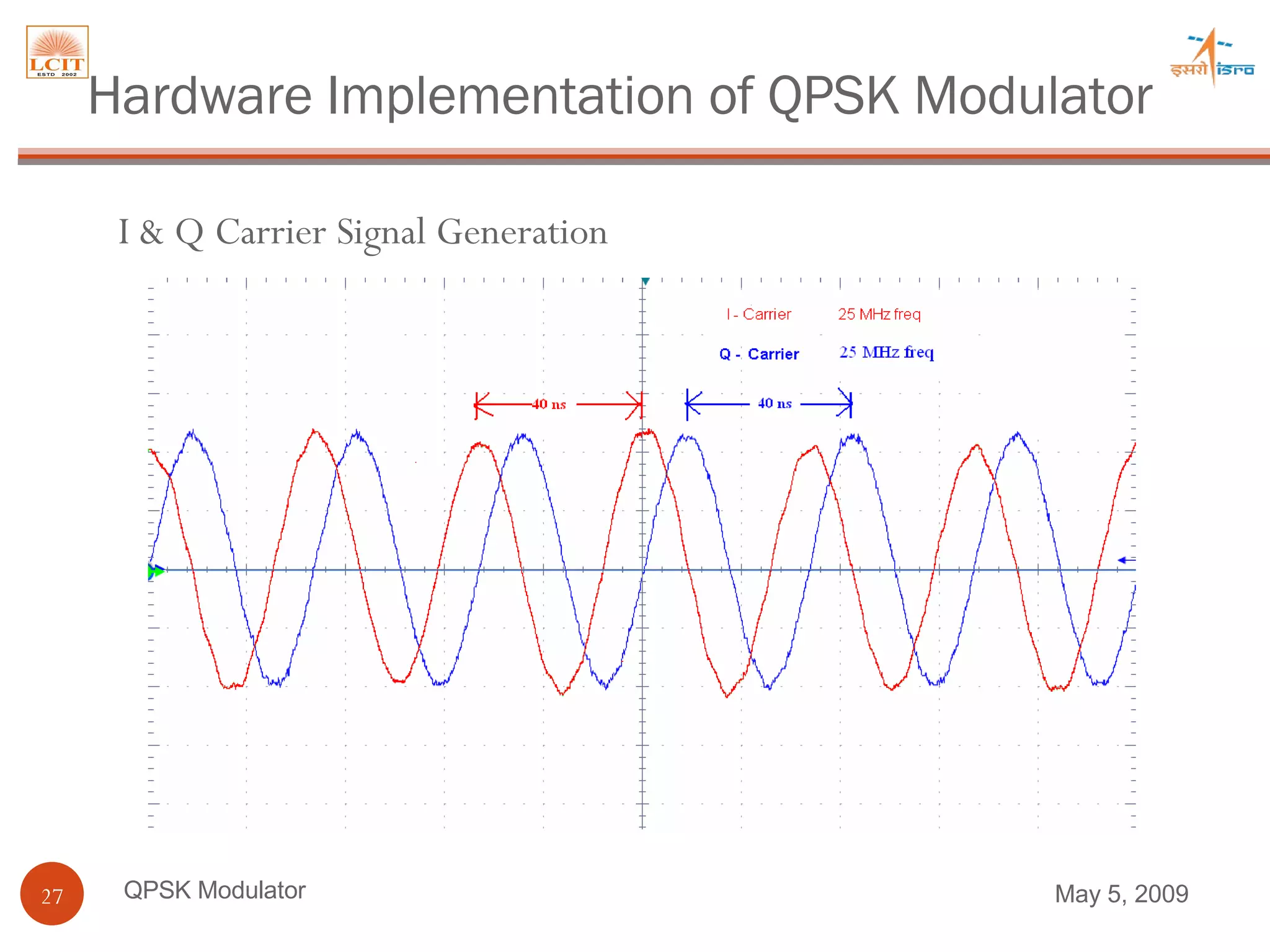

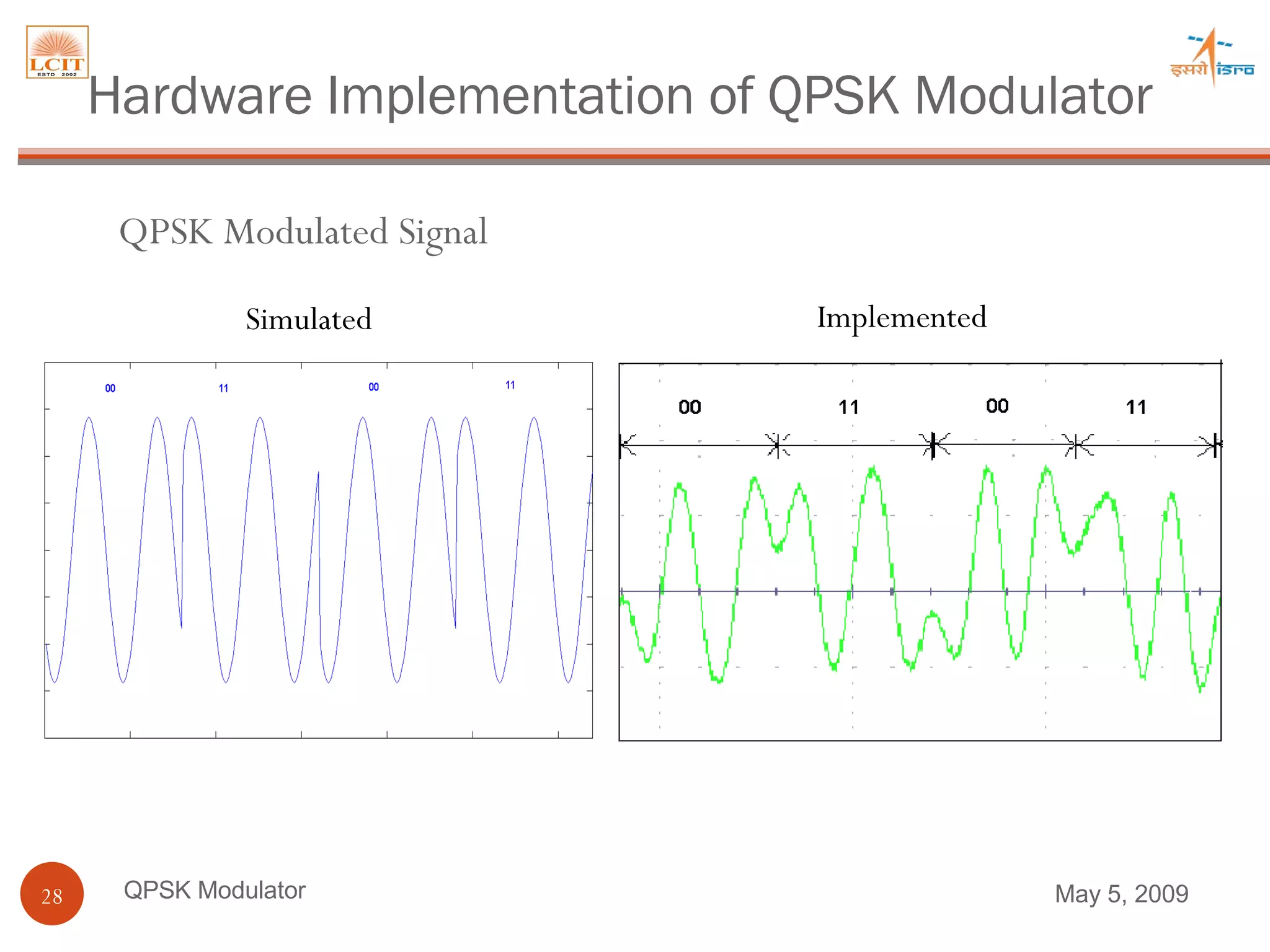

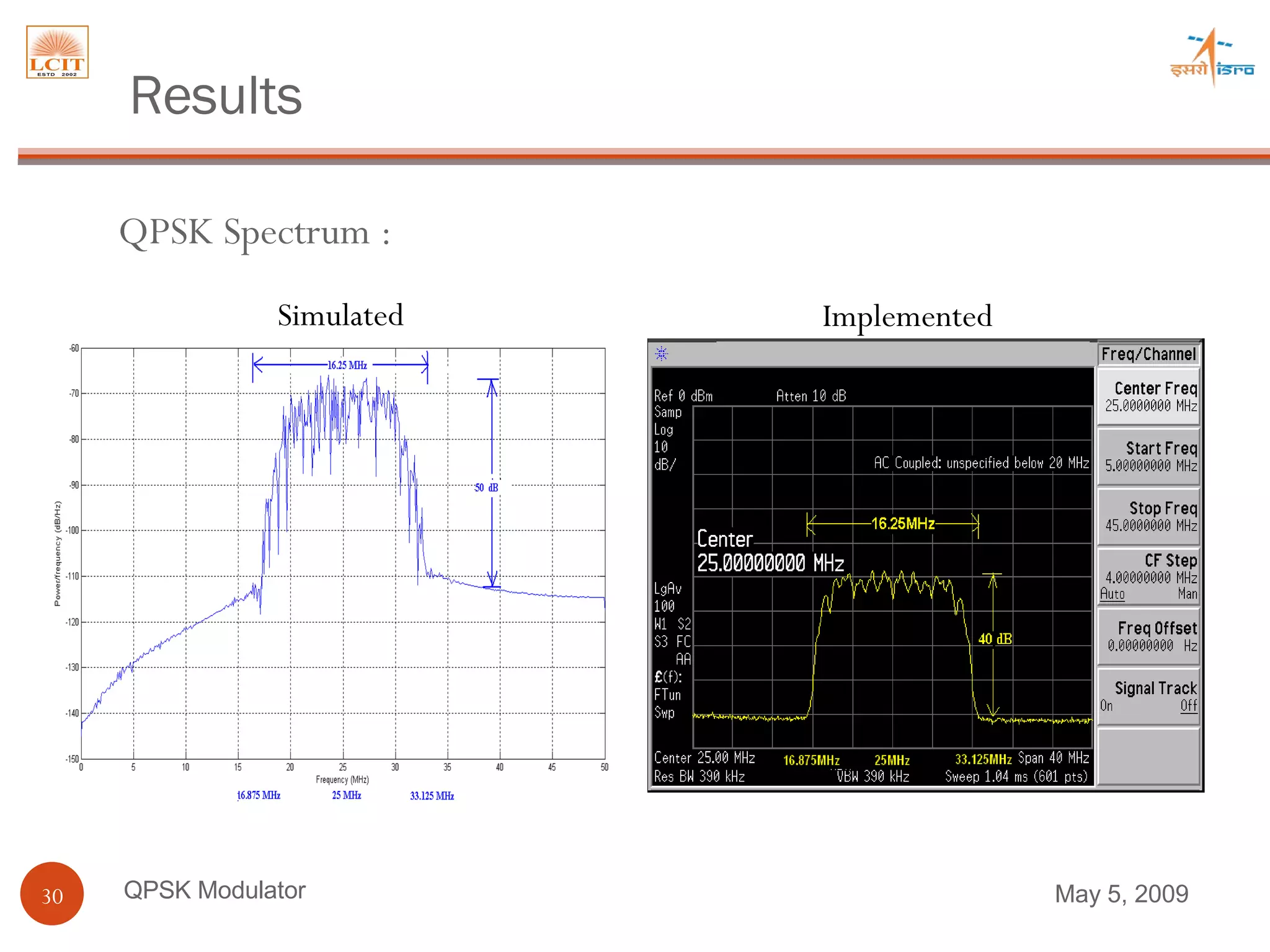

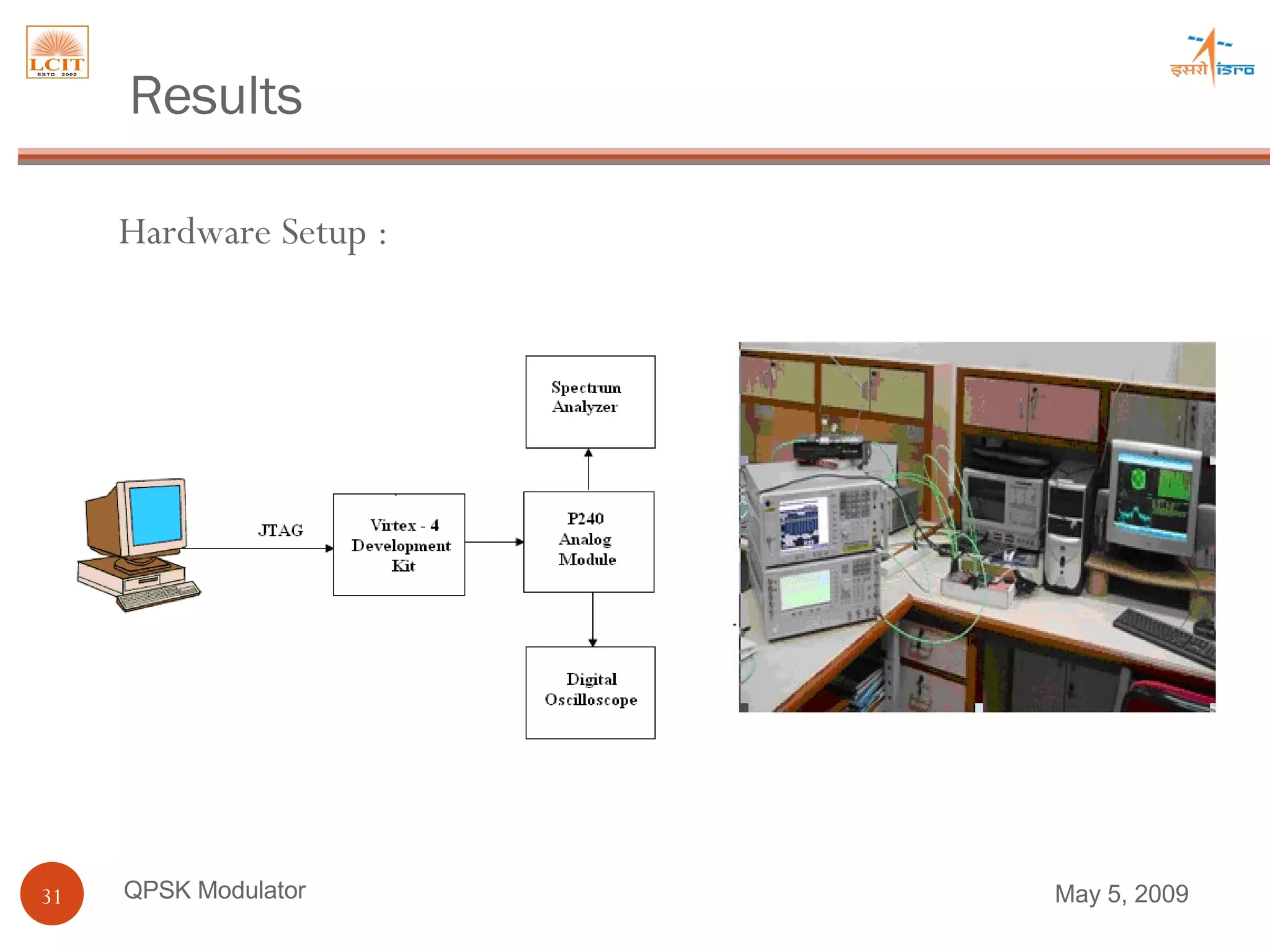

The document presents a hardware implementation of a QPSK modulator for satellite communication, detailing the project’s objectives, methodology, and results. It includes an overview of digital modulation, a description of QPSK, simulations conducted via MATLAB, and the implementation on an FPGA using Xilinx ISE software. The conclusion highlights the successful implementation and the possible future applications of the modulator in various RF subsystems.