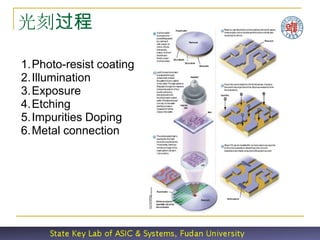

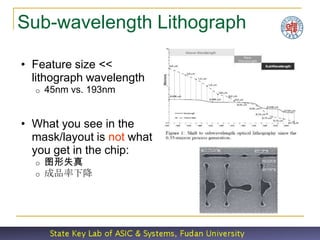

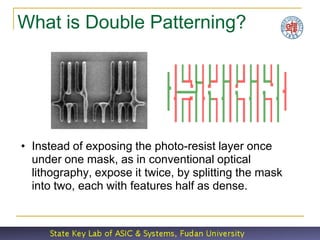

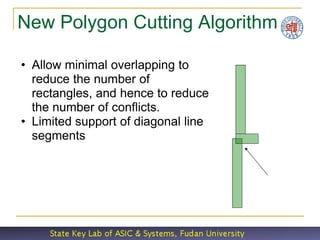

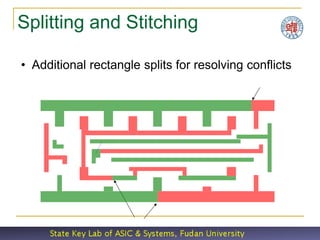

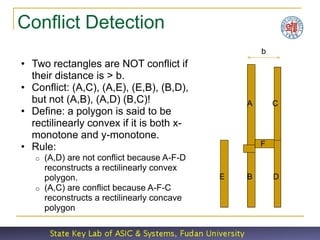

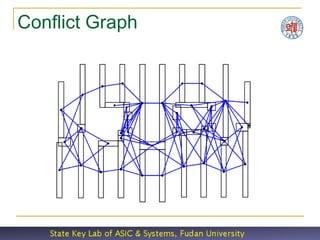

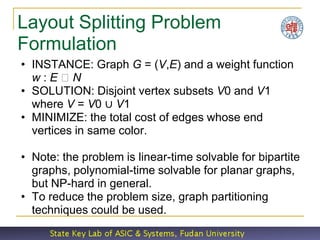

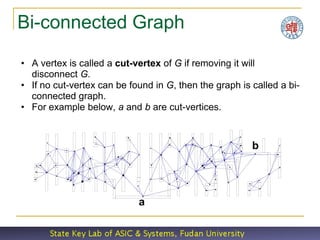

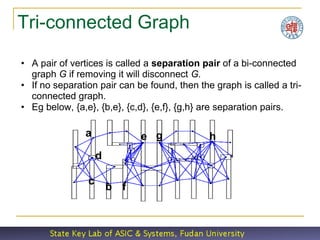

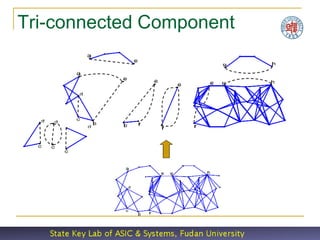

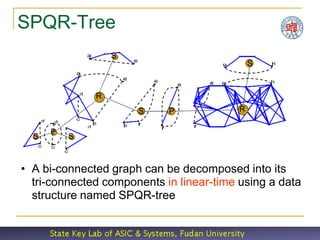

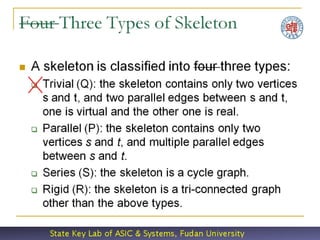

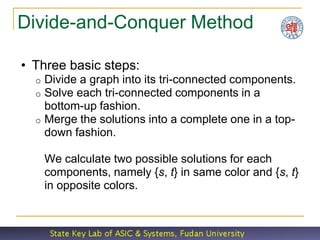

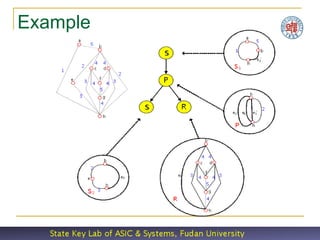

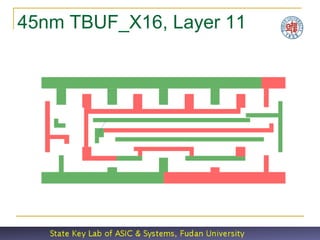

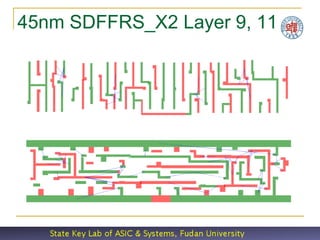

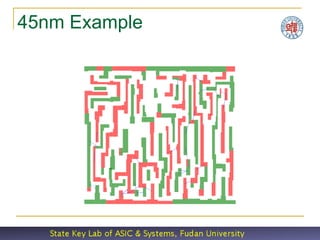

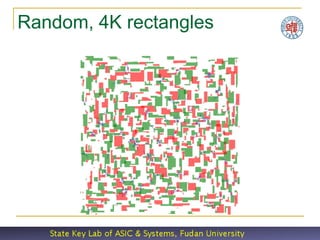

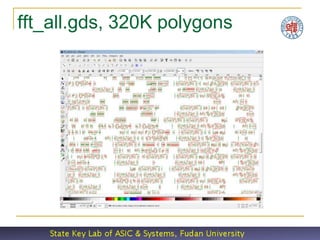

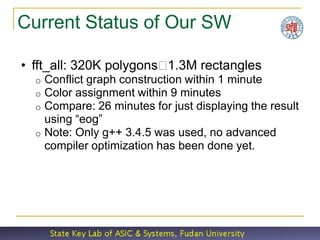

This document discusses double patterning lithography techniques. It introduces how optical lithography is approaching its limits and double patterning is needed for smaller feature sizes. It describes the double patterning process and challenges including feature distortion and decreased yield. The document outlines techniques for polygon cutting, priority search trees, and decomposing conflict graphs into tri-connected components to solve the layout splitting problem. Experimental results on test cases including a 320k polygon design show the method achieves 3-10x speedup.