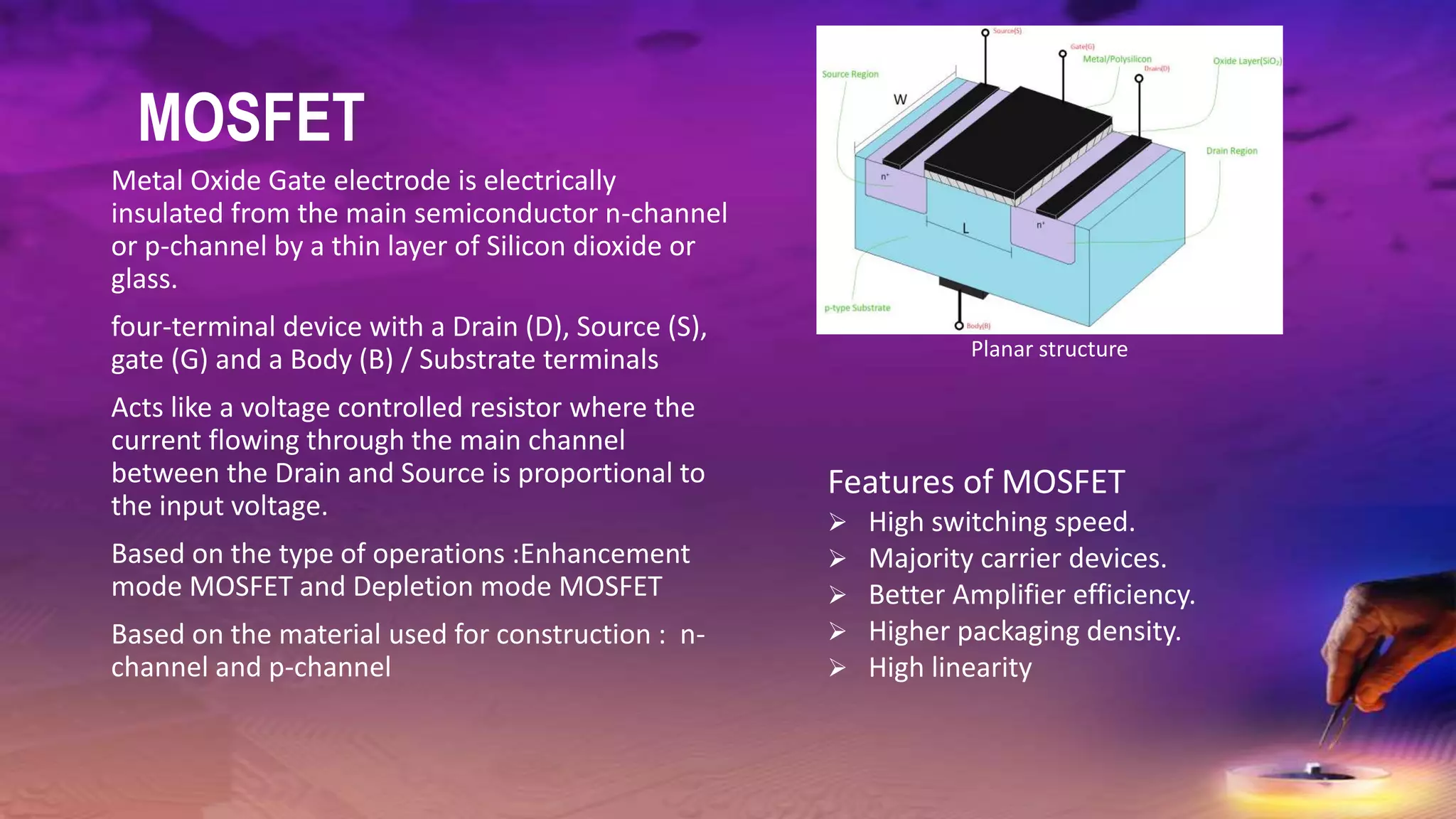

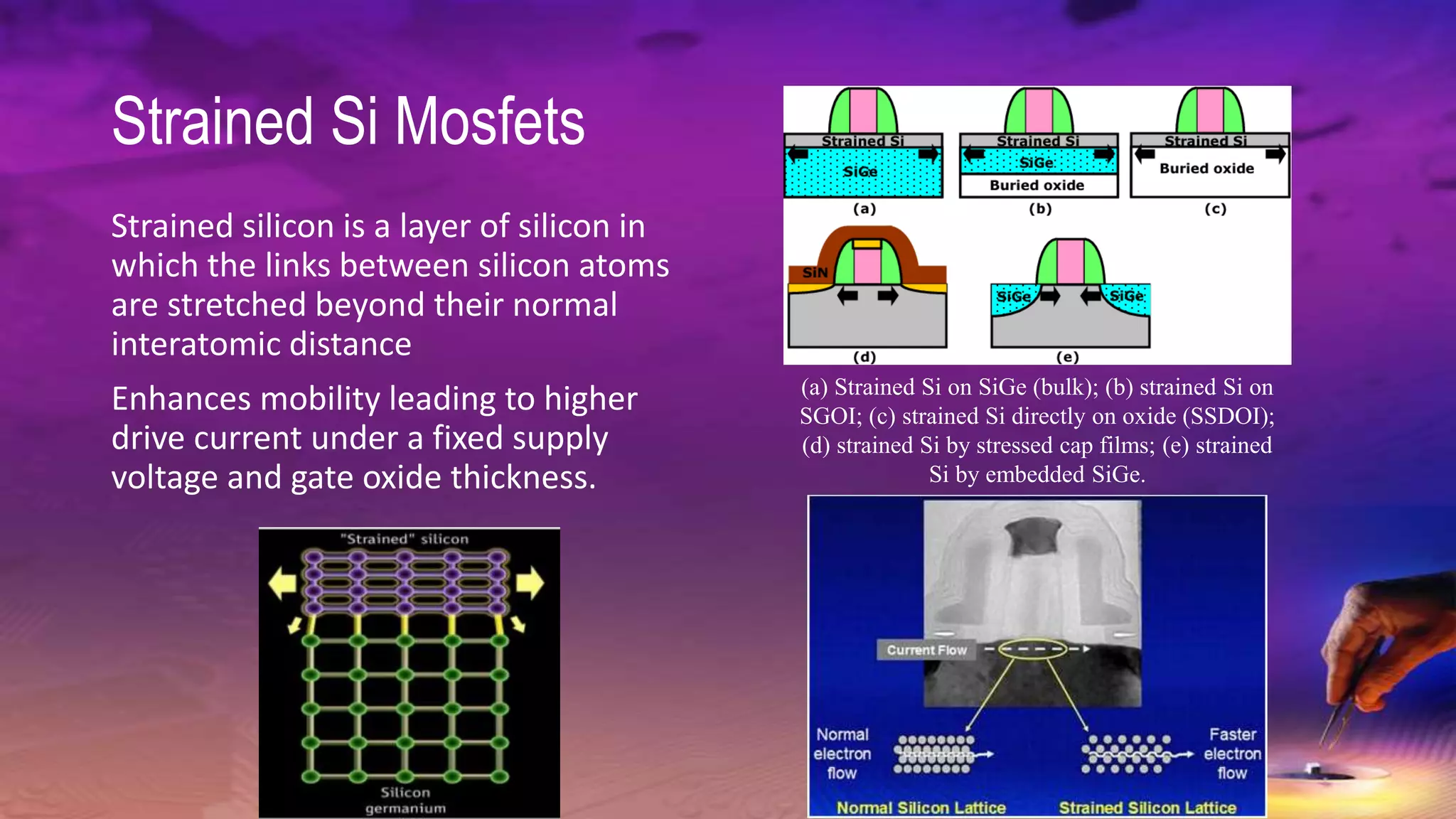

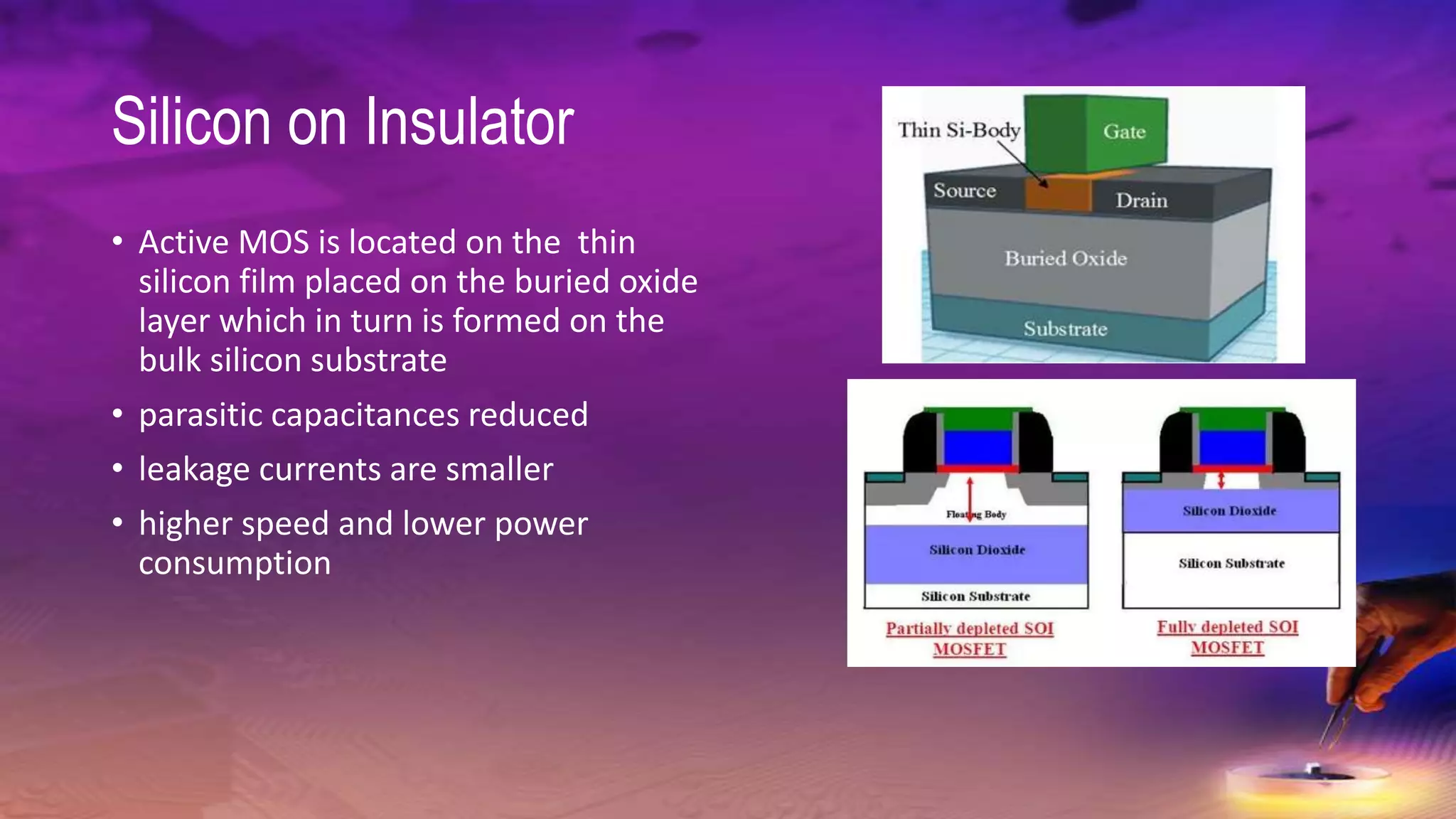

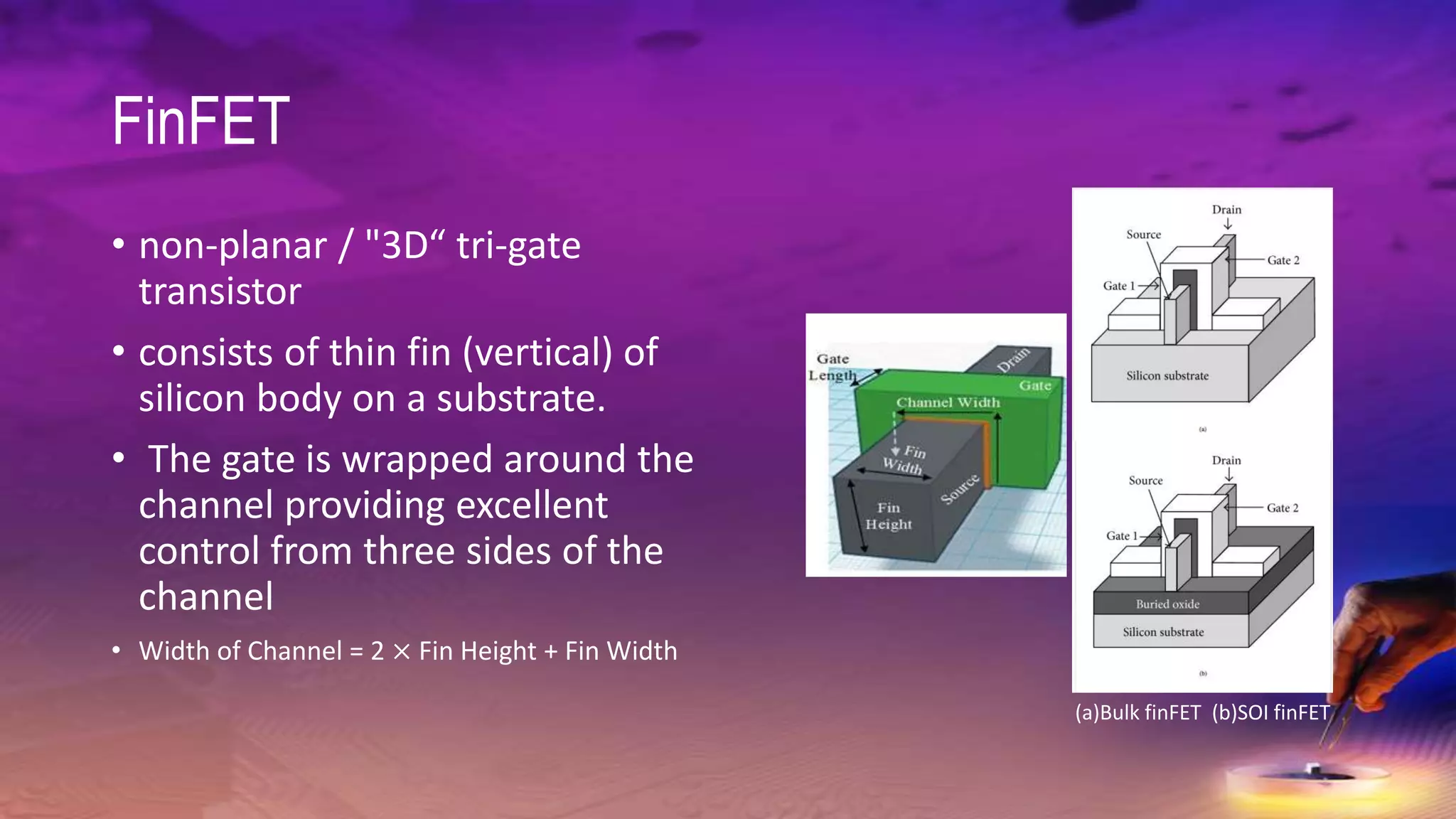

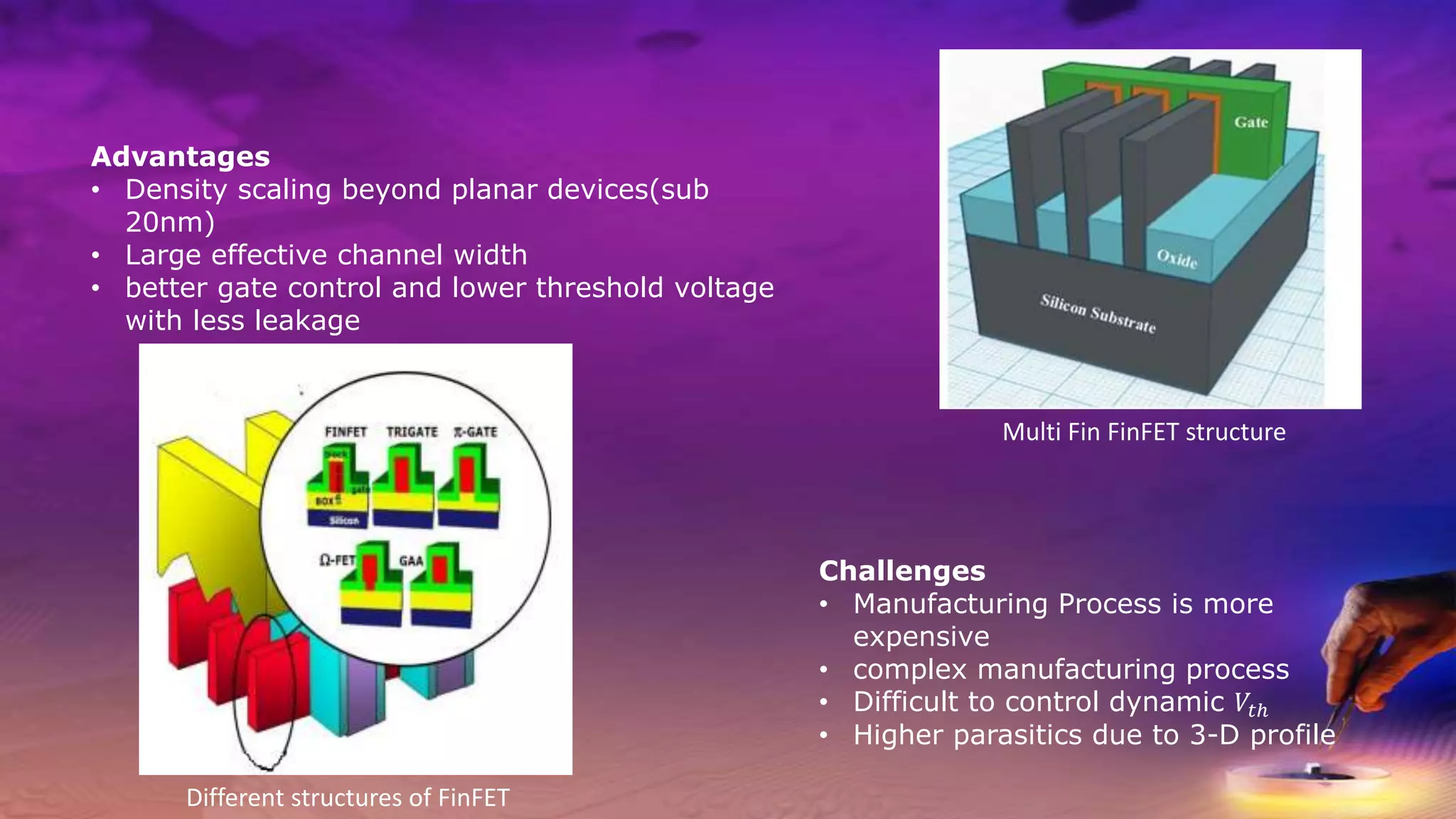

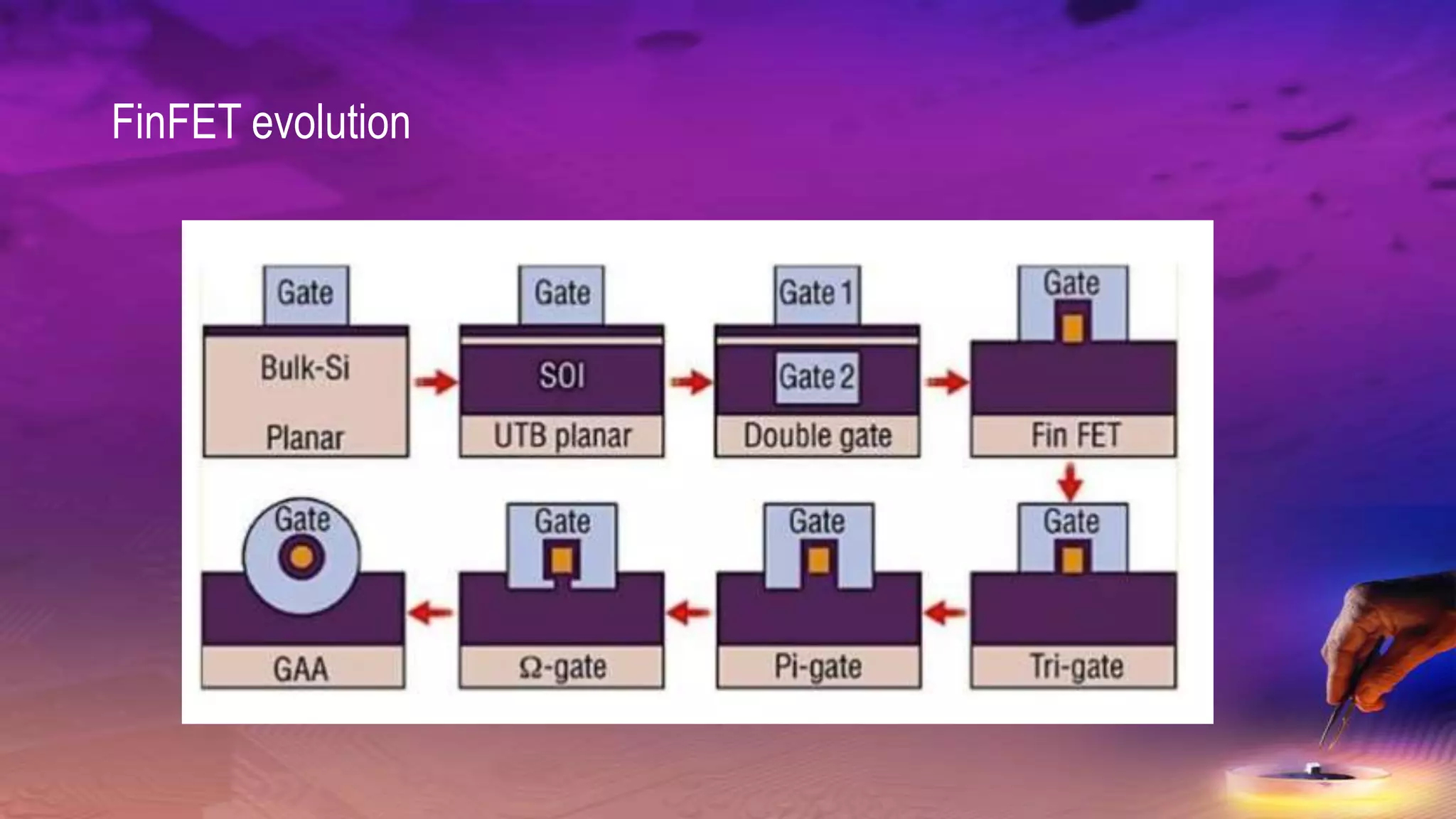

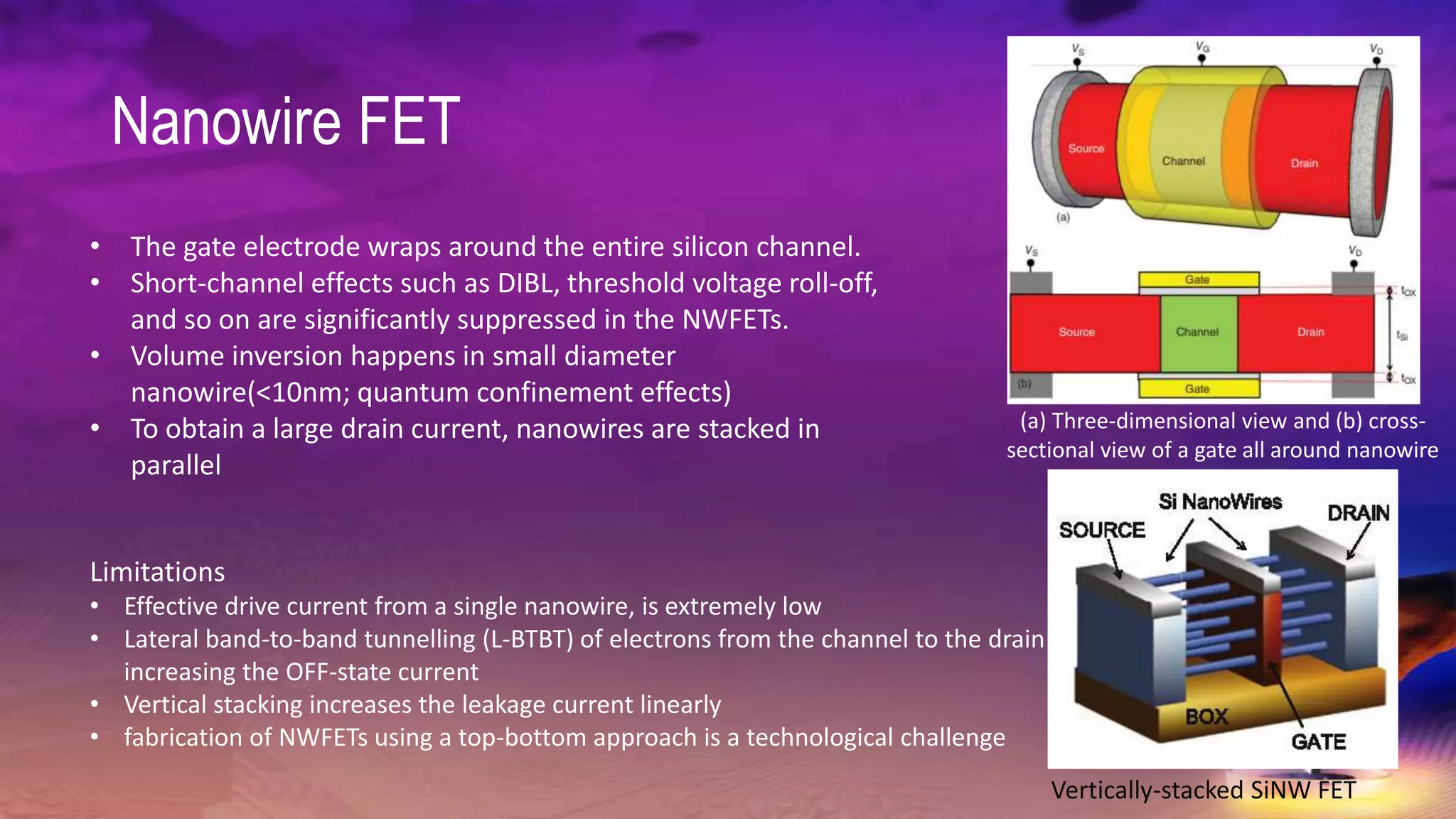

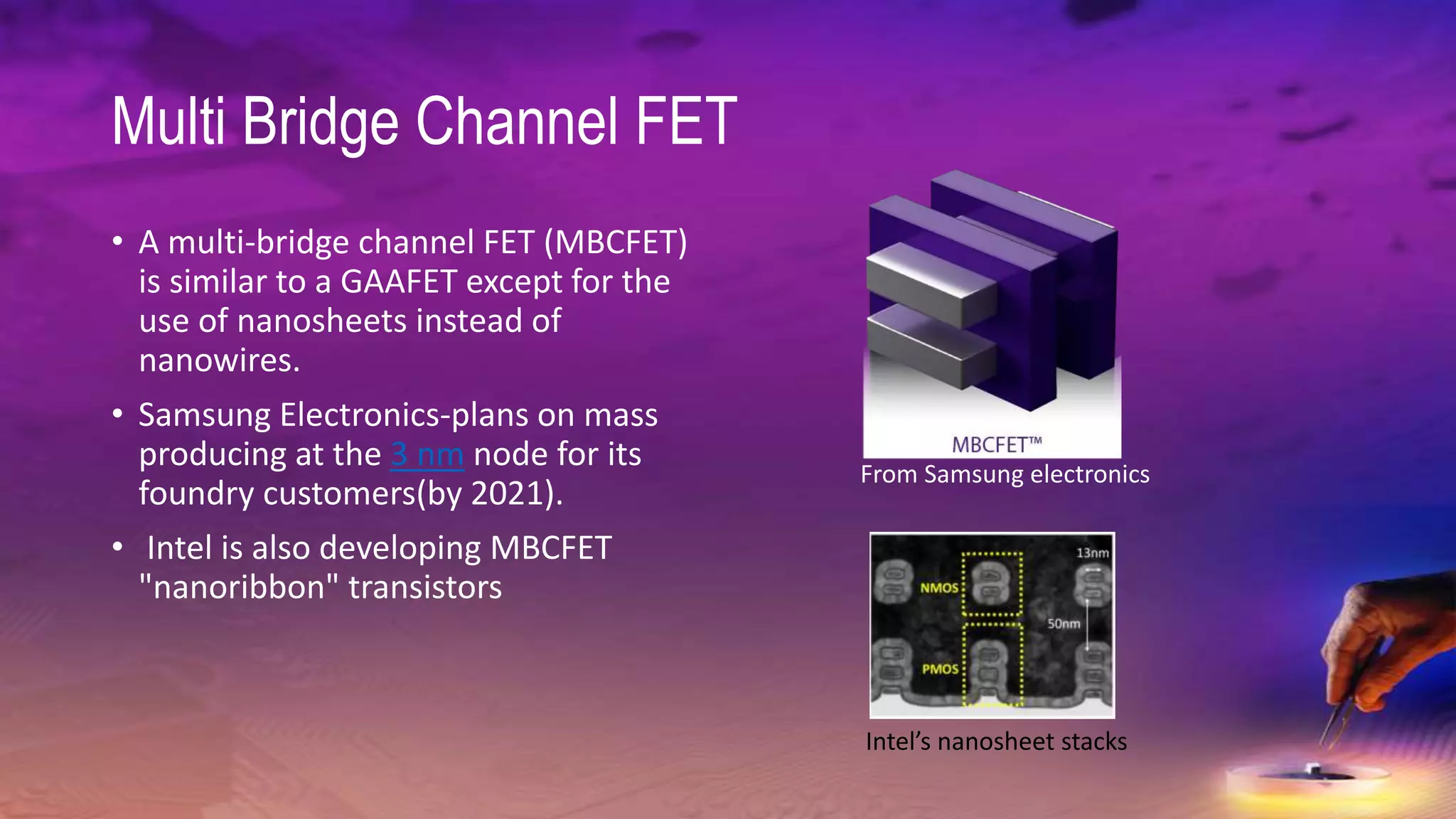

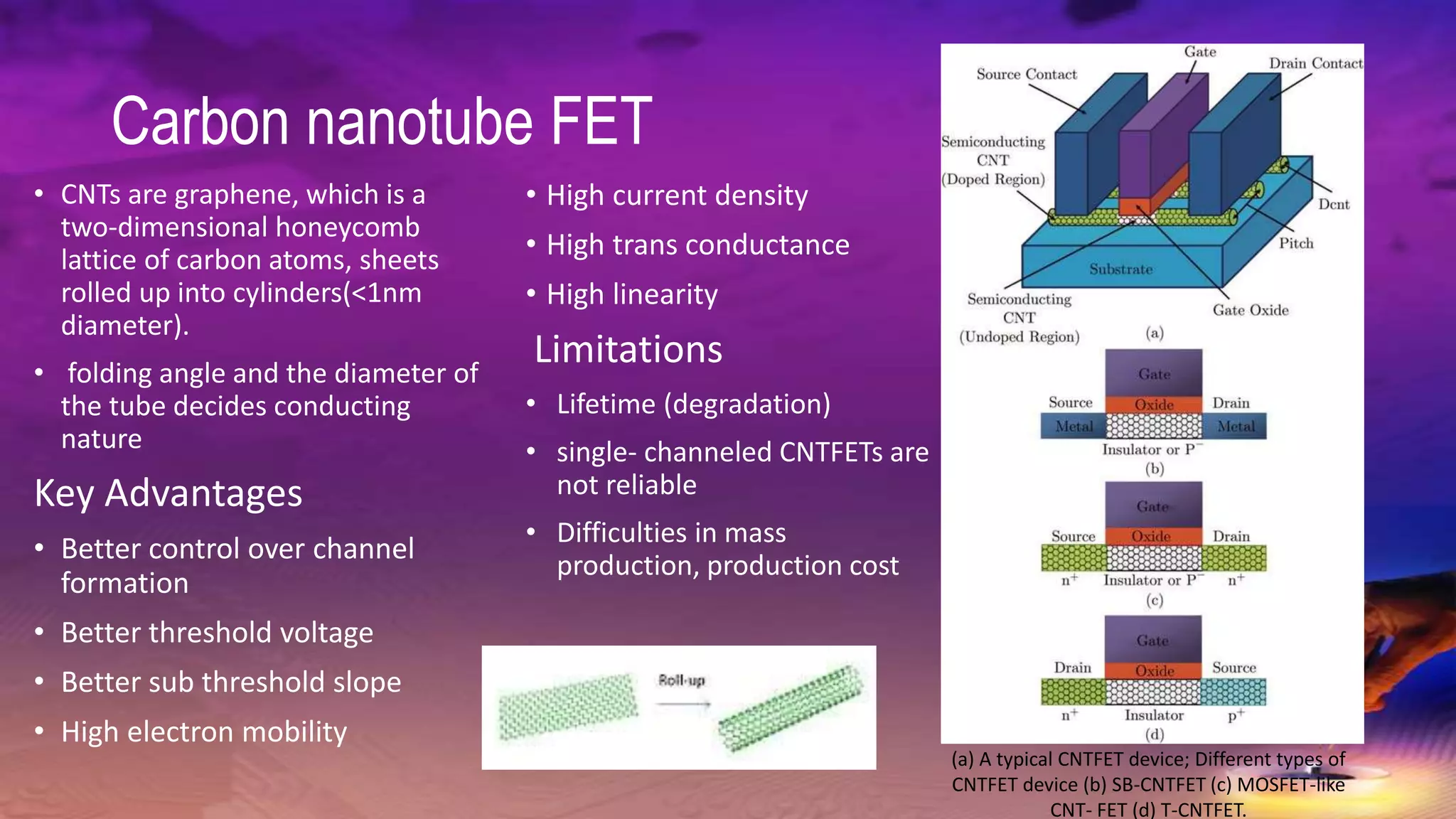

The document discusses various MOSFET structures, focusing on operational modes, materials used, and innovations for high density and low power consumption. It highlights non-classical MOSFETs like FinFETs and nanowire FETs, emphasizing their advantages in scaling and performance over traditional devices. Additionally, it covers the limitations and complexities of manufacturing these advanced structures.