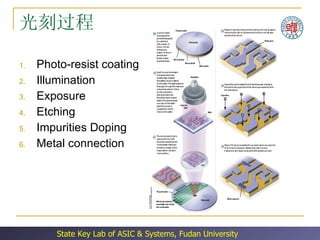

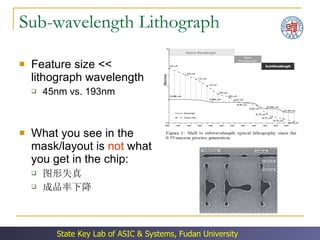

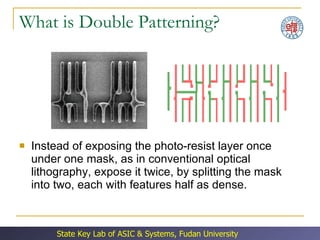

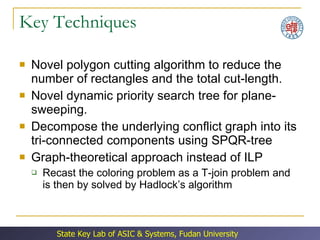

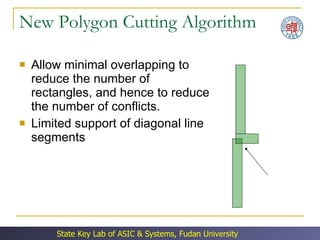

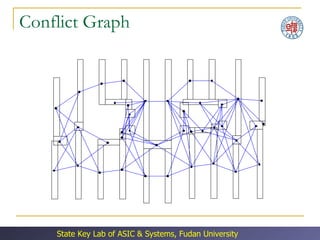

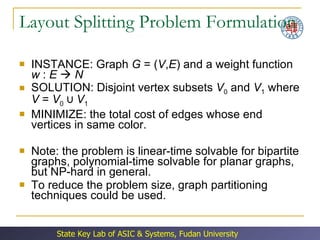

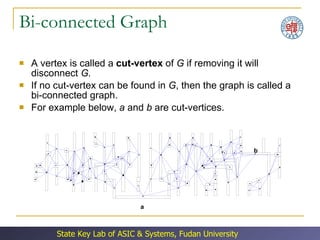

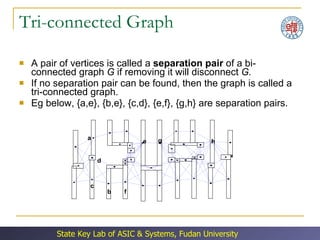

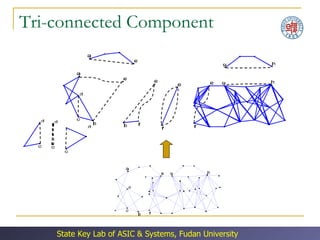

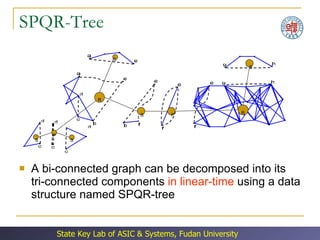

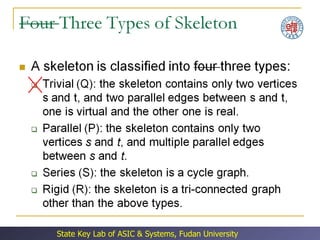

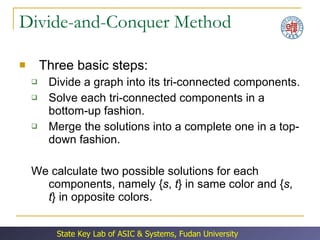

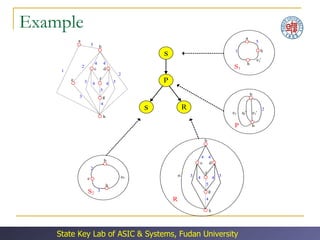

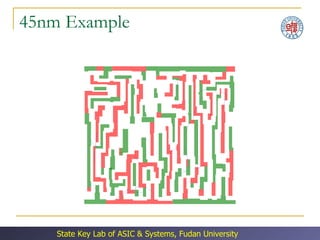

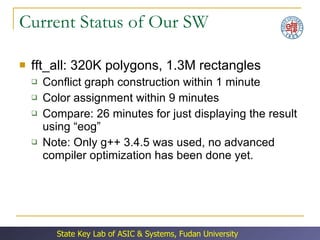

Double patterning lithography is a technique used to print integrated circuit designs when feature sizes shrink below the resolution limits of a single exposure. It involves splitting the circuit layout into two masks and exposing the photo-resist layer twice to print the full design. Decomposing the circuit layout and assigning patterns to the two masks is an NP-hard graph coloring problem. The document describes techniques for decomposing the conflict graph that represents incompatible patterns, including using SPQR trees to decompose into tri-connected components and solving each independently. Experimental results show the proposed method can achieve a 3-10x speedup over other approaches.