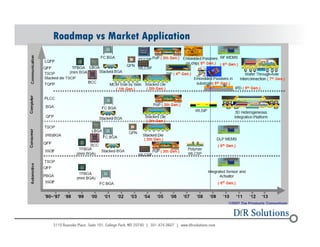

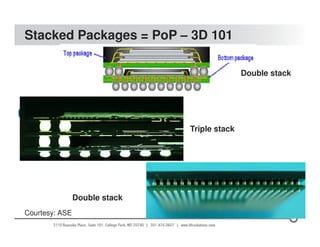

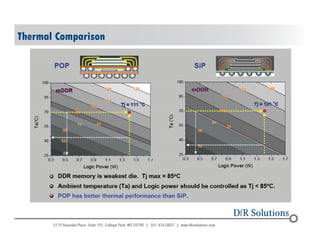

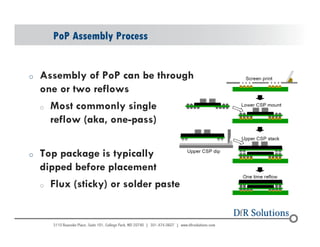

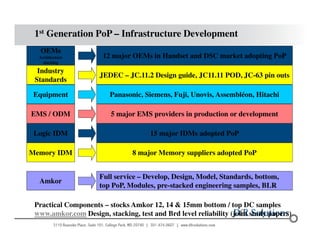

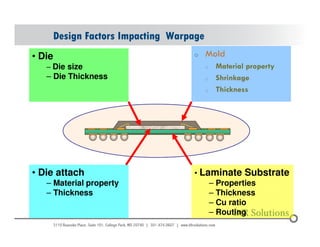

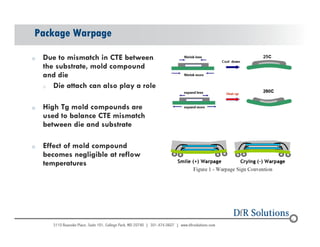

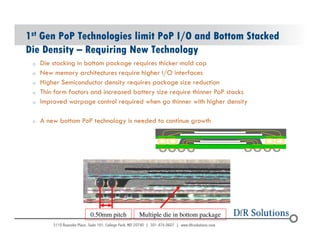

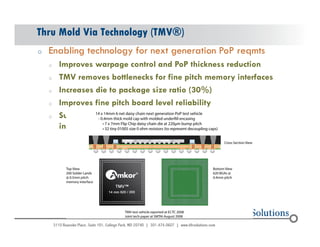

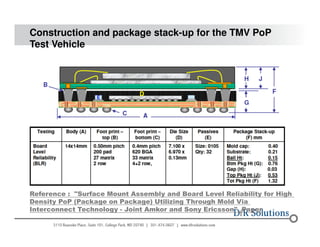

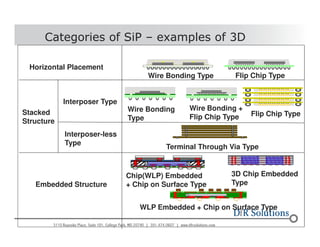

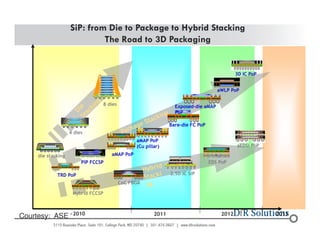

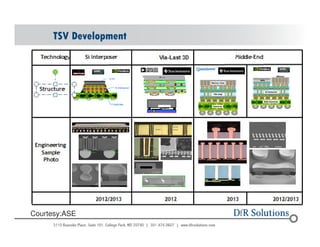

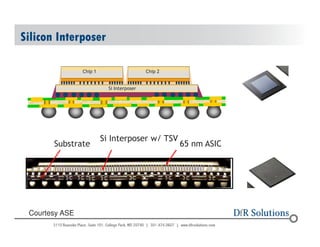

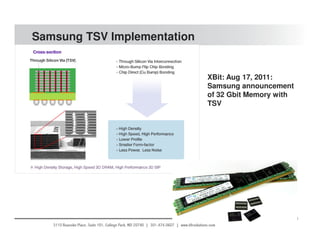

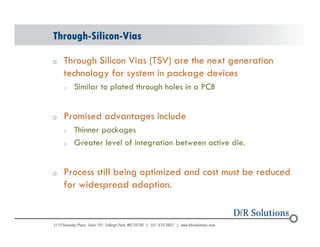

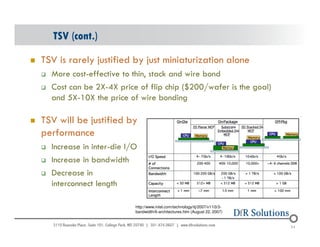

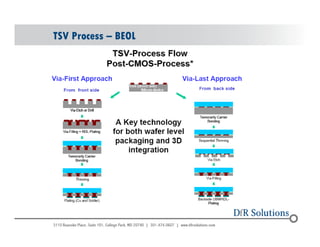

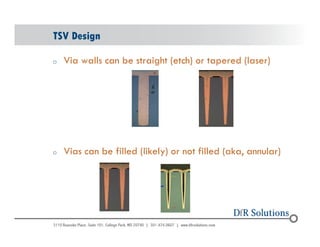

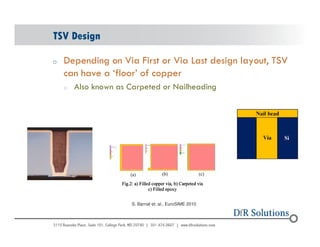

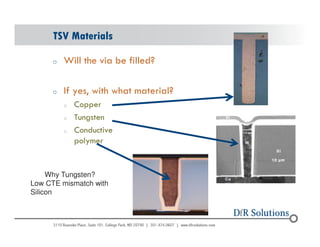

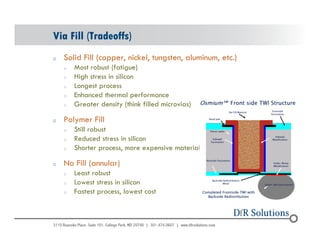

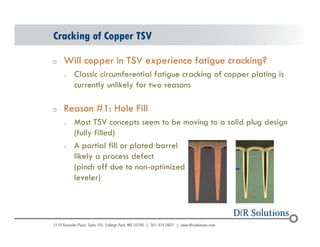

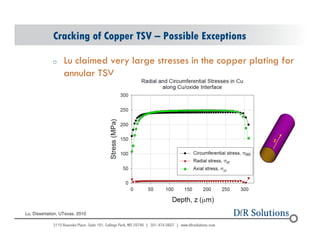

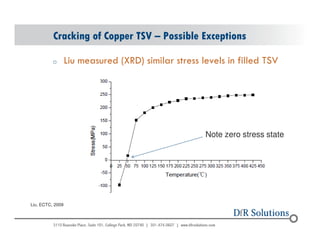

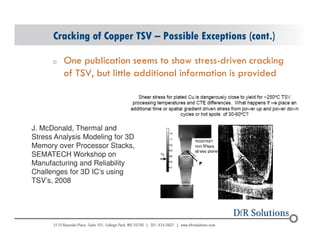

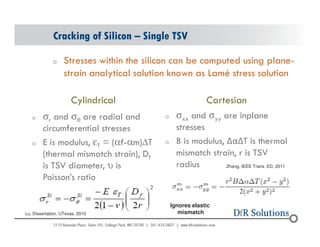

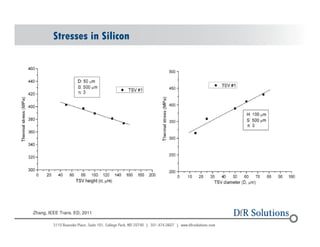

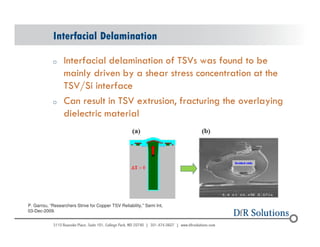

This document summarizes an advanced packaging presentation that covered topics like package-on-package (PoP), system-in-package (SiP), through silicon vias (TSV), and bottom terminated components. PoP provides benefits like less board area, better performance, and defined supply chain ownership. TSV and SiP enable further semiconductor integration challenges but require optimization for cost and reliability concerns like copper cracking.