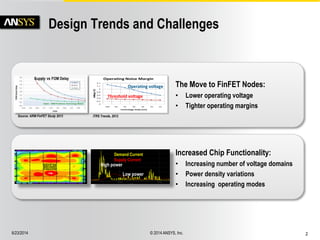

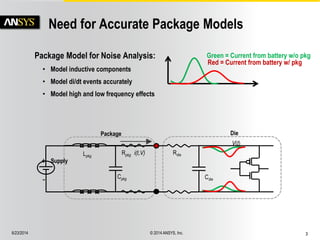

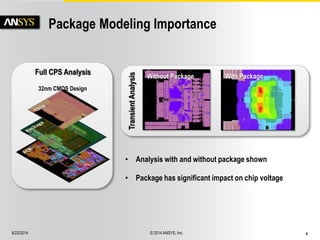

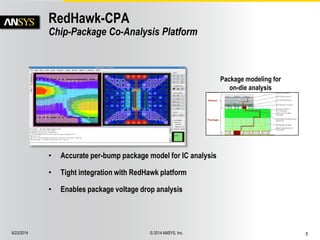

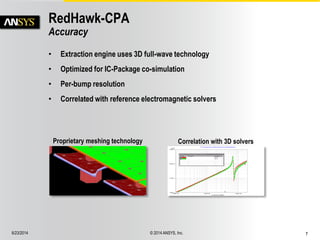

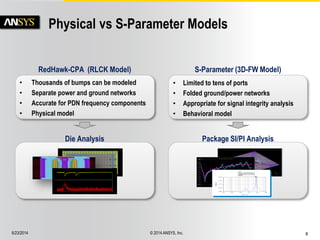

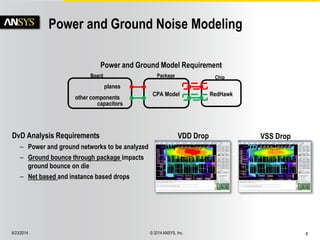

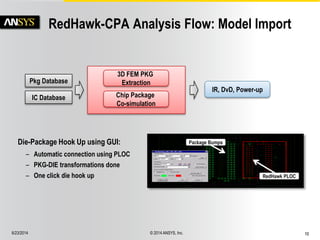

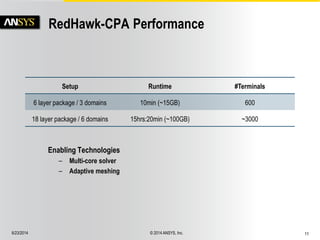

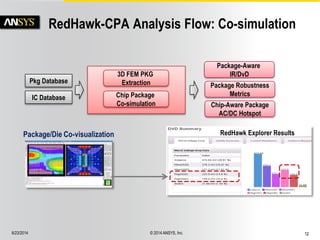

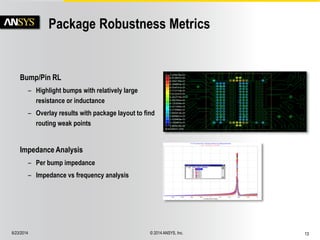

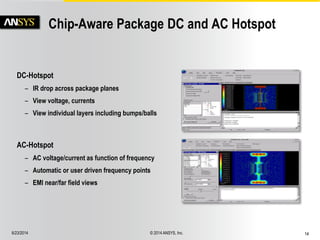

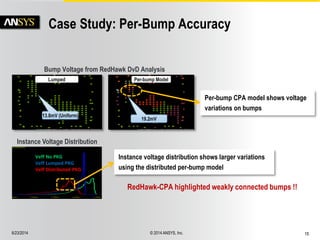

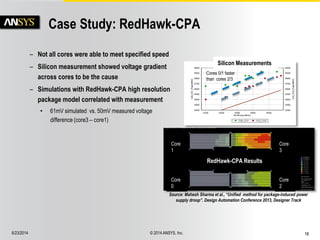

The document discusses the Redhawk-cpa chip-package co-analysis platform, which improves the accuracy of package models for integrated circuit (IC) analysis. It emphasizes the need for precise package modeling to analyze voltage drops and power integrity in advanced semiconductor designs with increasing chip functionality. The platform features high bump resolution, automatic import into Redhawk, and support for various analysis types, enabling efficient IC-package co-simulation.