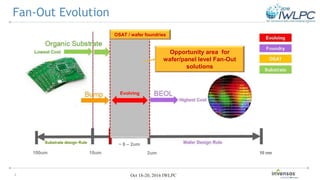

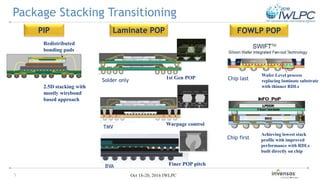

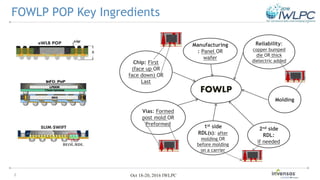

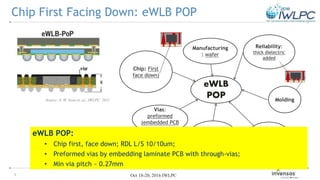

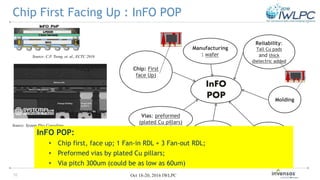

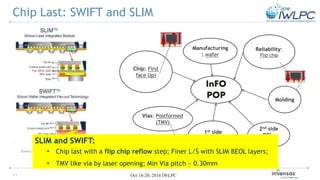

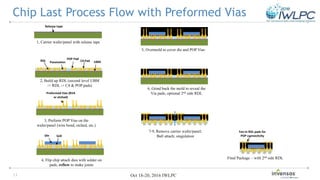

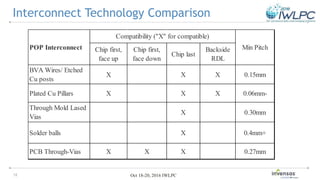

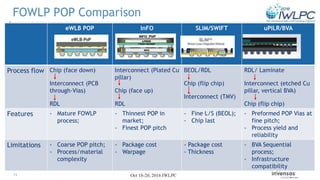

The document discusses the transition from laminate to fan-out wafer level packaging (WLP) and highlights key features and interconnect technologies such as chip first and chip last manufacturing approaches. It provides insights into future growth in the fan-out packaging market, with a projected $2.5 billion valuation by 2020, and various interconnect technologies like BVA and UPILR that aid in achieving high-density and reliable interconnects. Finally, it outlines significant cost advantages of the sequential processing method while acknowledging contributions from various research entities.