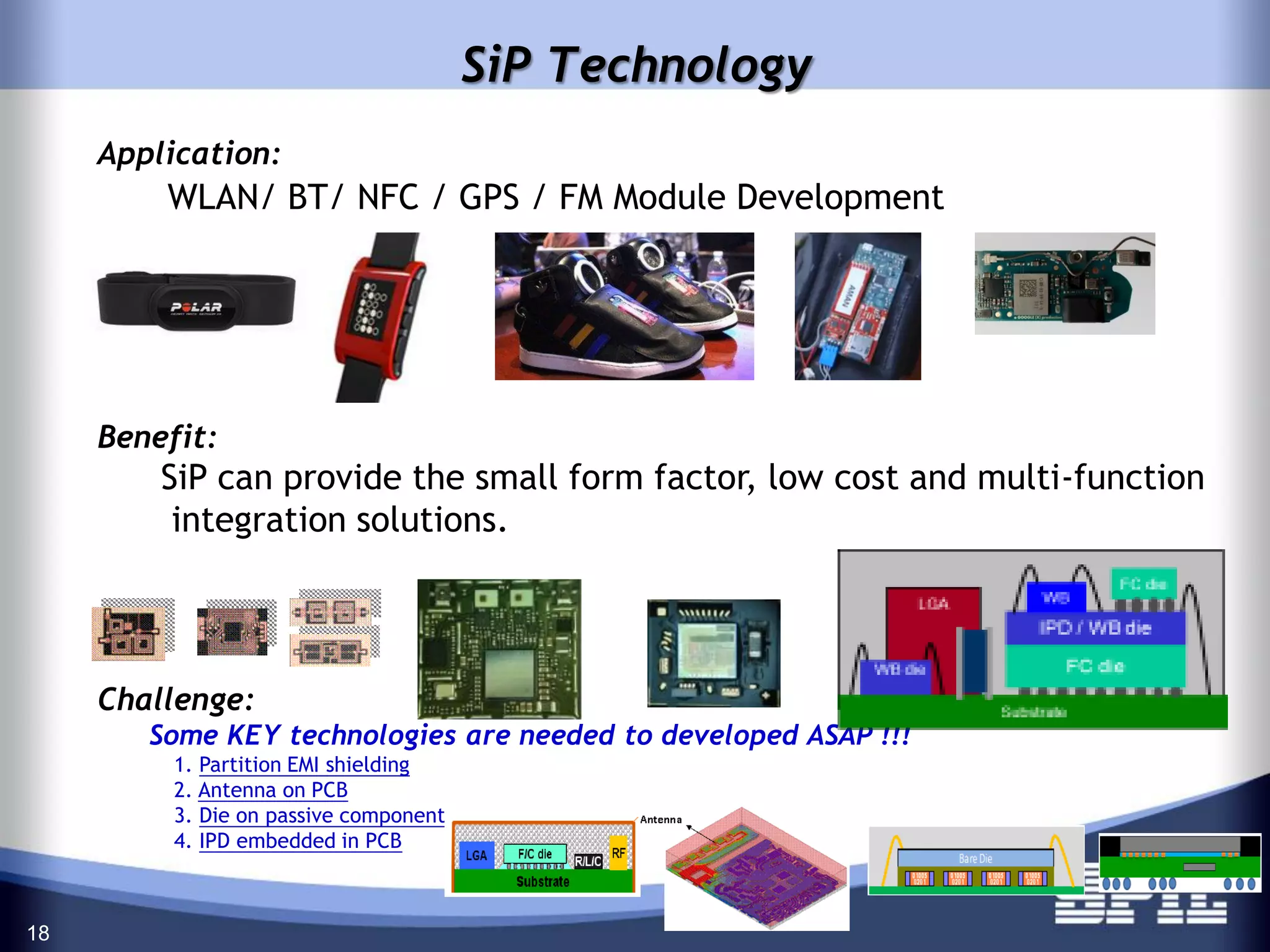

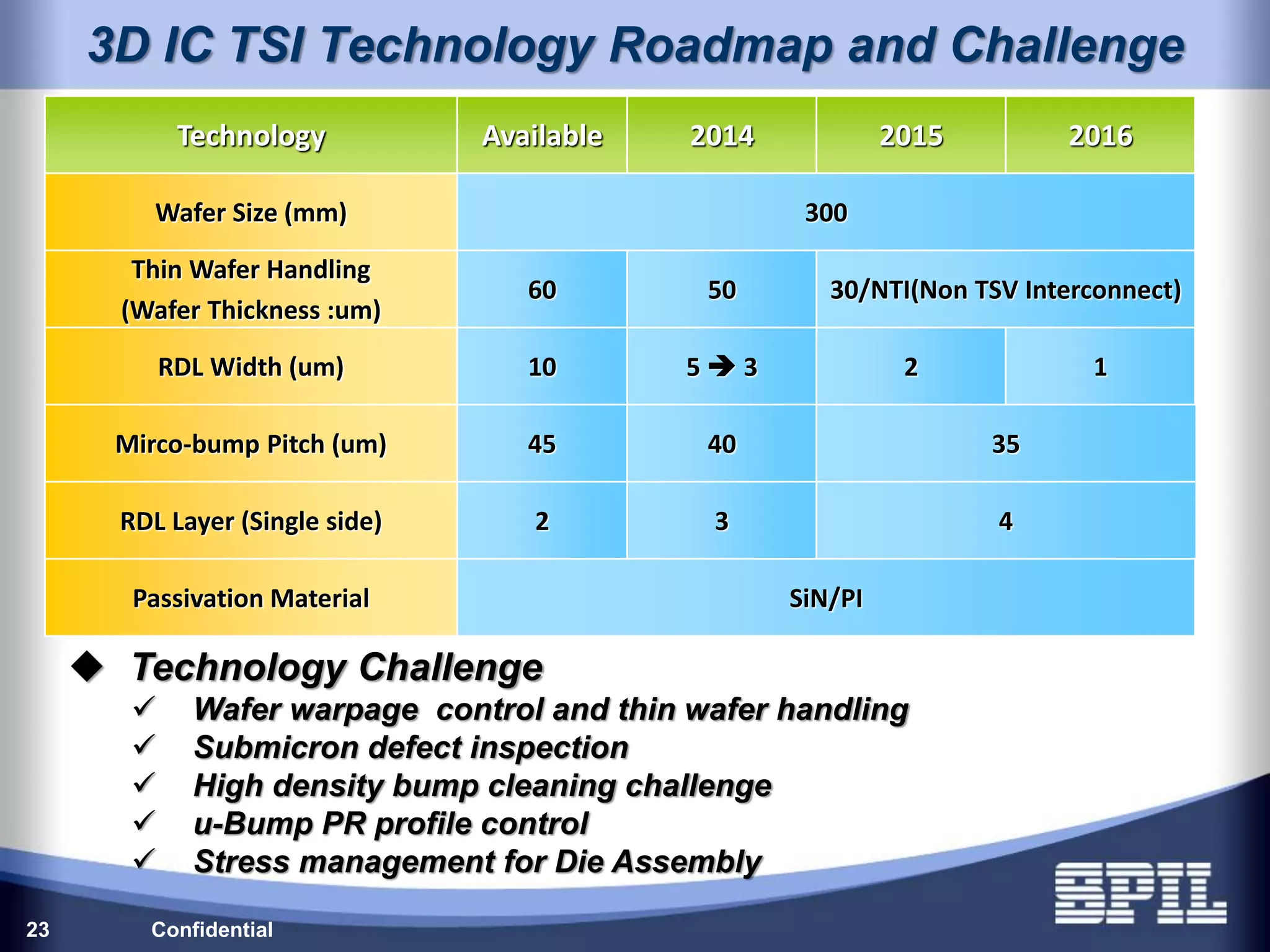

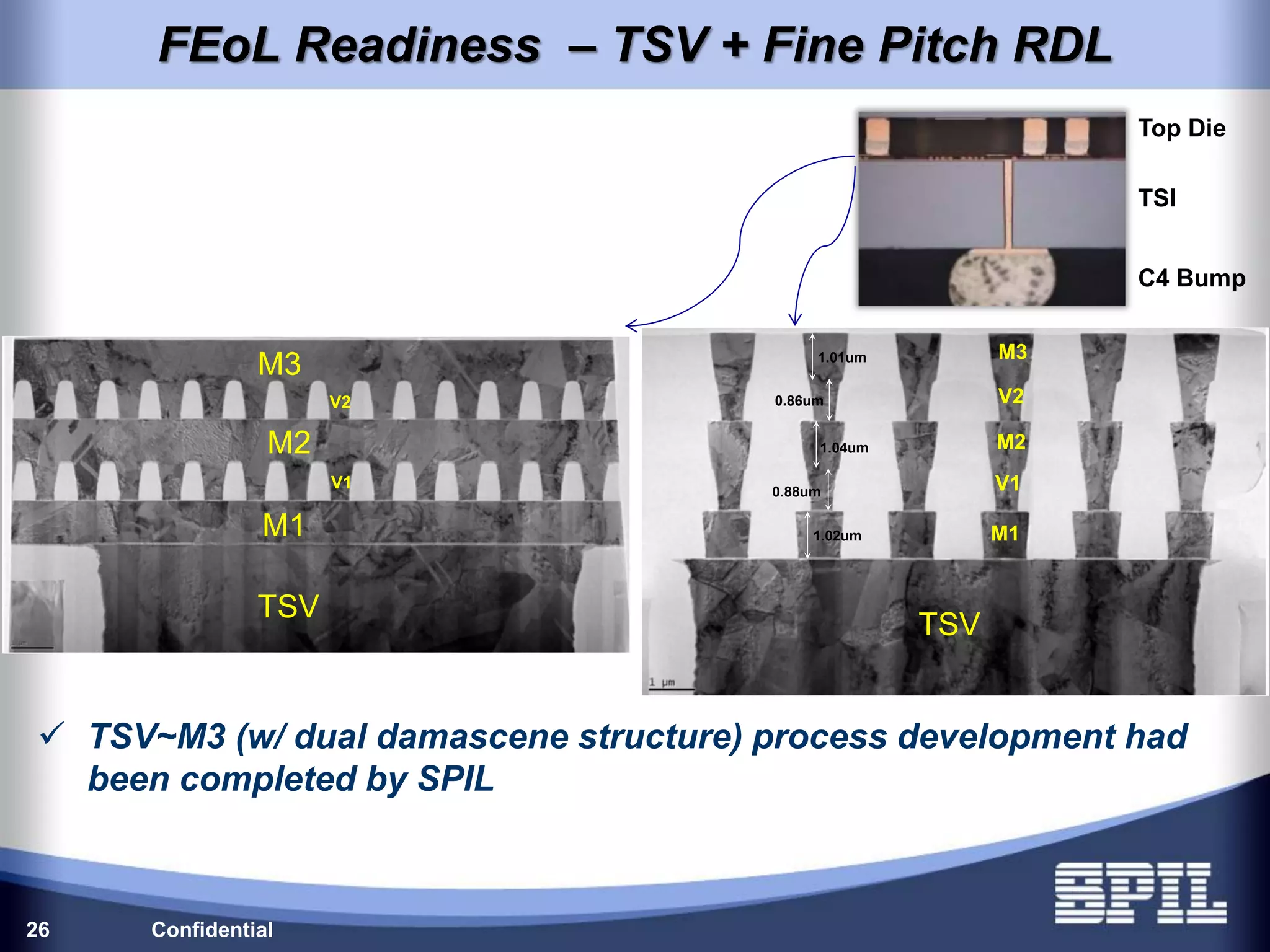

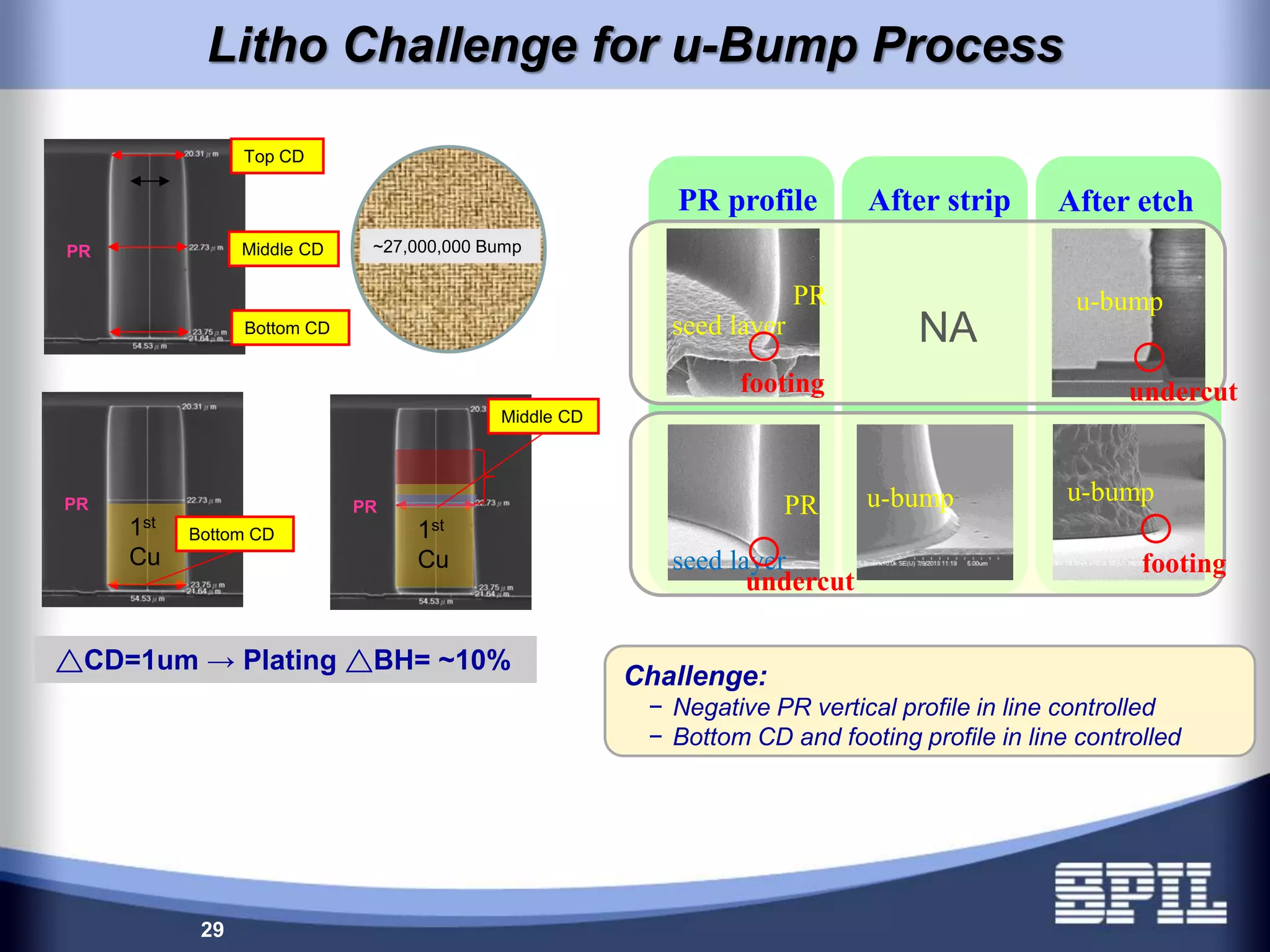

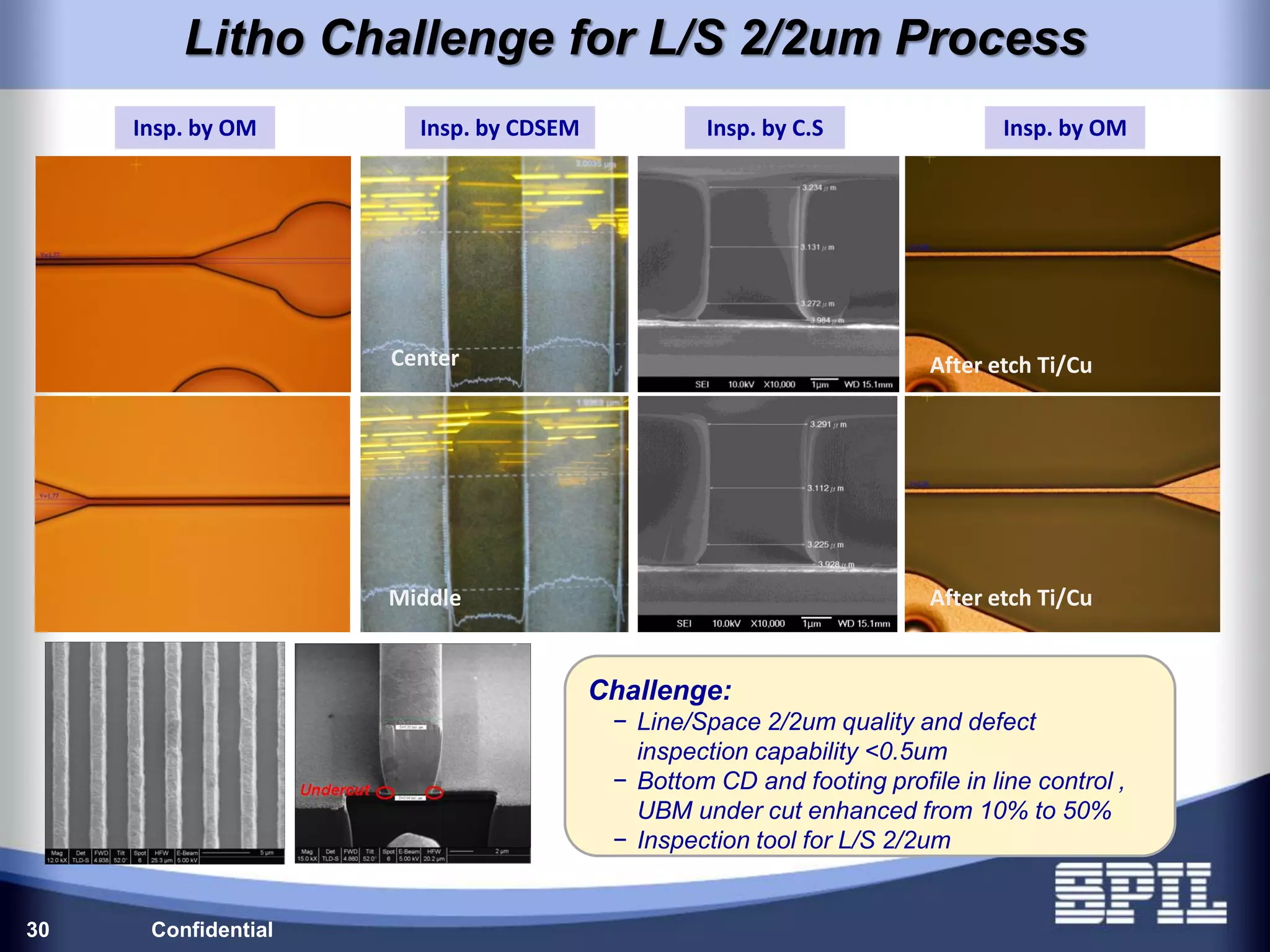

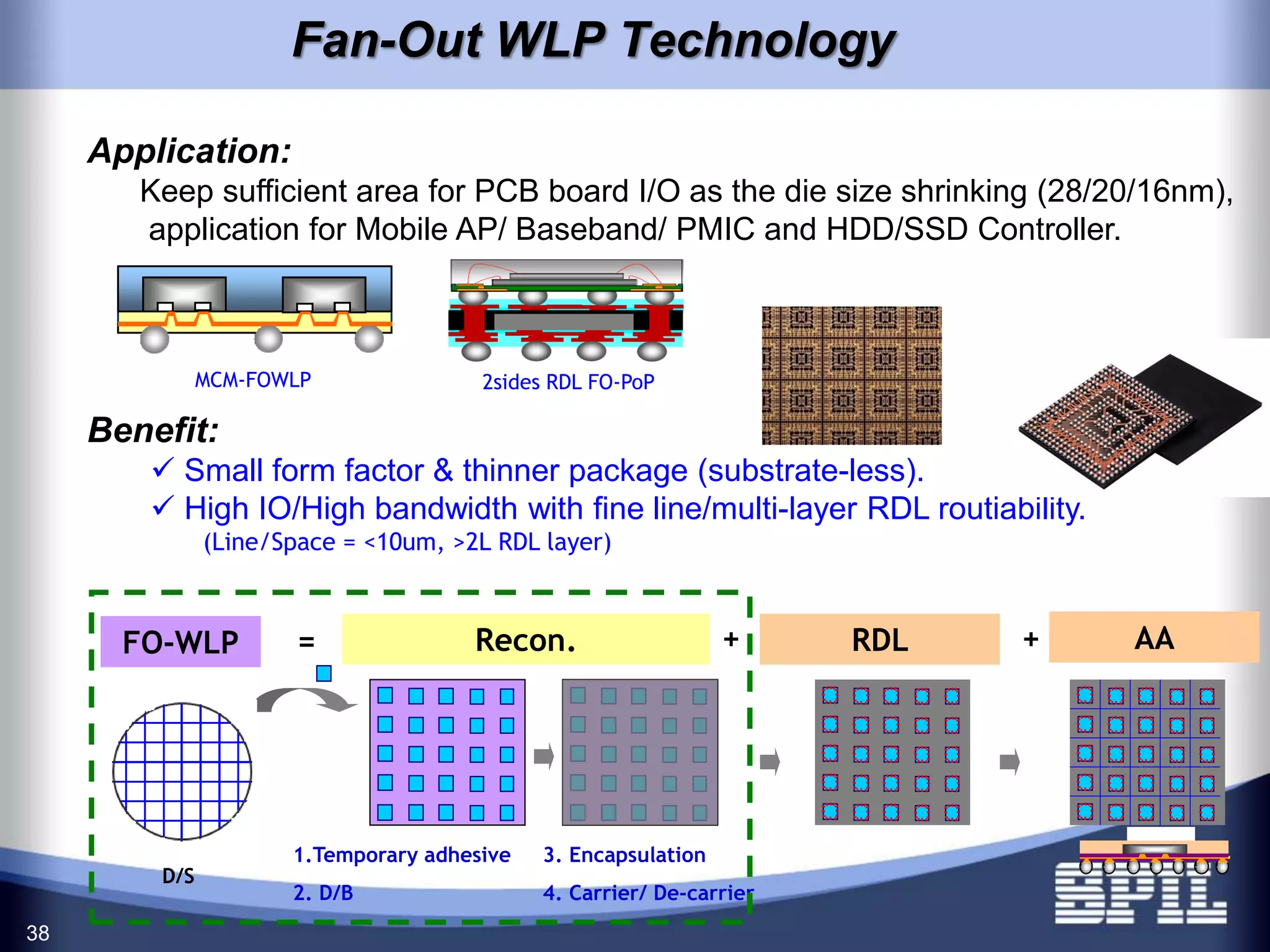

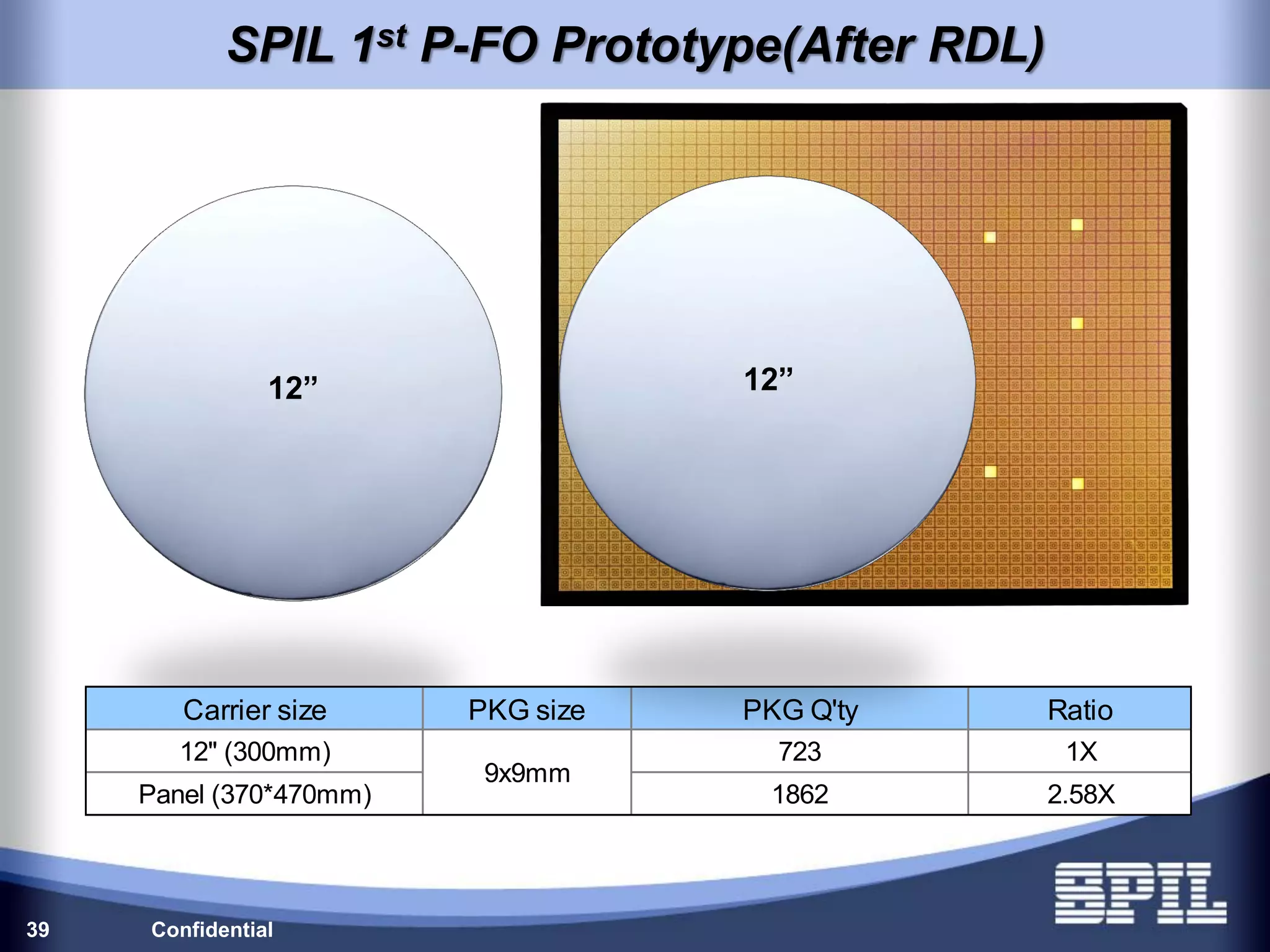

SiP technology can provide small form factors, low costs, and multi-function integration solutions. Some key technologies need to be developed to realize these benefits, including EMI shielding partitioning, antenna integration on PCBs, die placement on passive components, and integrating intellectual property cores directly into PCBs. Fan-out wafer level packaging and fan-out package-on-package technologies allow for thinner packages and high I/O routing densities at fine line/space pitches. Challenges include lithography control at sub-2 micron resolutions, high-density bump cleaning, and thin wafer warpage control.