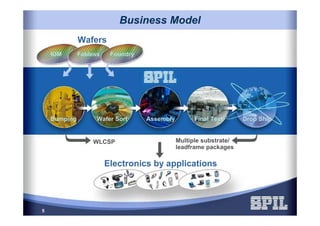

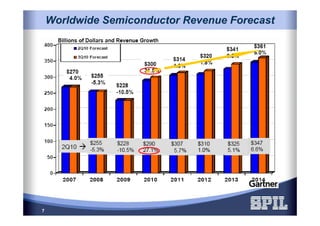

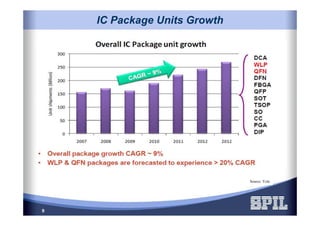

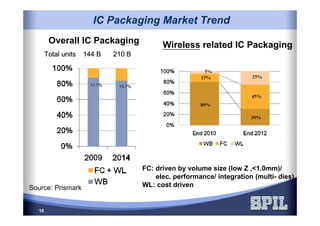

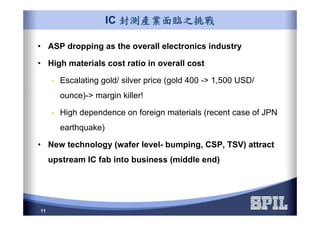

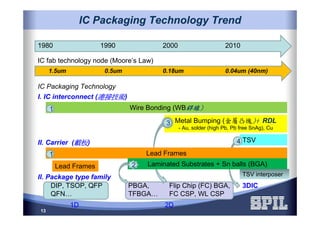

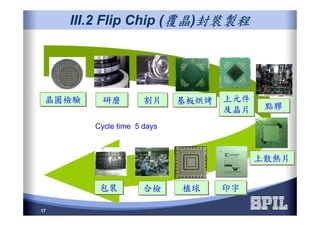

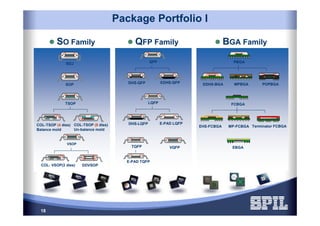

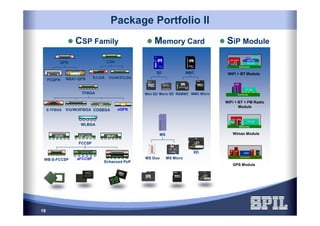

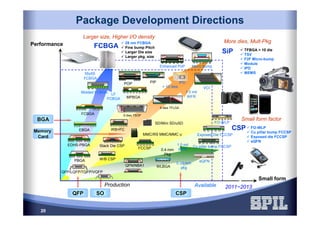

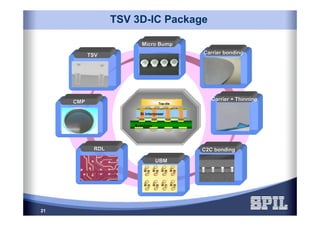

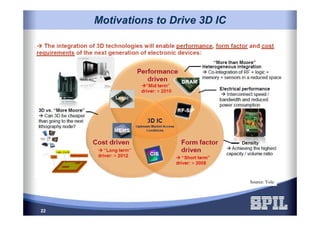

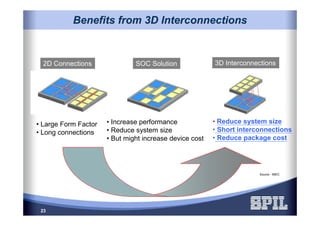

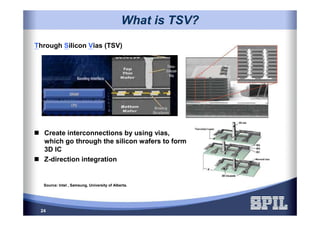

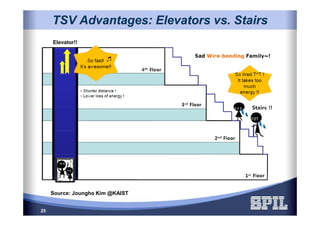

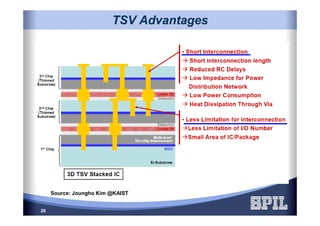

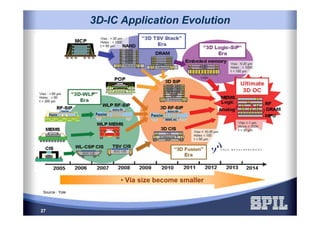

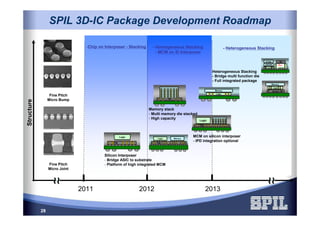

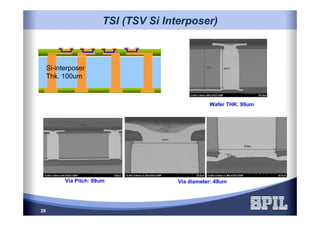

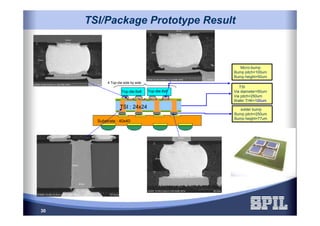

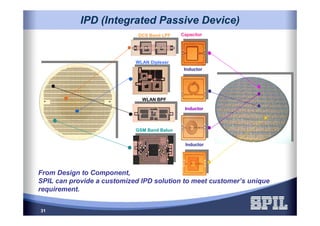

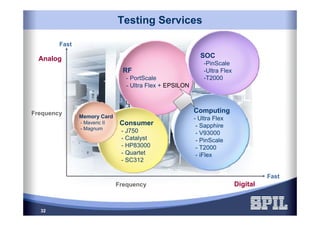

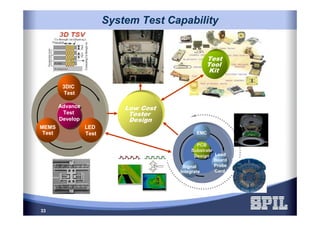

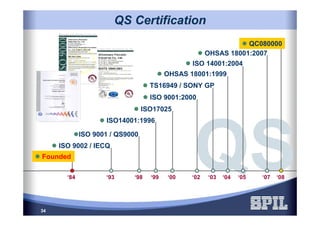

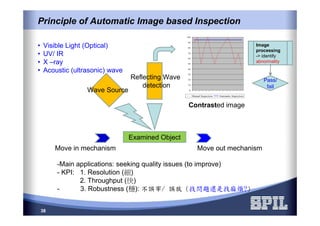

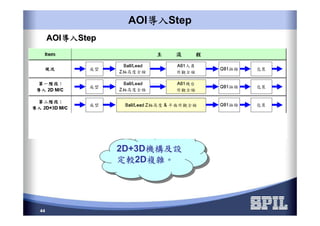

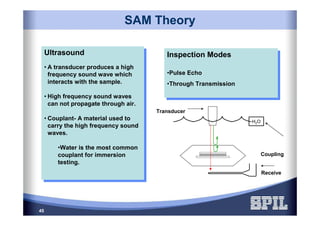

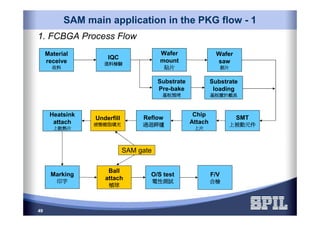

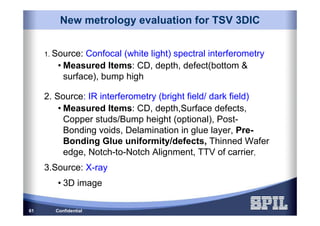

This document discusses trends in the IC packaging industry and technology. It provides an overview of the market growth in IC packaging units and revenues. Key challenges for the industry are declining ASPs and increasing materials costs. Emerging technologies discussed include wafer-level packaging, 2.5D/3D IC with TSV, and integrated passives. The document outlines SPIL's packaging portfolio and roadmaps for 3D IC and TSV development over the next few years. It also summarizes SPIL's testing and certification capabilities.