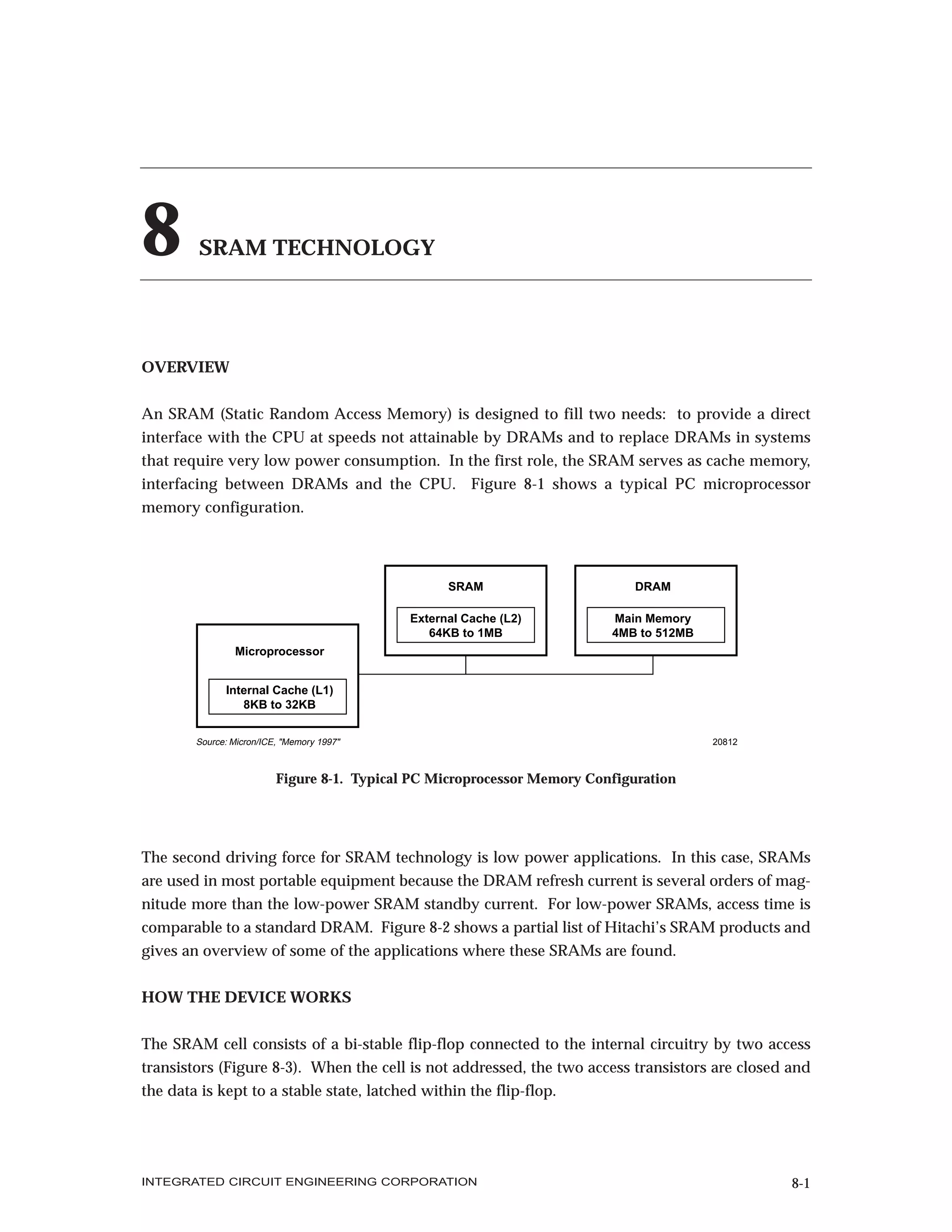

SRAM is used as cache memory interfacing between DRAM and the CPU due to its faster access speeds compared to DRAM. It is also used in low power applications where DRAM refresh currents would be too high. The SRAM cell consists of a bi-stable flip-flop connected to internal circuitry by two access transistors. To read or write data, the word line is activated, connecting the flip-flop to bit lines and sense amplifiers. The data is volatile but does not need refresh like DRAM as it does not leak over time. Different SRAM cell designs use either 4 transistors plus resistive loads or 6 transistors.