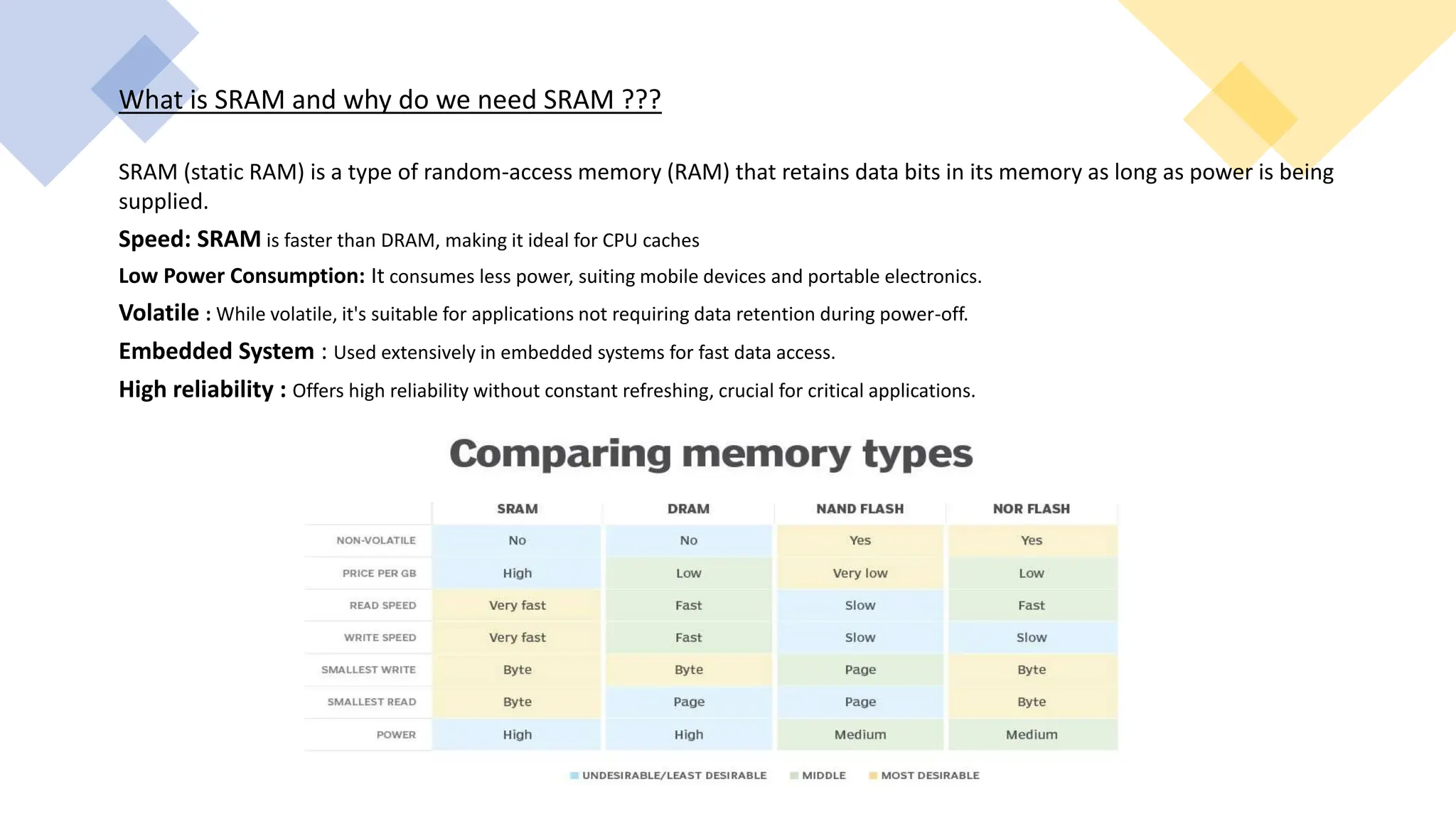

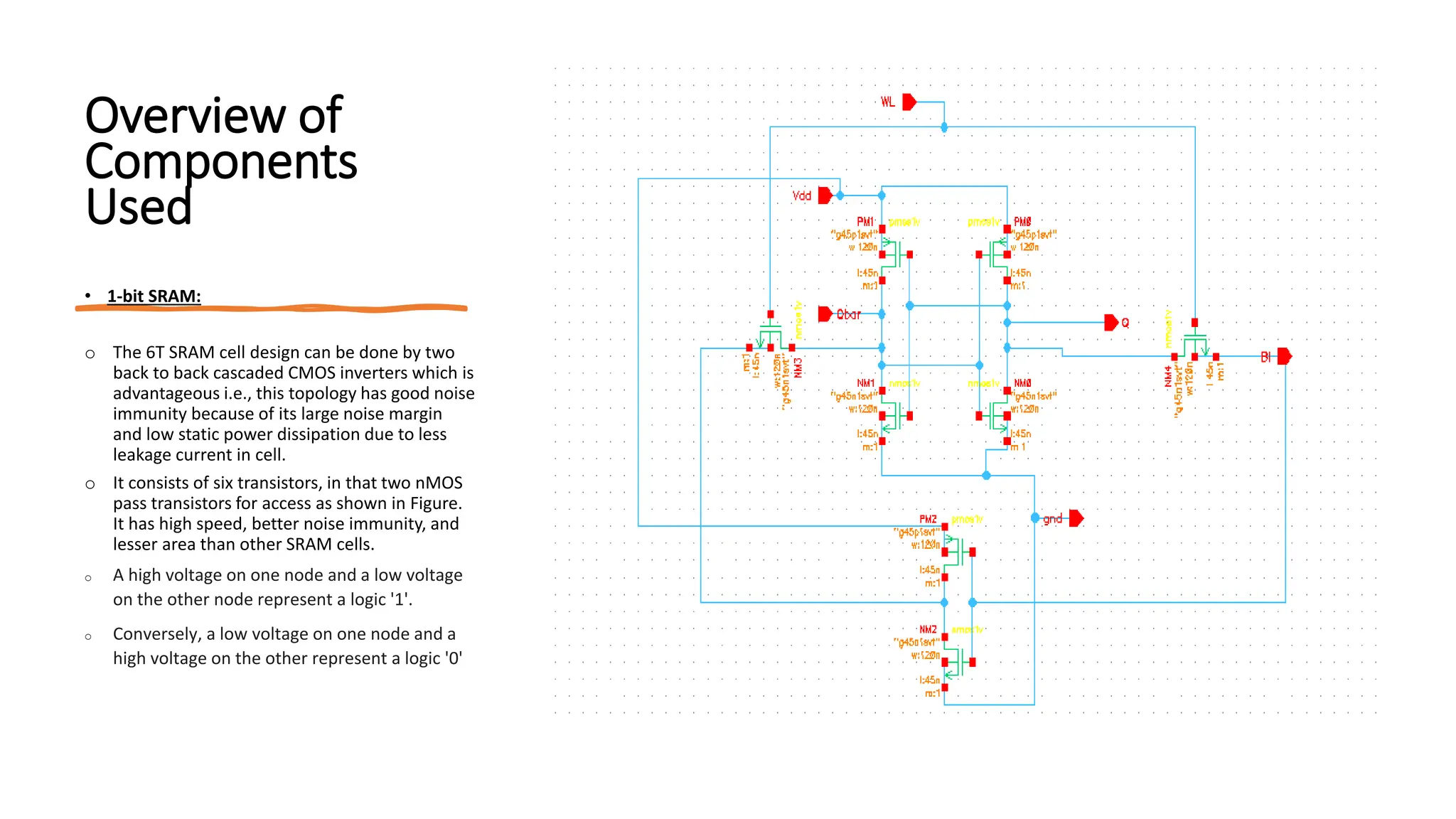

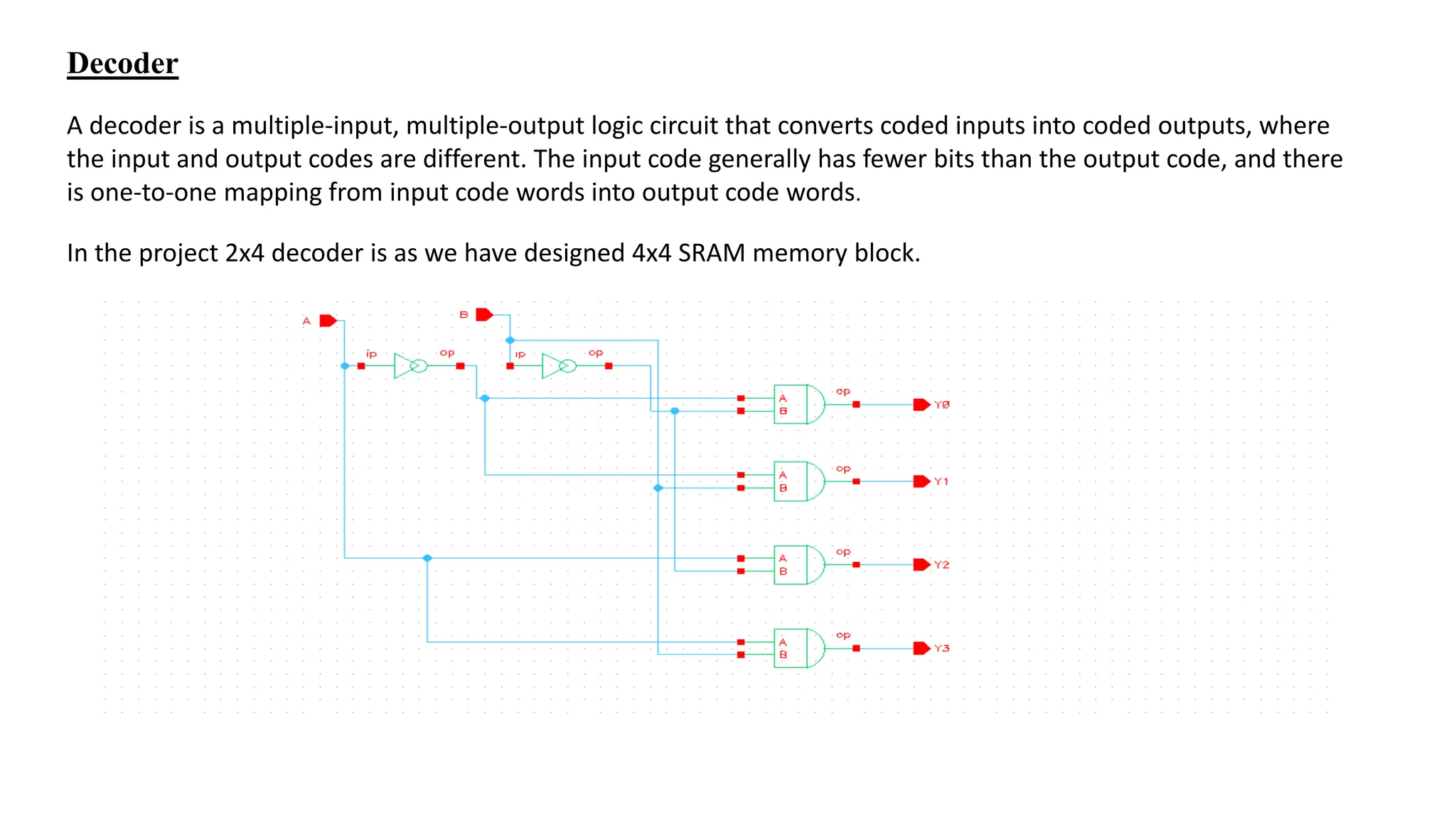

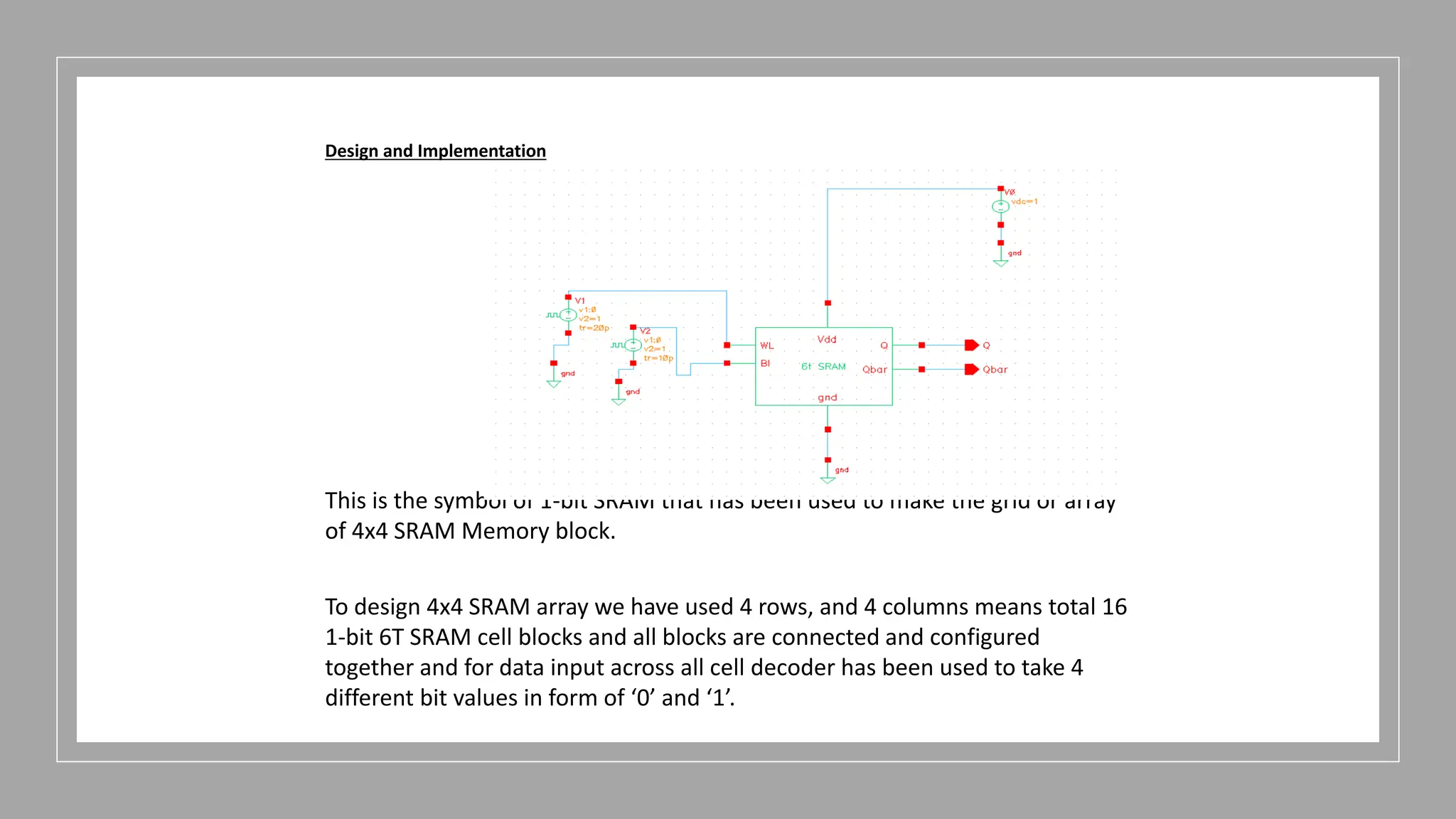

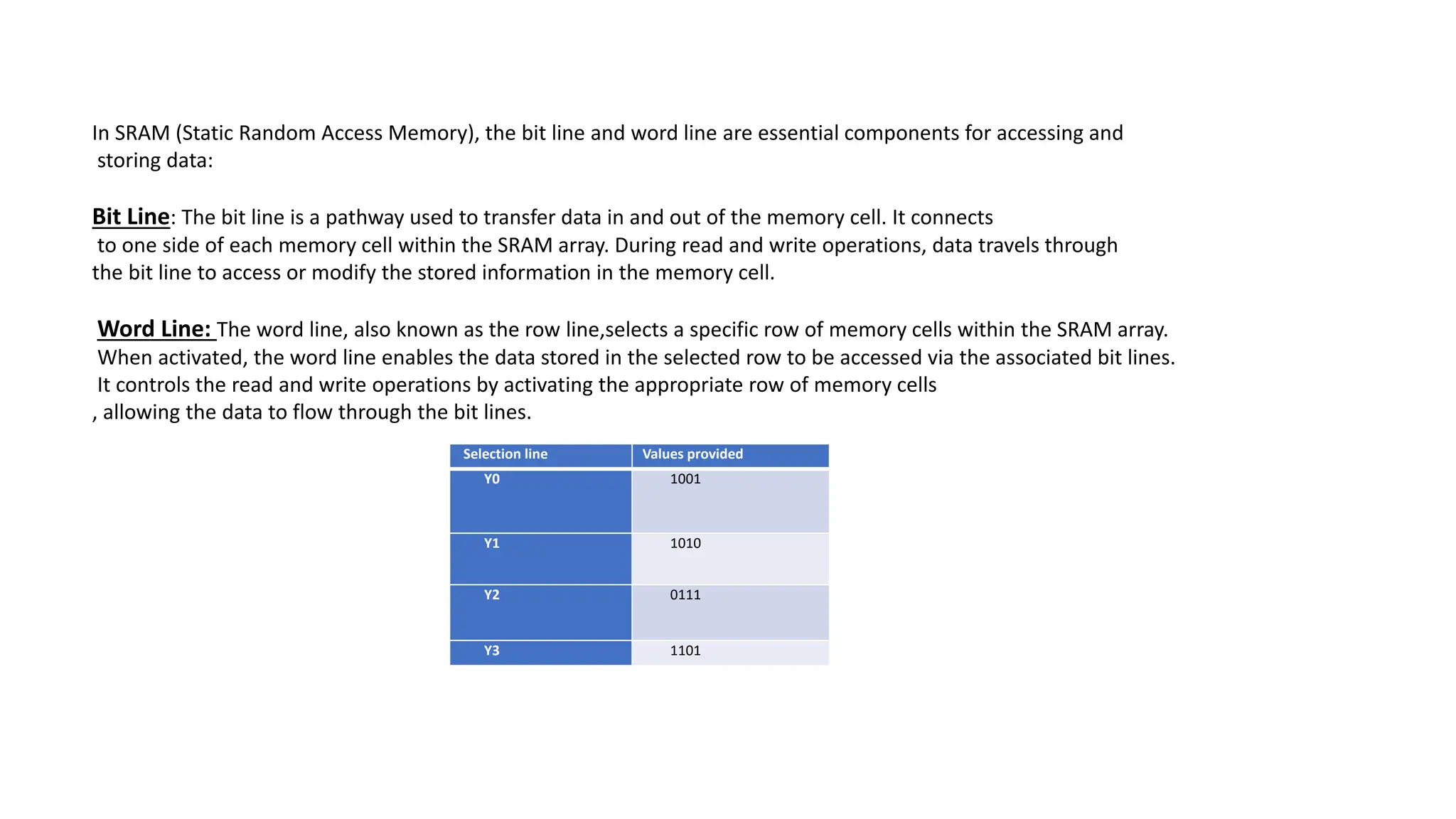

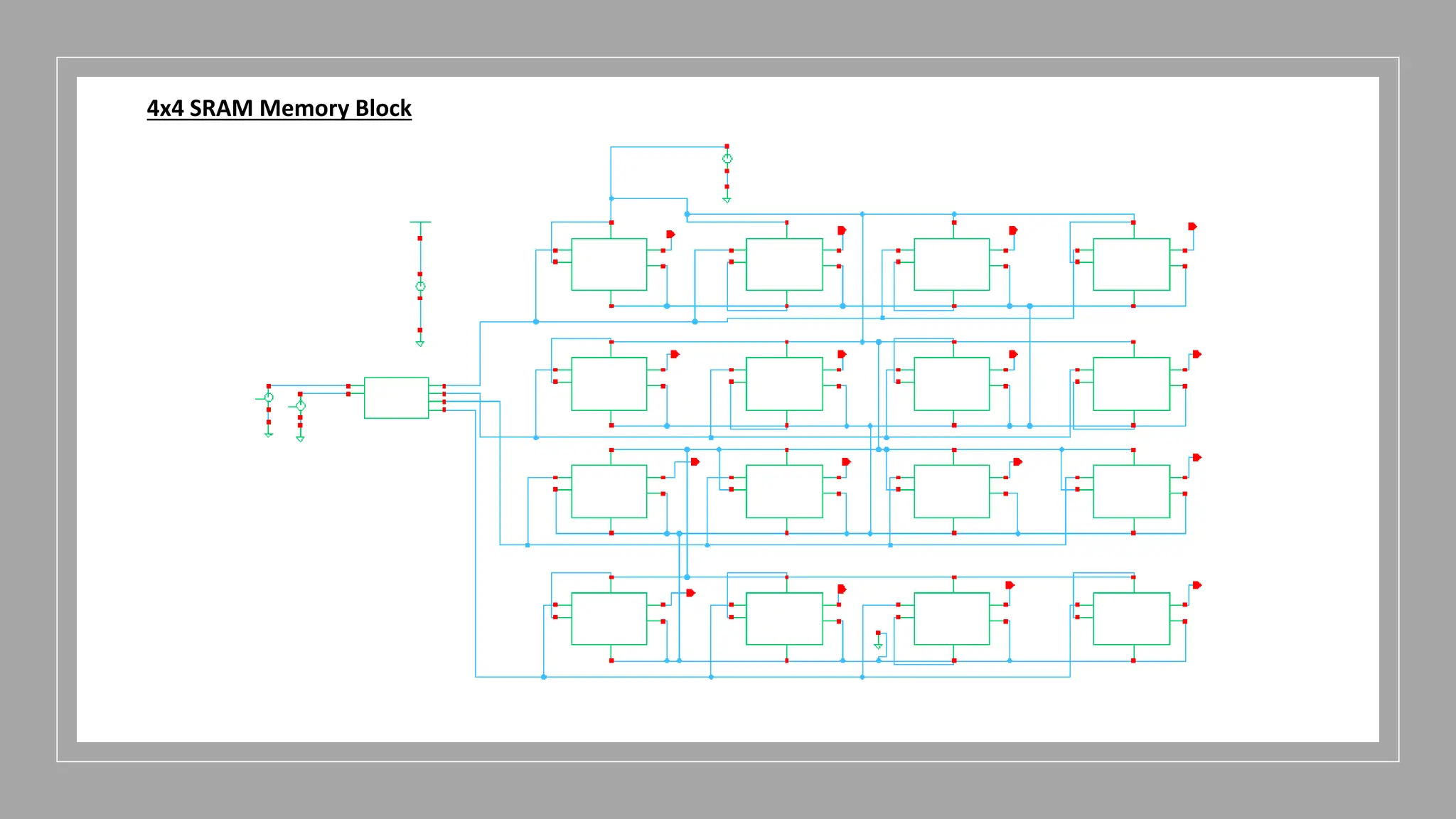

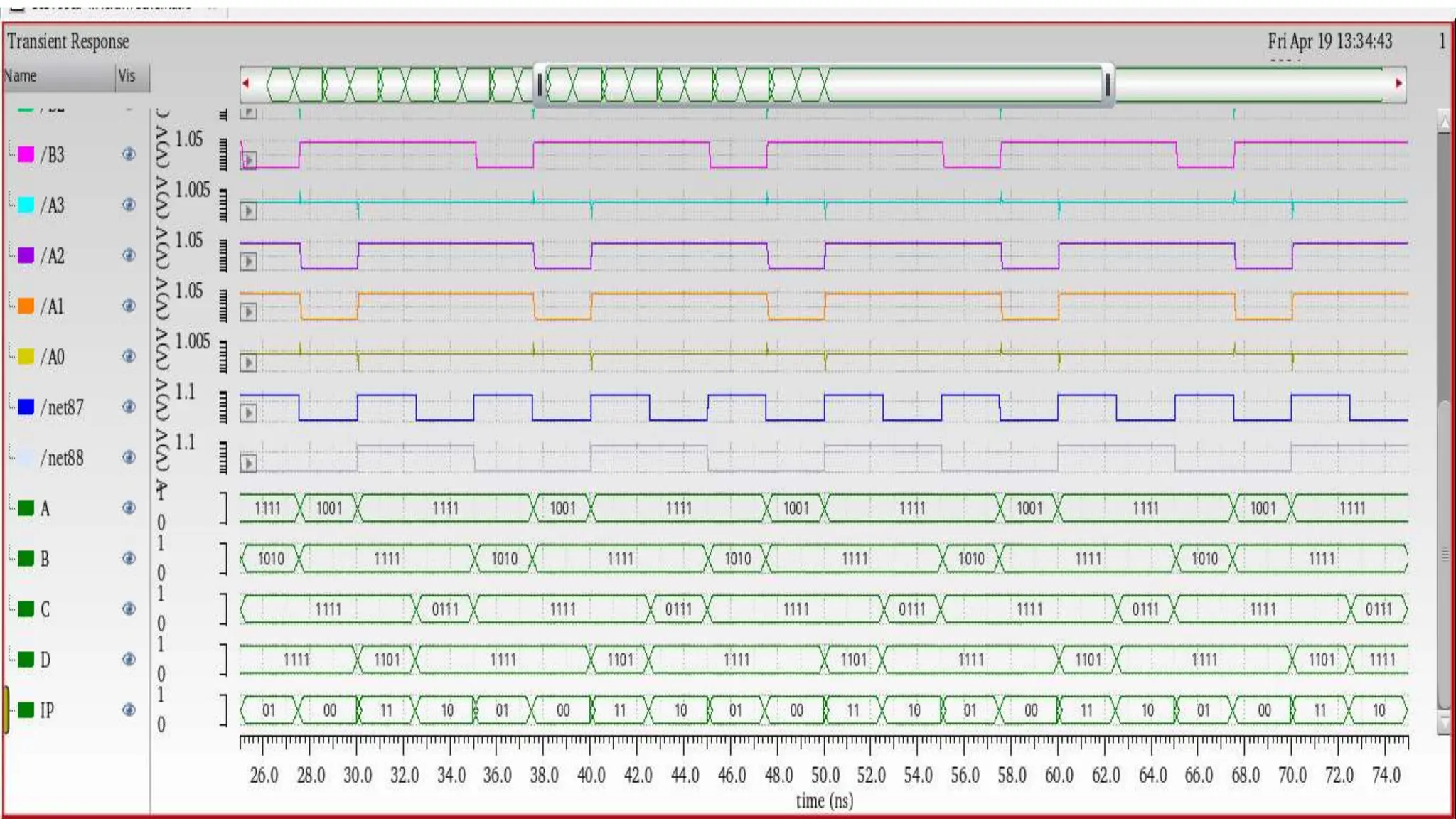

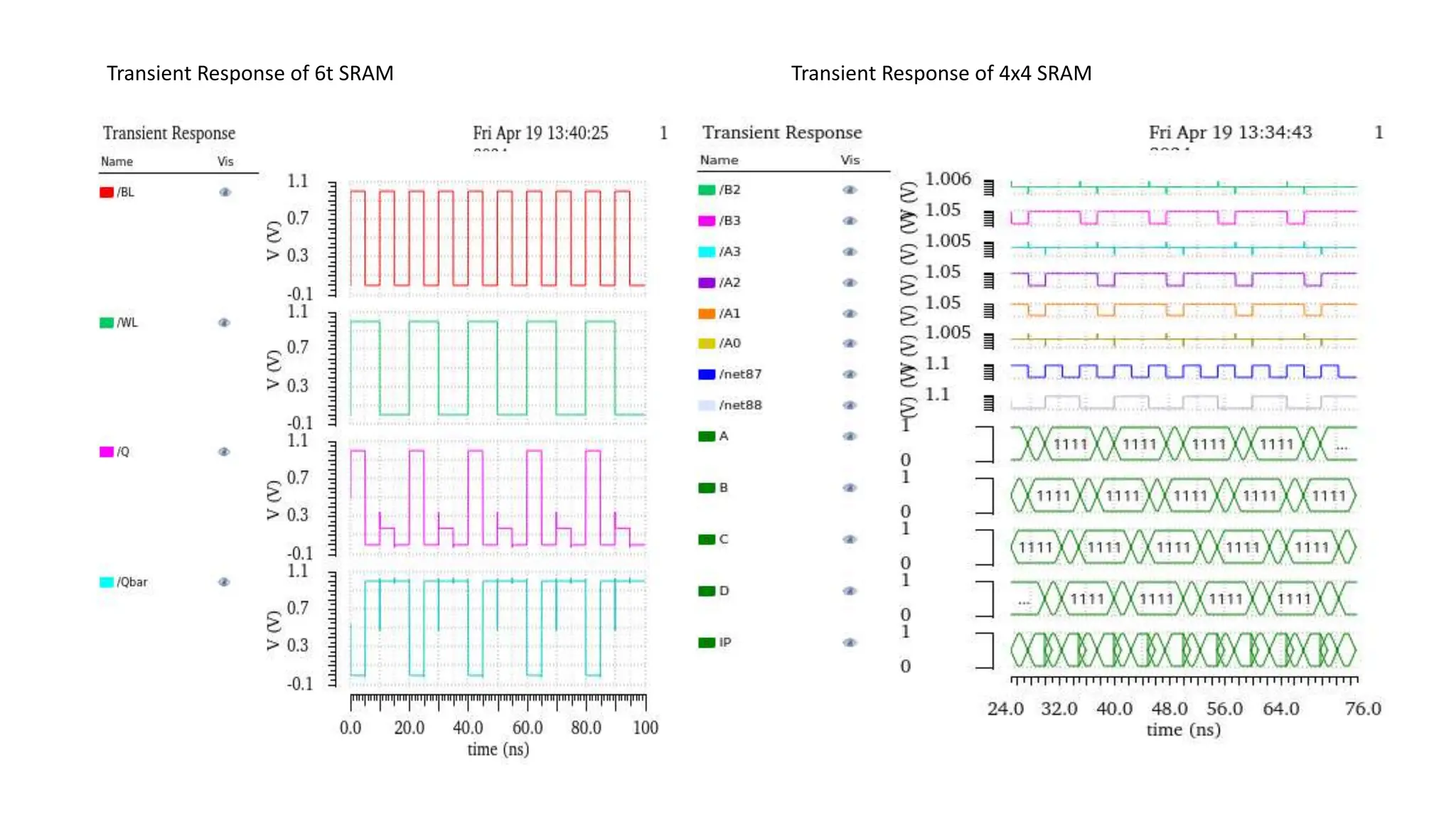

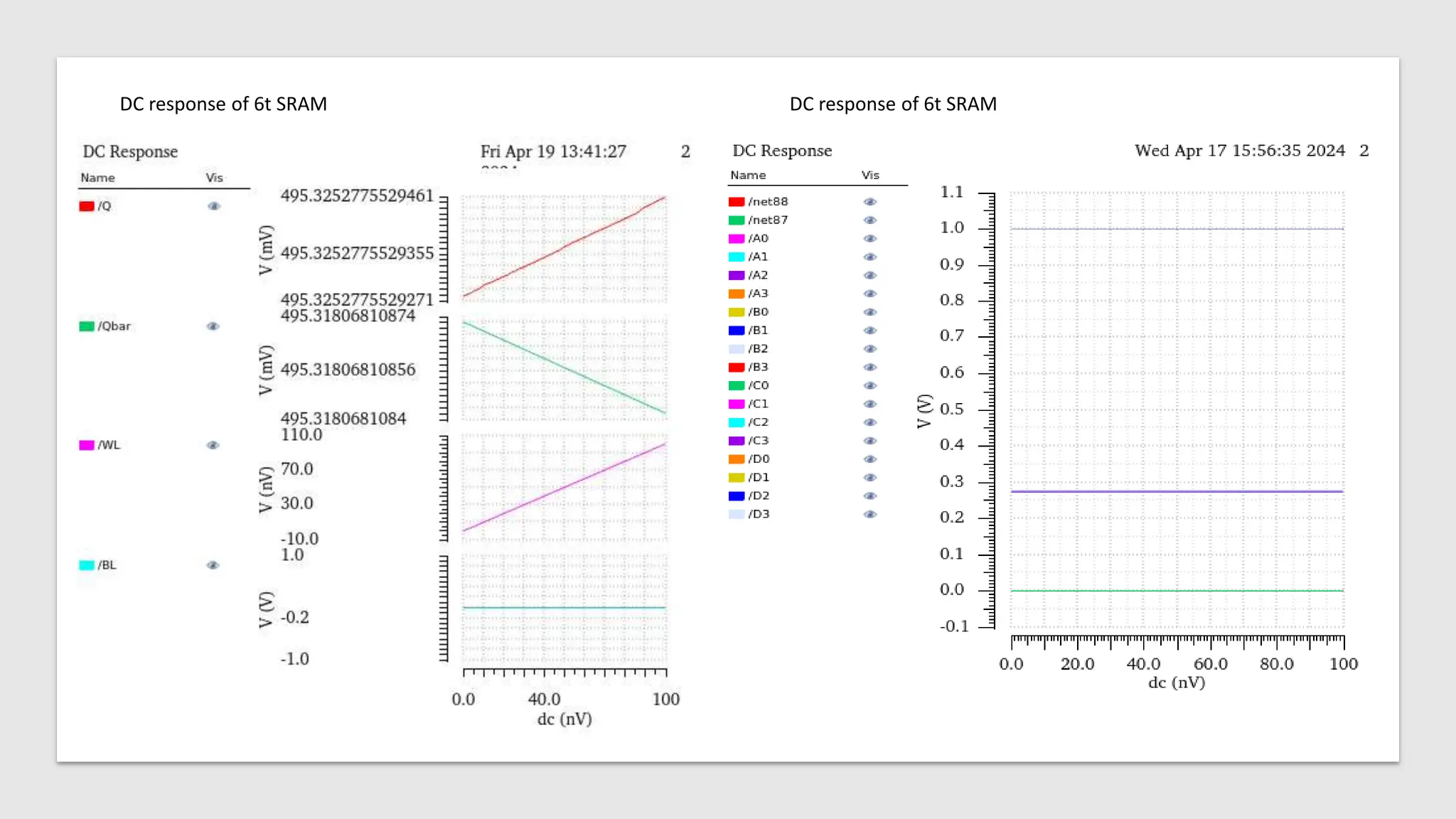

The document presents a detailed overview of a compact 4x4 SRAM memory block designed at the 45 nm node, highlighting its architecture, components, and applications in modern digital systems. It discusses the advantages of SRAM, including speed, low power consumption, and reliability, as well as the layout and design of the 4x4 SRAM array incorporating 1-bit SRAM cells. Additionally, it emphasizes the importance of power consumption, operating speed, and scalability, while suggesting future improvements for enhanced performance and reliability.