This document discusses sequential circuits and their design. It covers:

1. The difference between combinational and sequential logic and examples like finite state machines and pipelines that require sequential logic.

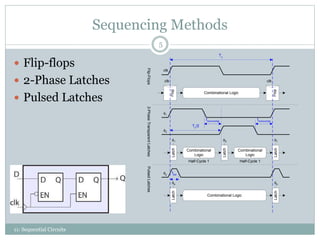

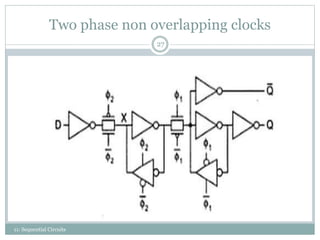

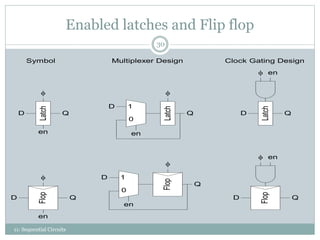

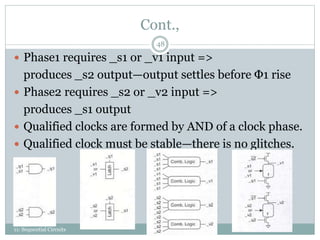

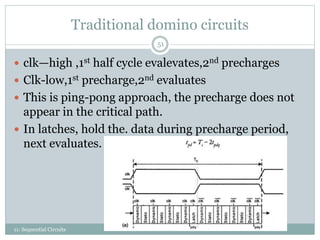

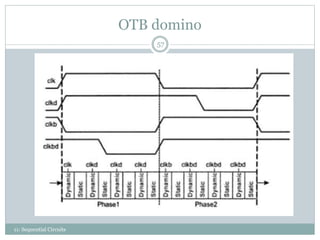

2. Methods for sequencing tokens through pipelines using flip-flops, latches, and pulsed latches and the associated timing diagrams.

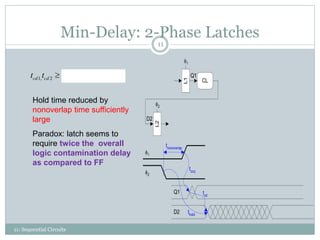

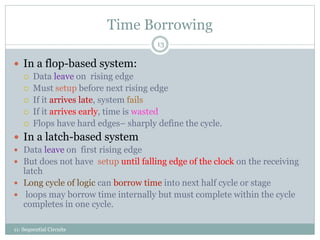

3. Design considerations for sequential circuits like max/min delays, time borrowing, and clock skew.

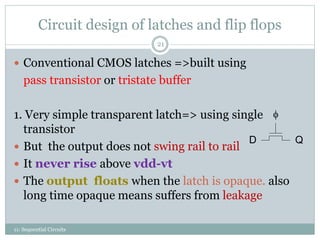

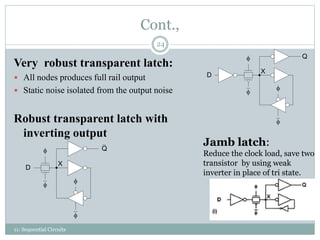

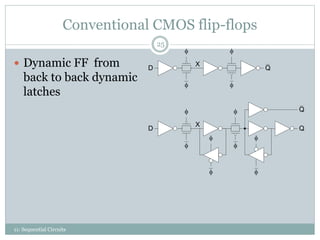

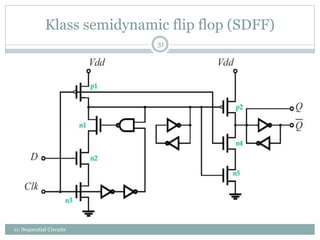

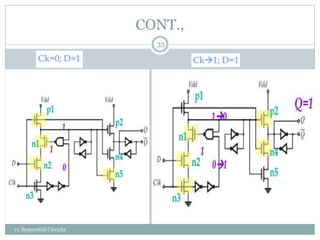

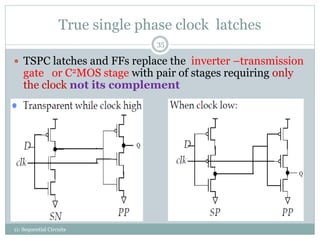

4. Circuit designs for various latches and flip-flops including transparent latches, CMOS transmission gate latches, dynamic flip-flops, and true single phase clock elements.