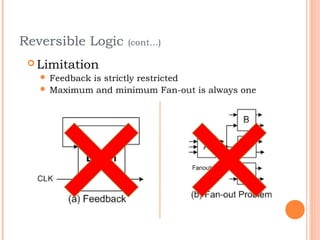

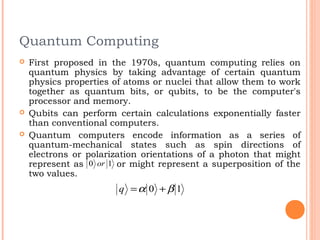

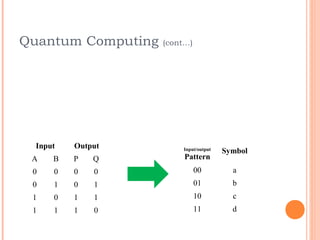

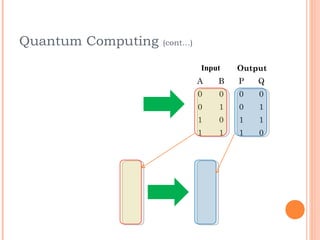

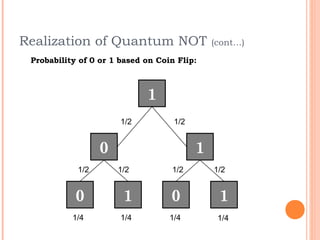

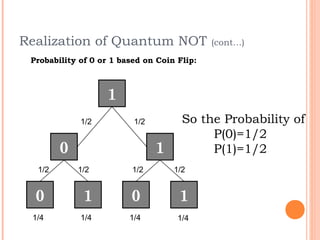

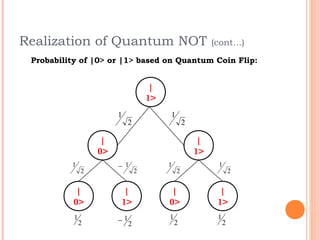

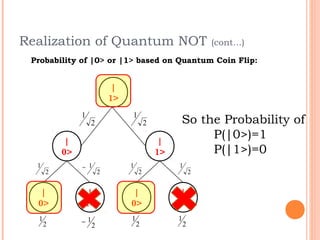

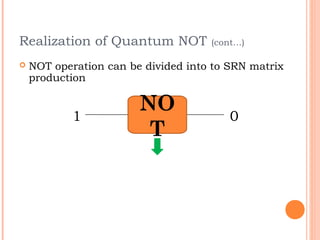

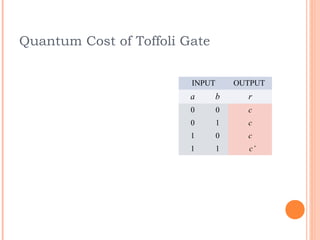

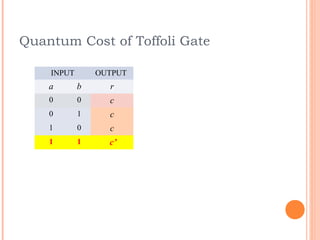

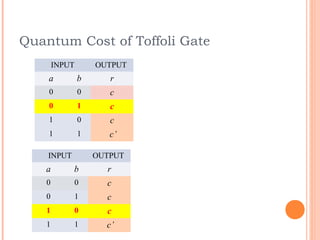

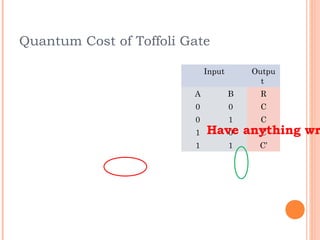

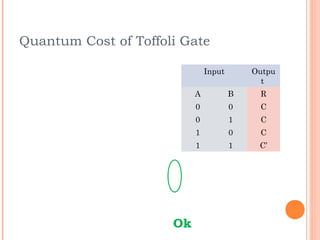

This document discusses the calculation of quantum cost for reversible circuits. It begins with an overview of reversible logic and quantum computing concepts like quantum gates. It then explains the realization of quantum NOT gate using quantum coin flips. Different quantum gates and their quantum costs are discussed, including Toffoli, Fredkin, Peres and NFT gates. Special cases involving quantum wires that have zero cost are also covered. The document concludes with an assignment to find the cost of additional gates and provides information about the author.