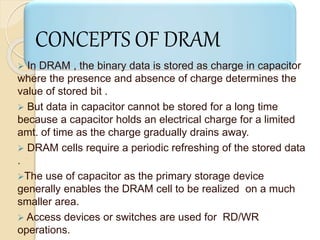

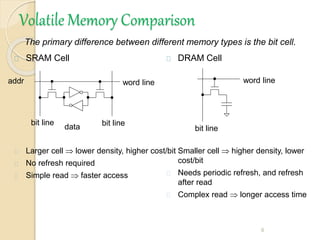

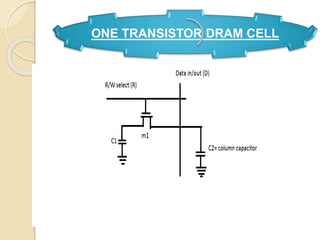

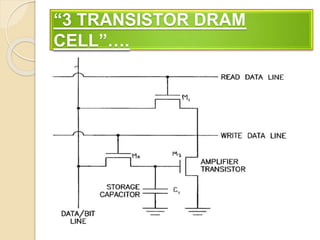

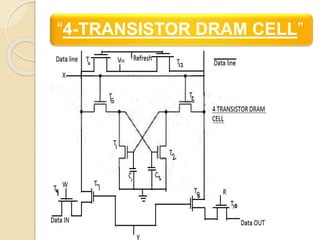

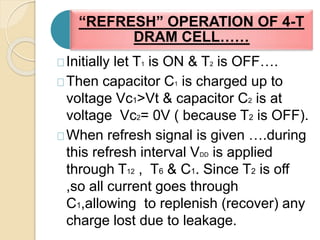

The document discusses Dynamic Random Access Memory (DRAM). DRAM uses a capacitor and transistor to store each bit of data, which allows it to be implemented using less space than SRAM. However, DRAM is volatile and requires periodic refreshing to prevent data loss as the capacitor charge leaks over time. Common DRAM configurations include one transistor cells, three transistor cells, and four transistor cells. The document outlines the read and write operations for DRAM and how refreshing maintains the stored data.