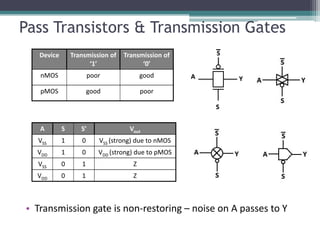

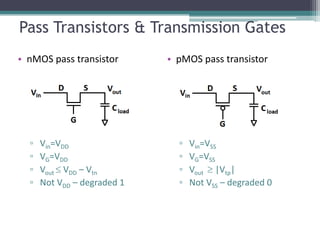

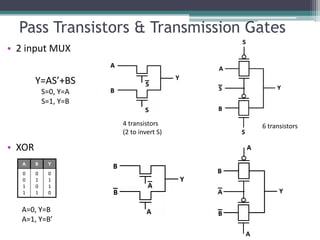

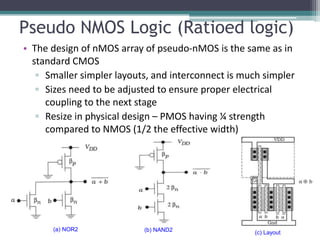

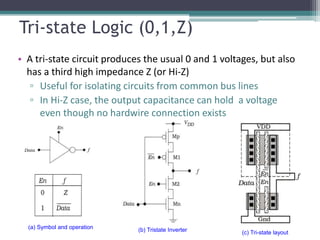

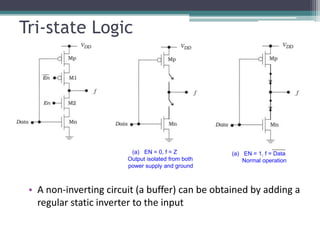

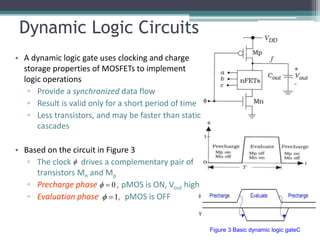

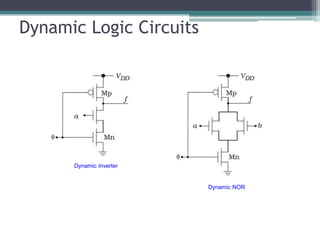

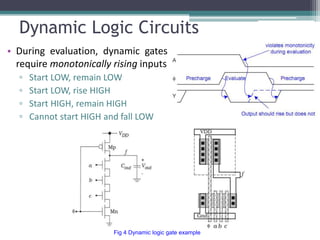

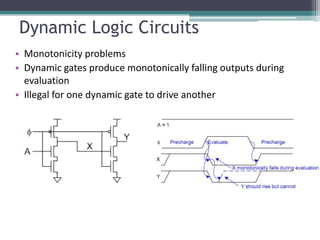

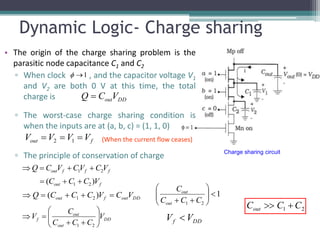

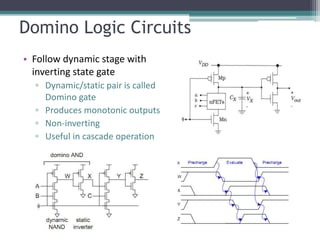

The document outlines various VLSI combinational logic circuit design techniques, including pass transistors, transmission gates, pseudo NMOS logic, tri-state logic, dynamic logic, and domino logic. Each technique is described in terms of its operational characteristics, circuit configurations, and advantages, such as reduced transistor count and improved isolation in state circuits. Additionally, it discusses the implications of dynamic logic designs and issues like charge sharing and monotonicity in outputs.