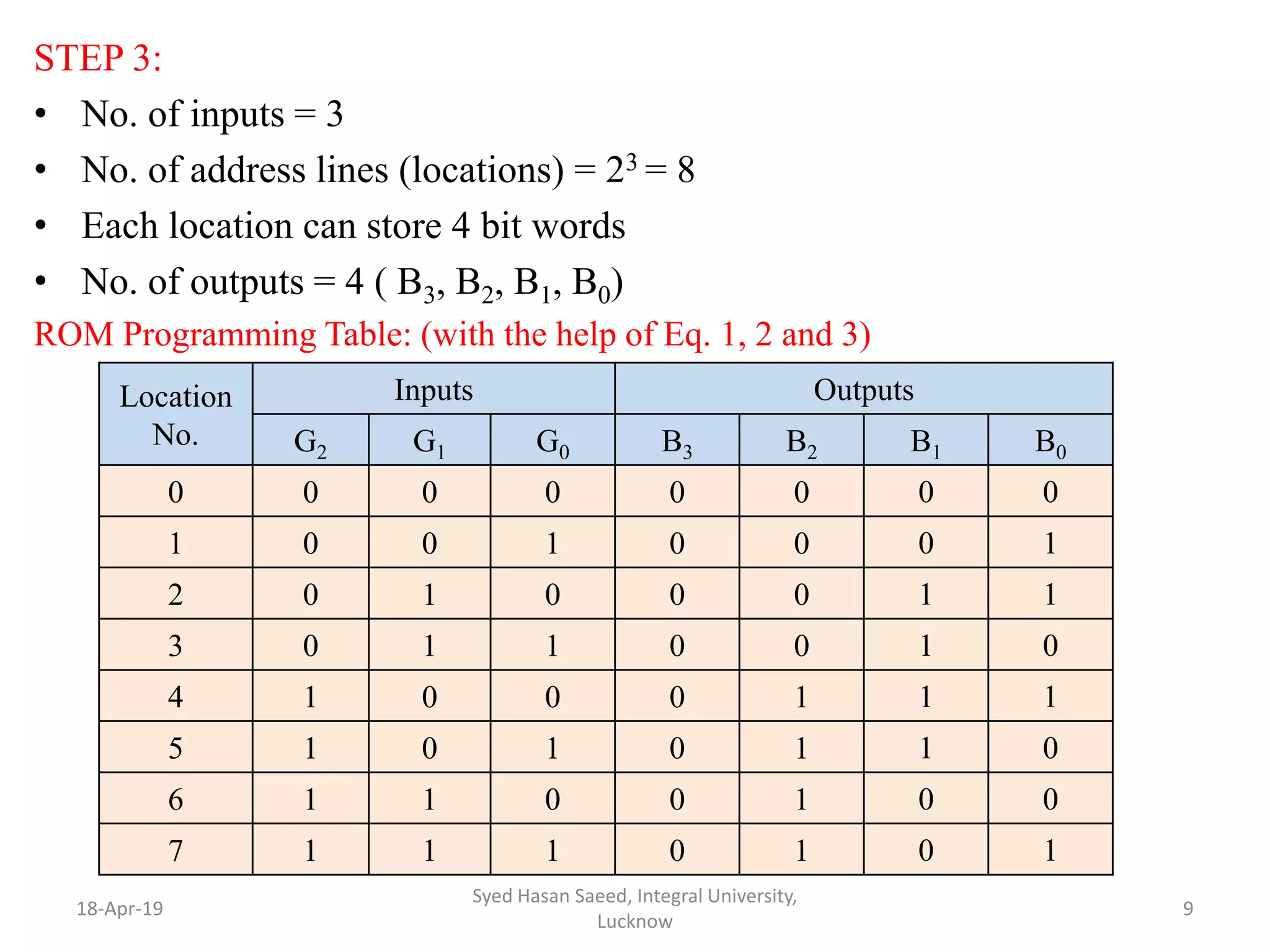

Programmable Read Only Memory (PROM) can be used as a programmable logic device or memory. As a programmable logic device, PROM uses AND gates as inputs to generate all possible combinations, and programmable OR gates to select the desired output combinations. It has 2n AND gates and m OR gates, where n is the number of inputs and m is the number of outputs. An example shows how an 8x2 PROM can be used to implement two Boolean functions of three variables. PROM can also be used as a memory device, where it stores m-bit data words at 2n address locations.