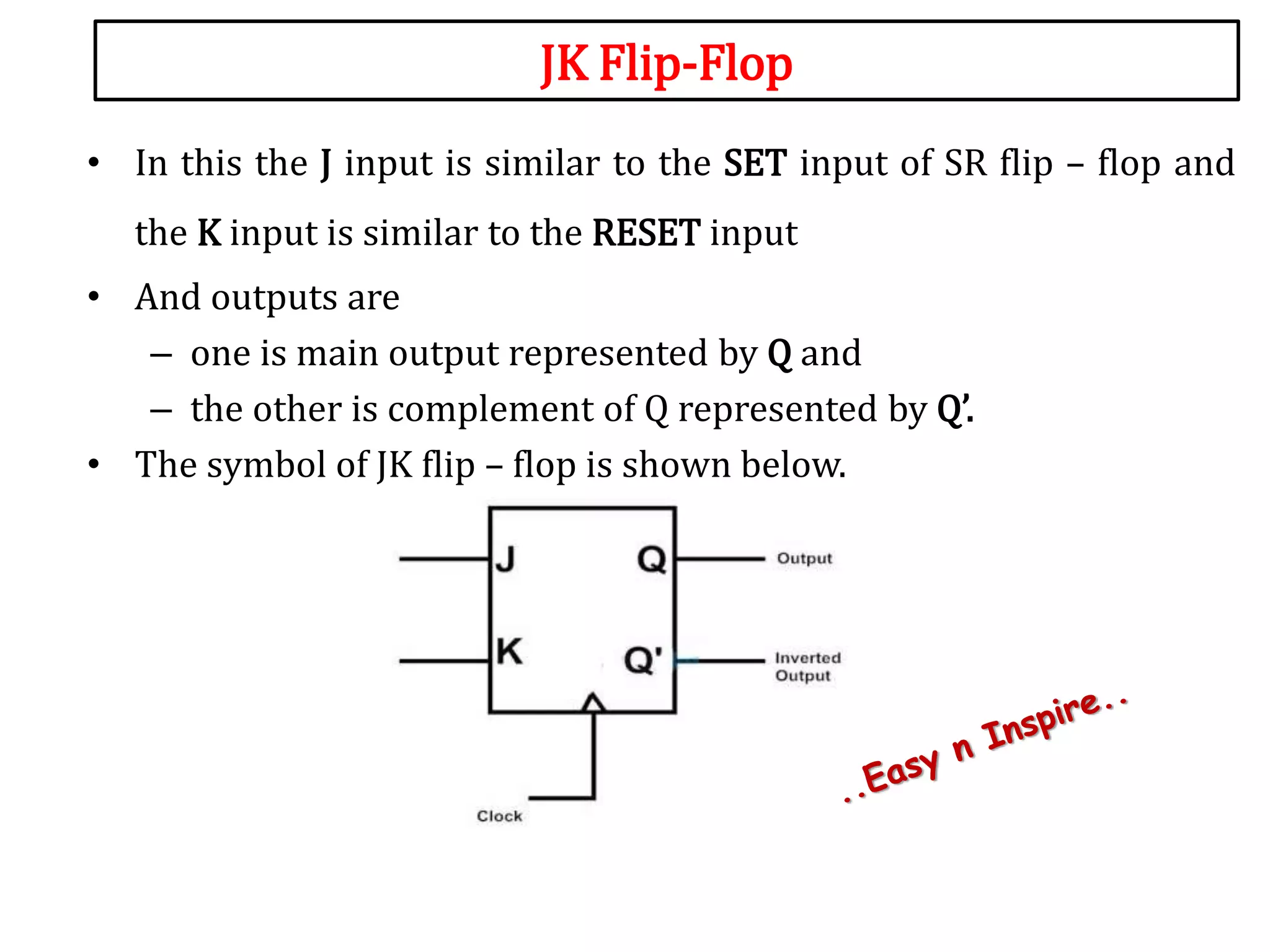

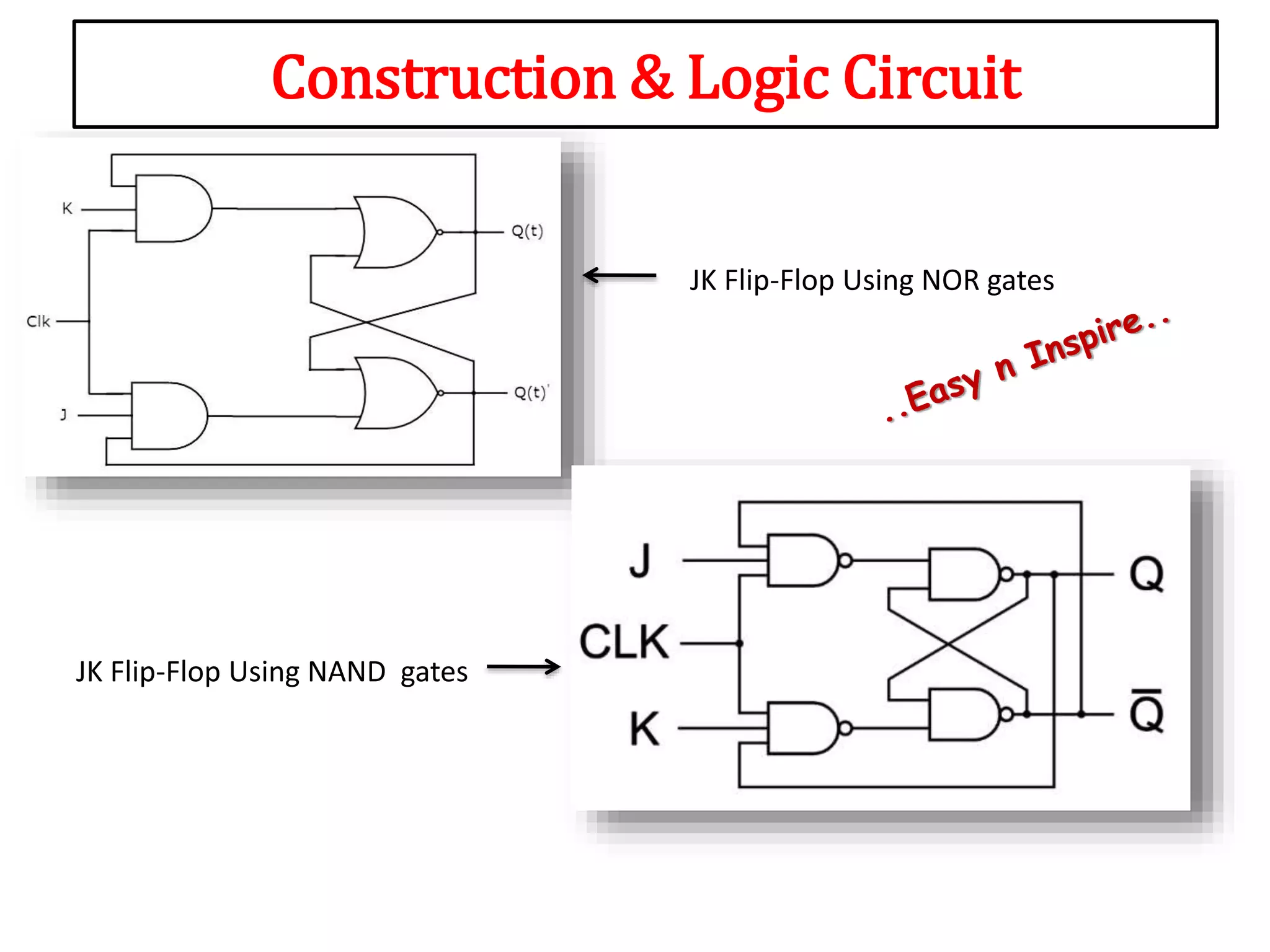

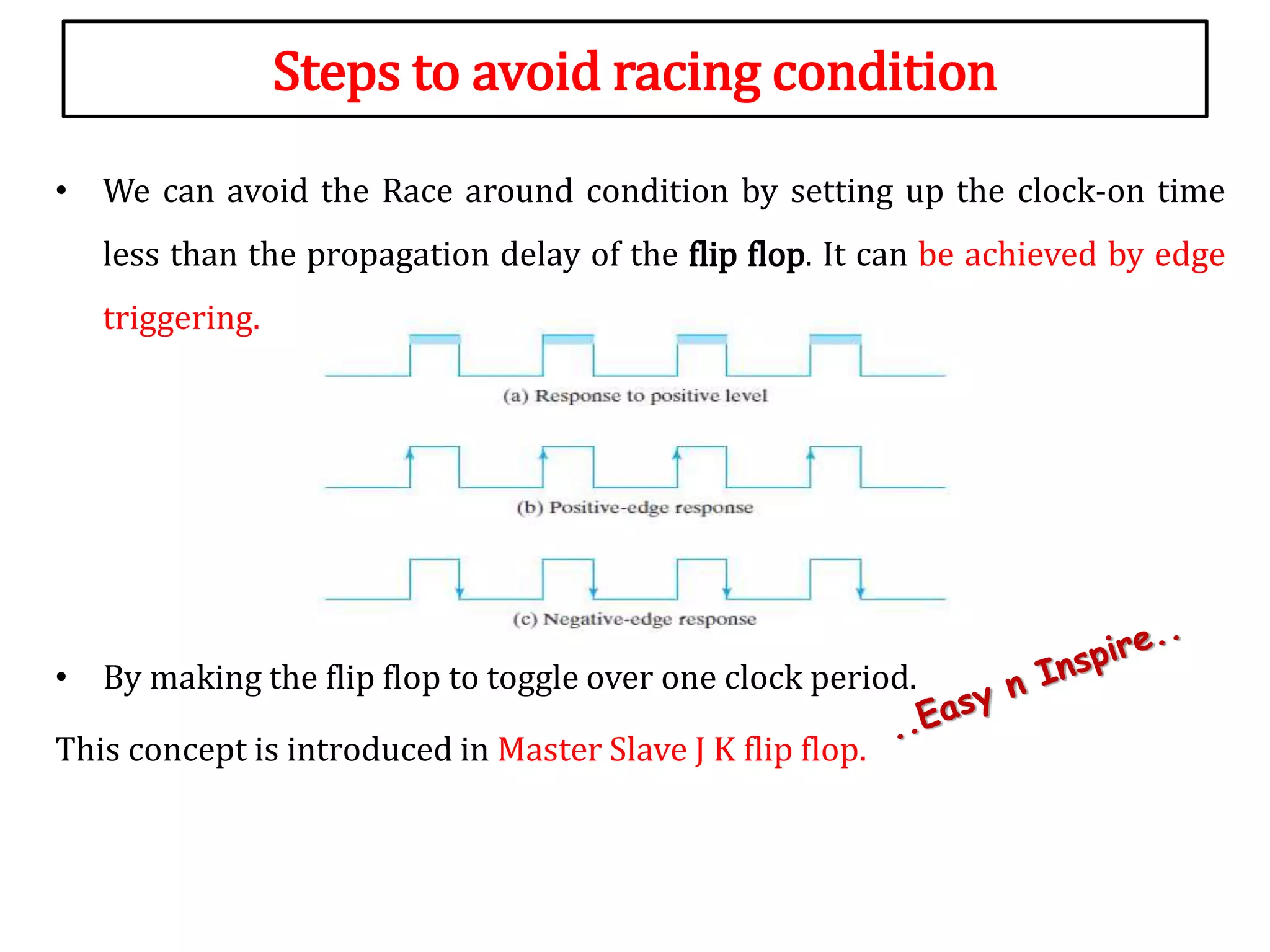

The document explains the JK flip-flop, a type of sequential logic circuit that is a modification of the SR flip-flop, eliminating invalid states. It serves as a universal programmable flip-flop, where the J and K inputs behave as set and reset inputs, with toggling behavior dependent on clock signals. Additionally, it addresses issues such as the race around condition and methods to prevent it, including using edge triggering in a master-slave configuration.