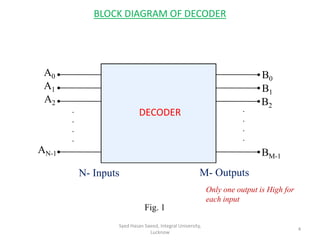

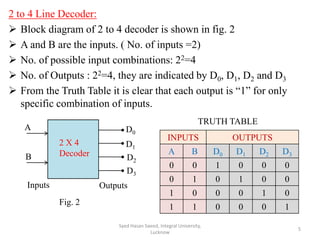

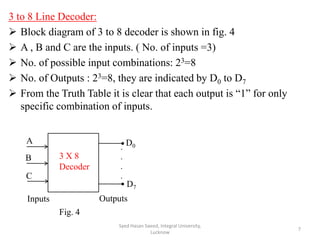

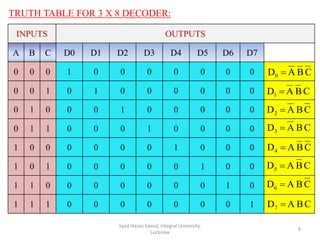

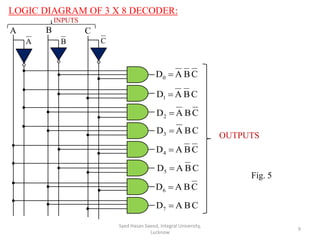

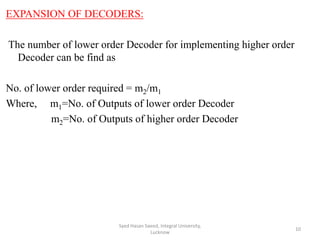

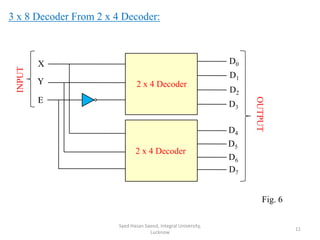

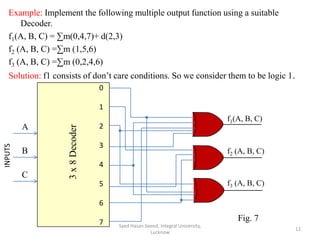

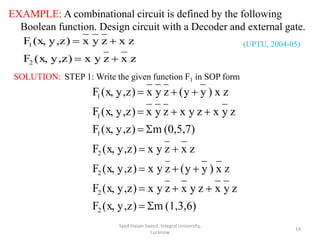

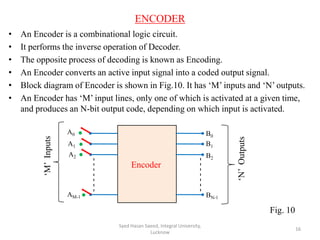

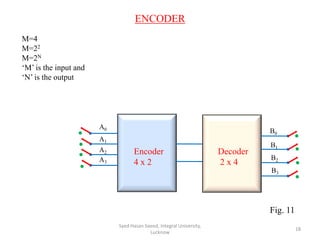

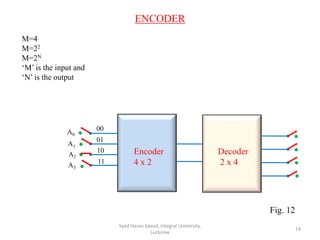

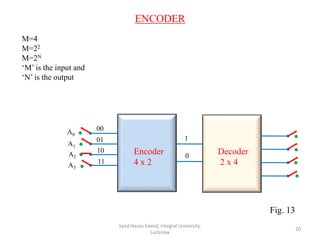

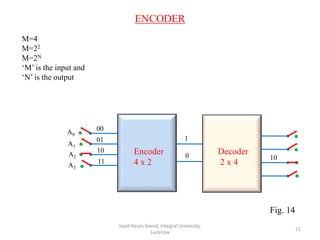

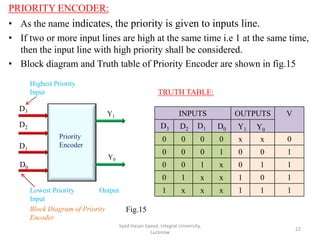

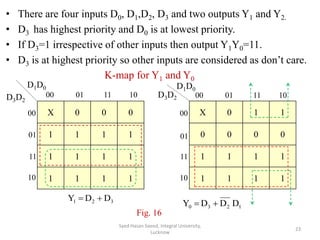

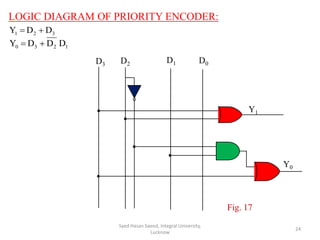

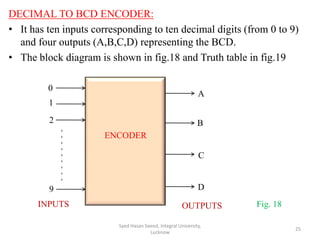

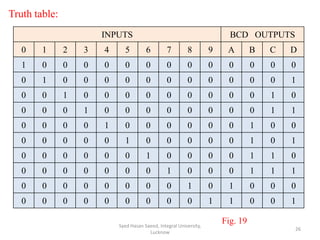

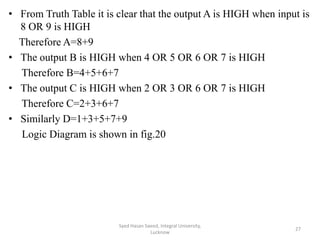

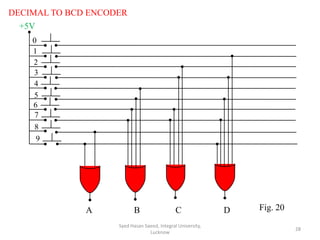

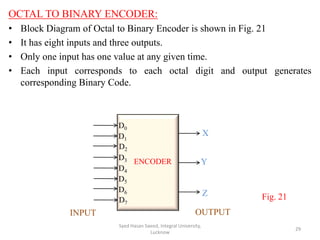

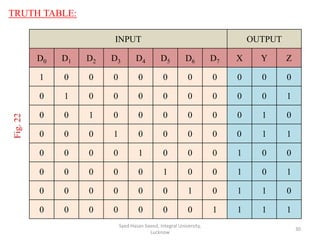

This document discusses decoders and encoders. It defines a decoder as a circuit that accepts a binary input and activates only one output corresponding to the input. An encoder is the inverse, converting an active input to a coded output. Various types of decoders and encoders are described, including 2-to-4 decoders, 3-to-8 decoders, priority encoders, decimal-to-BCD encoders, and octal-to-binary encoders. Truth tables and logic diagrams are provided as examples. Expansion of decoders using multiple lower-order decoders is also covered.