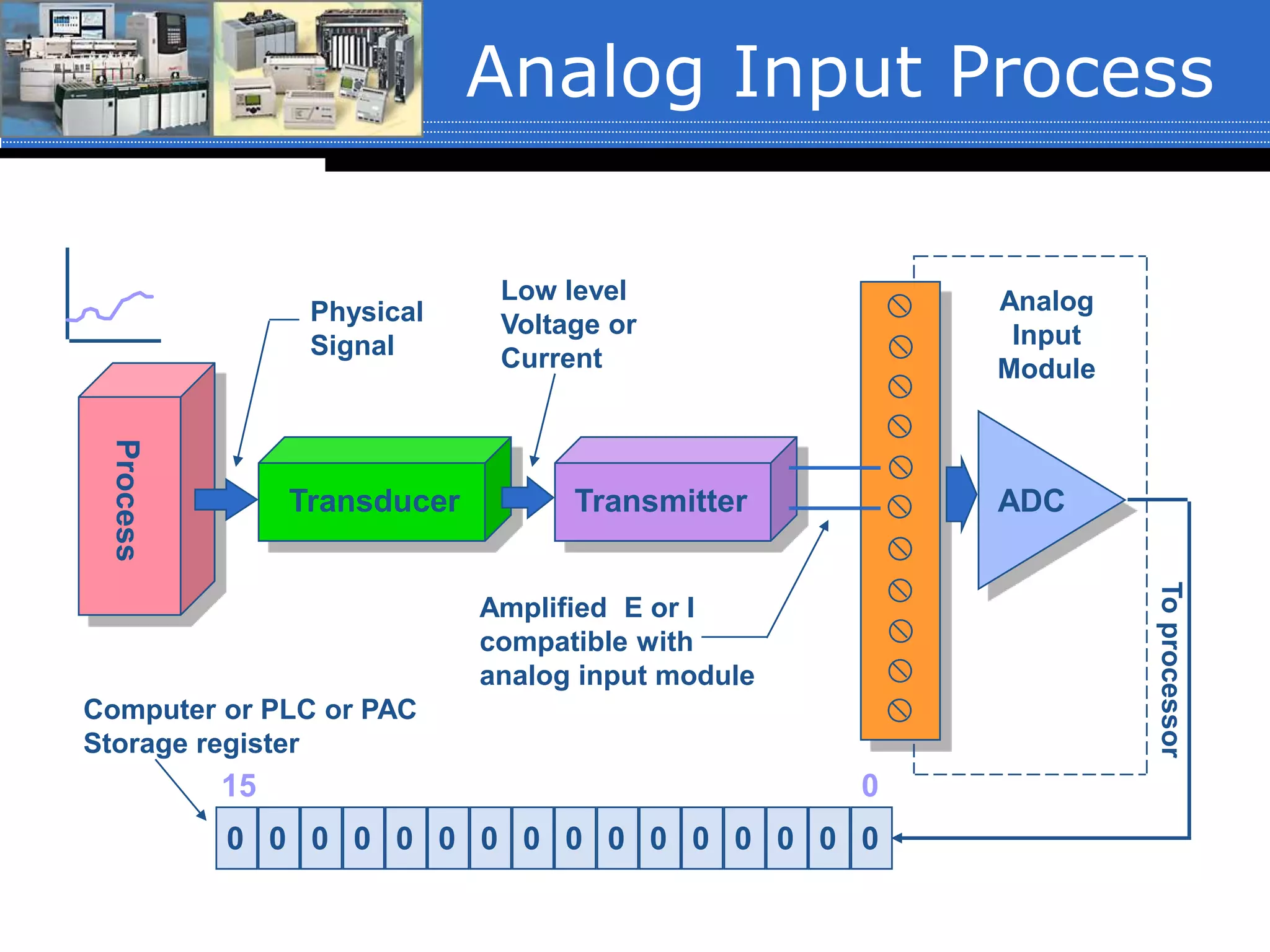

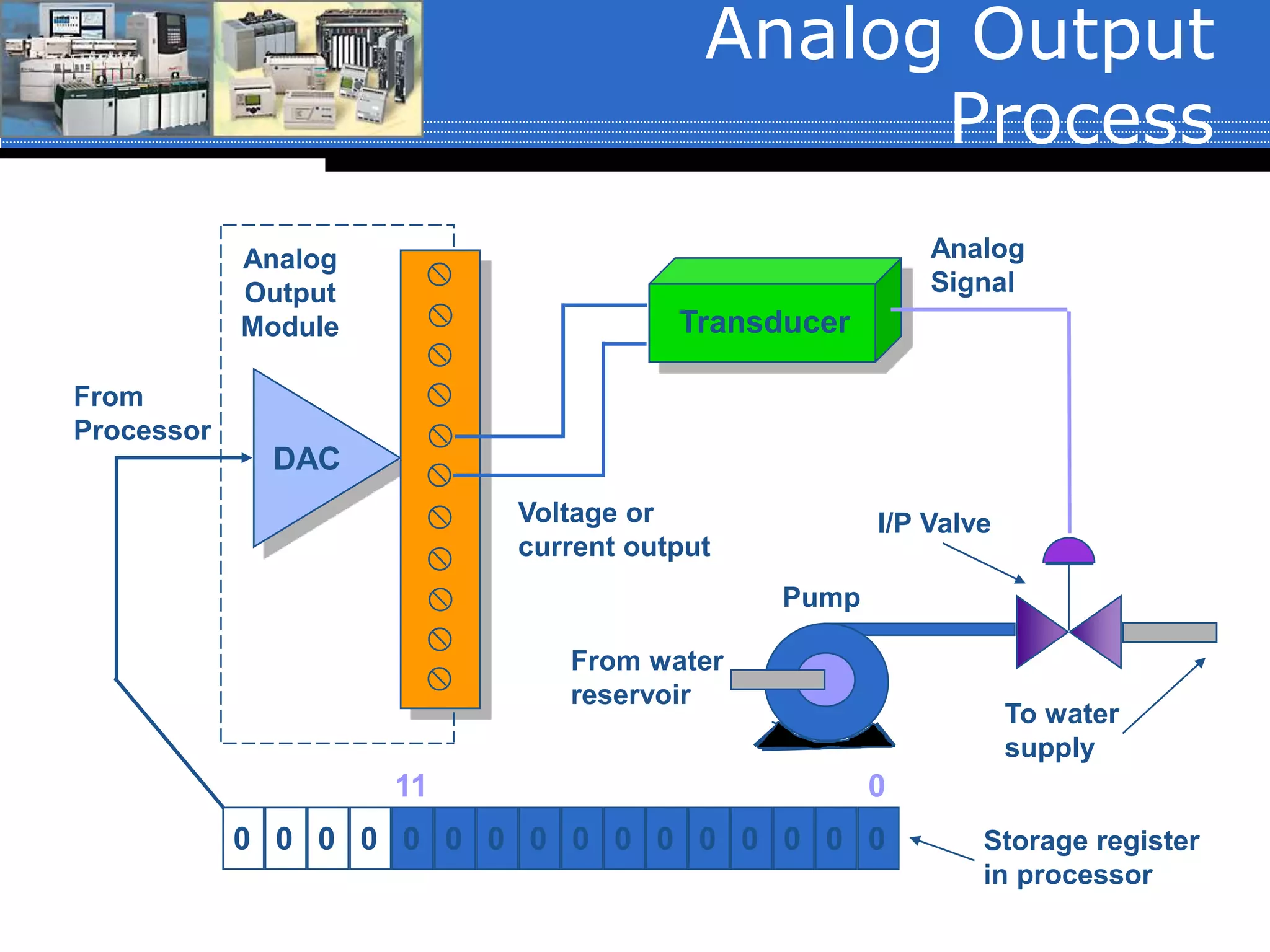

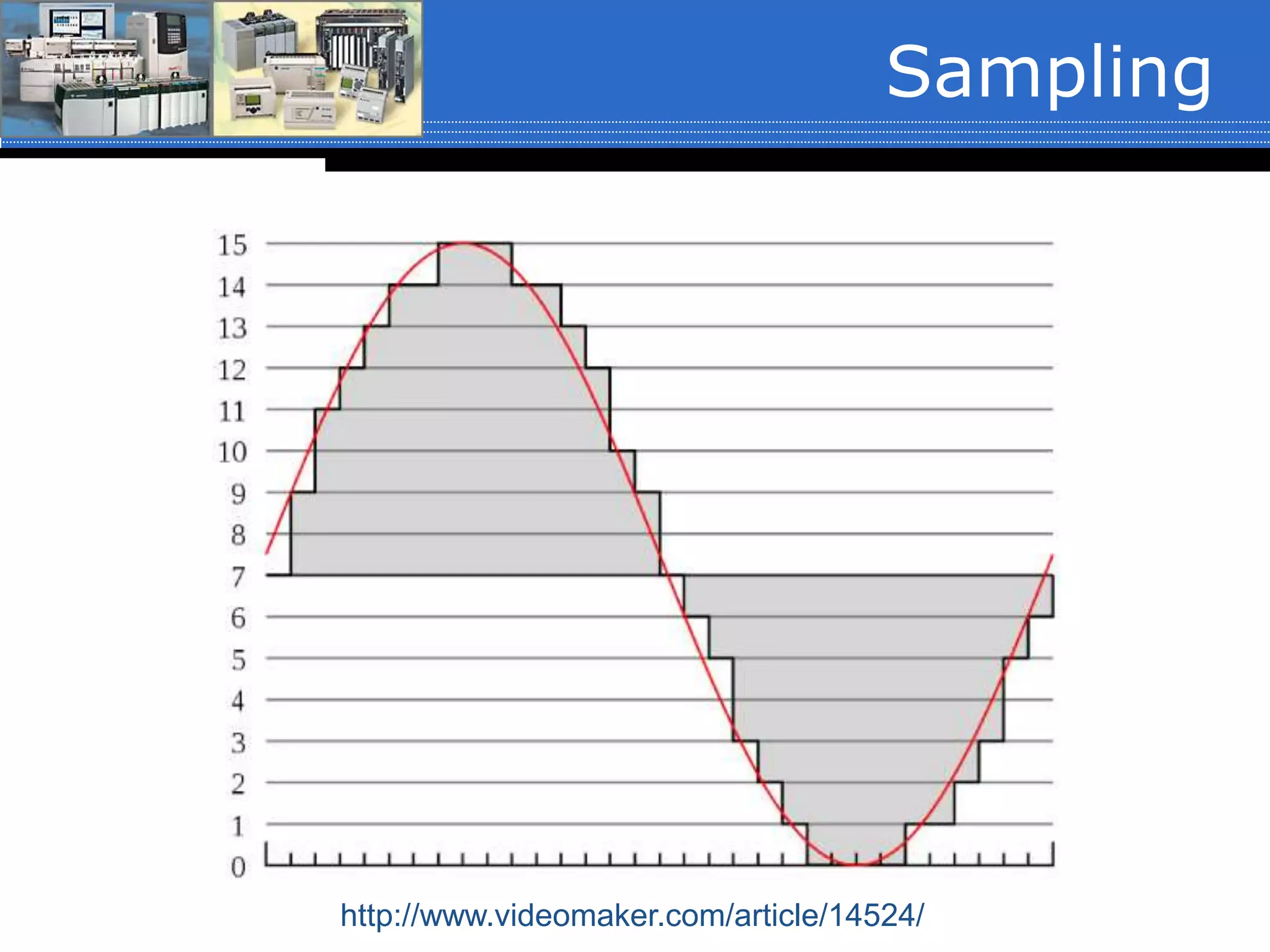

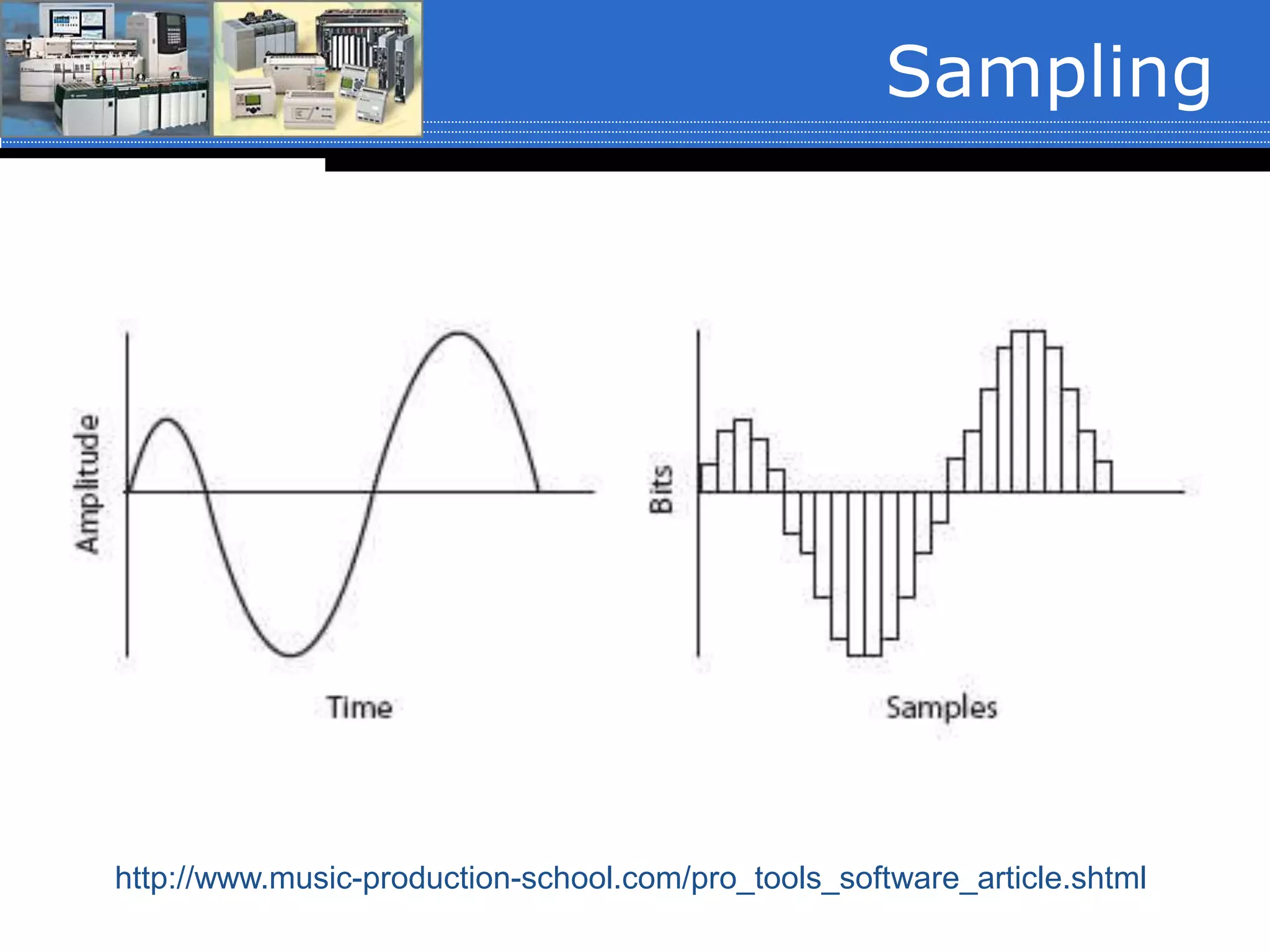

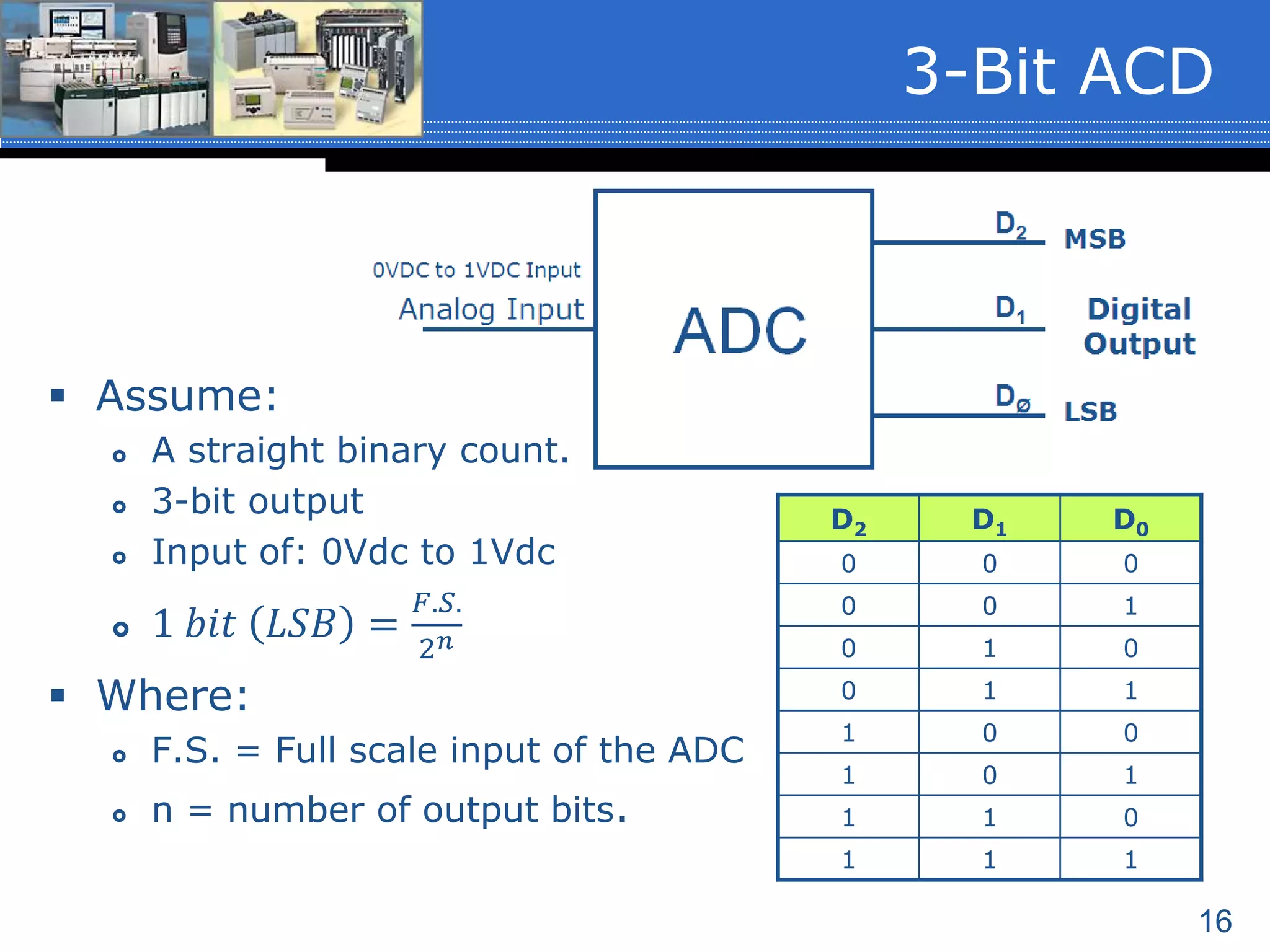

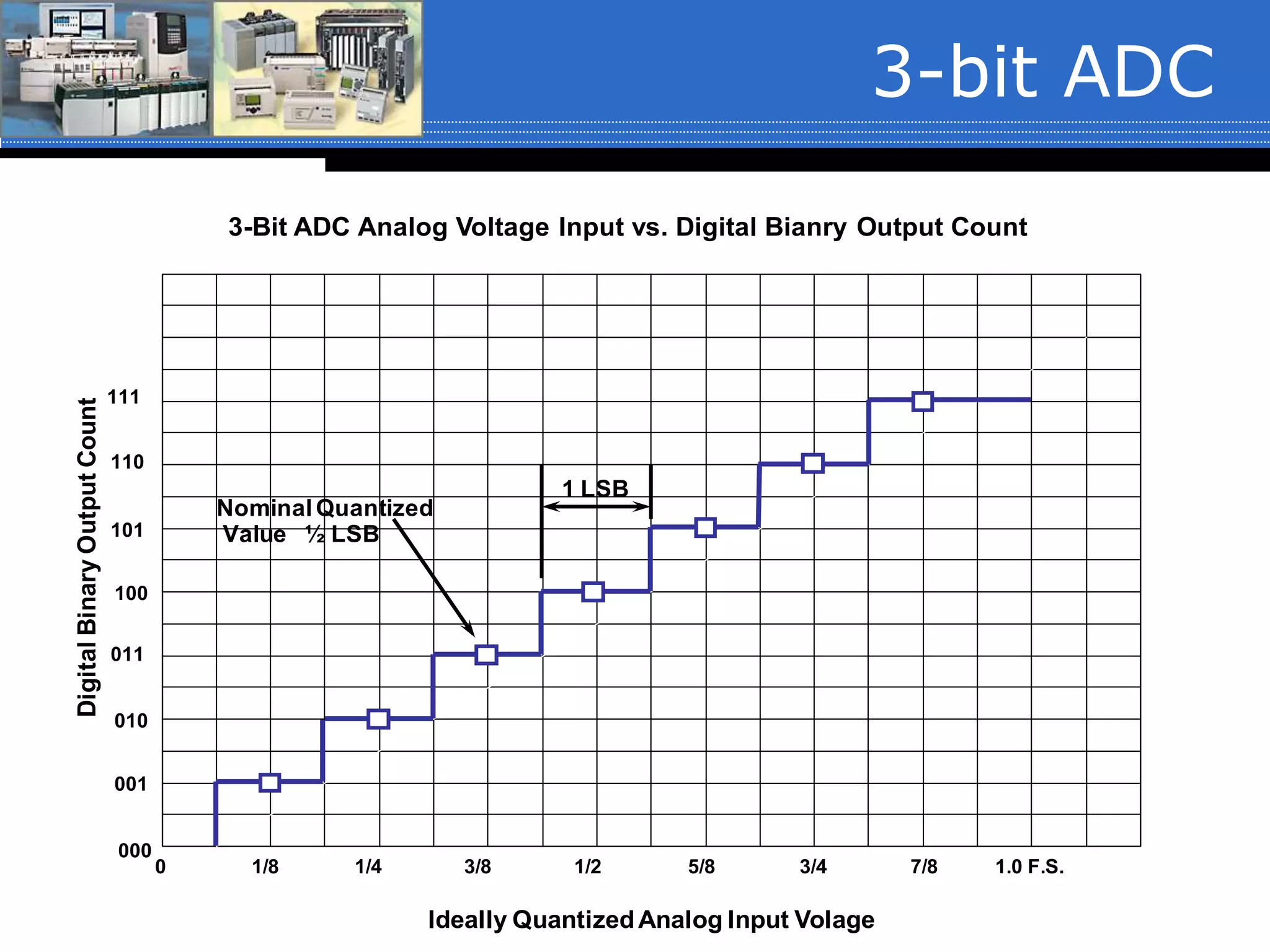

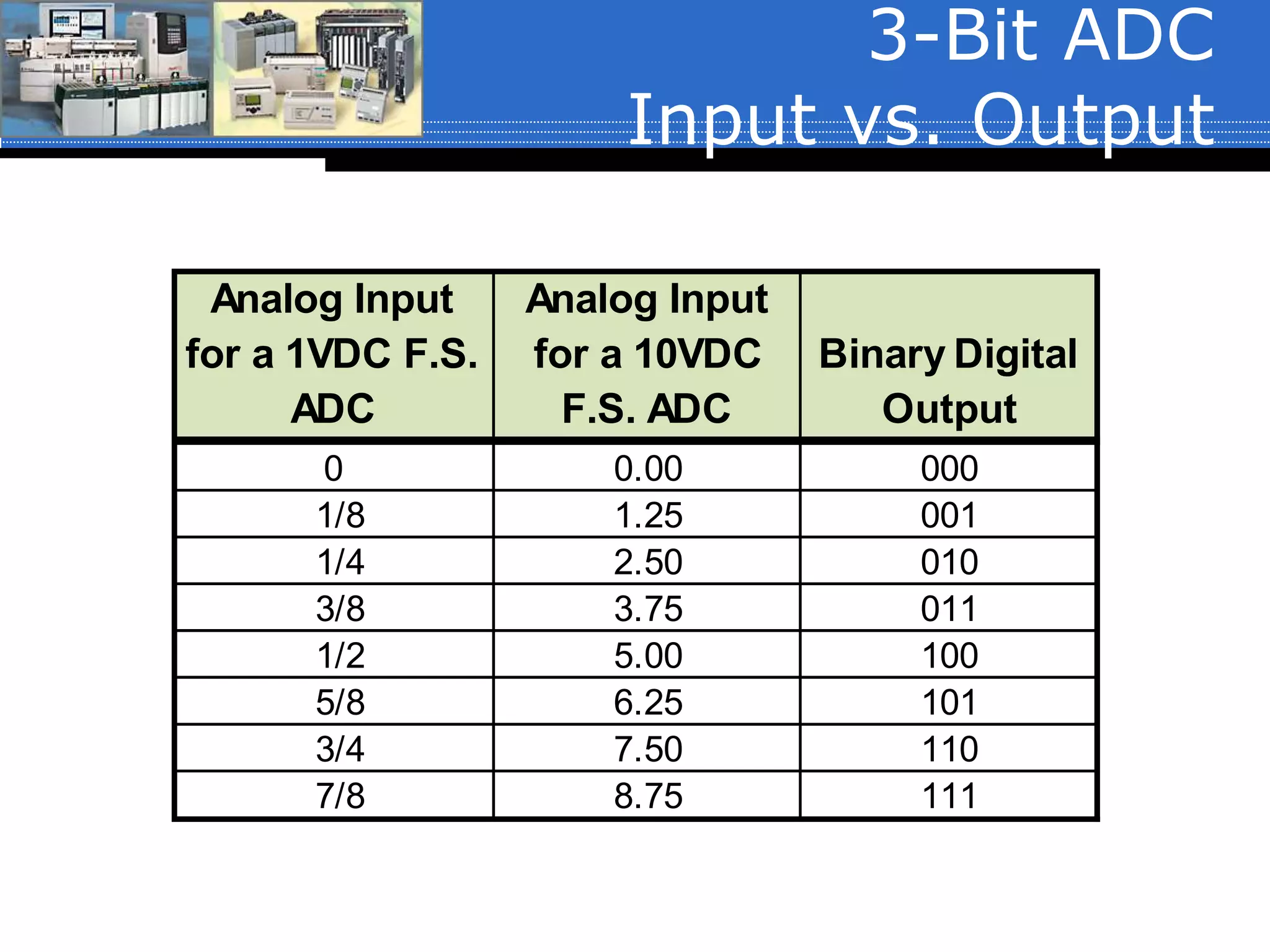

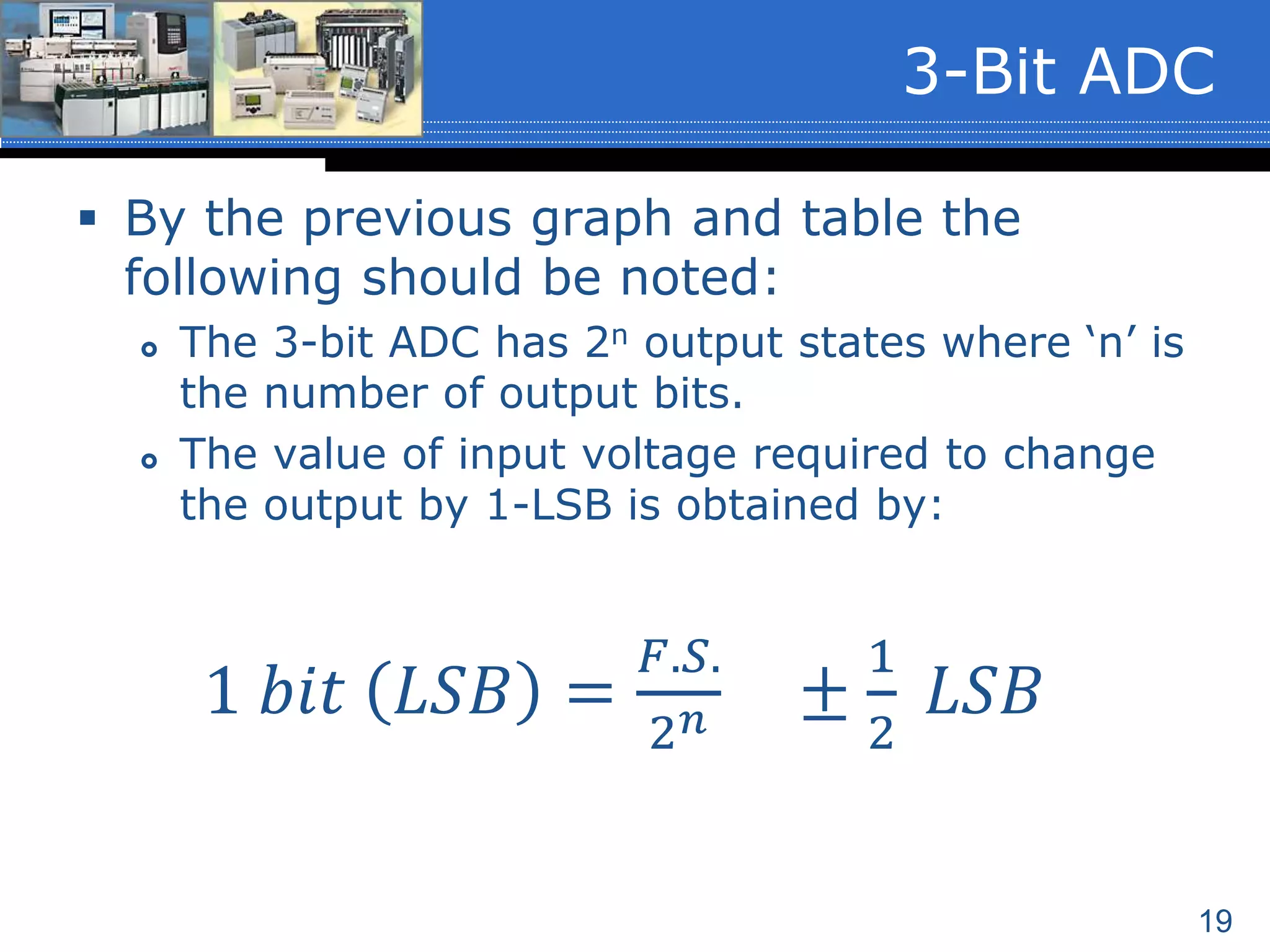

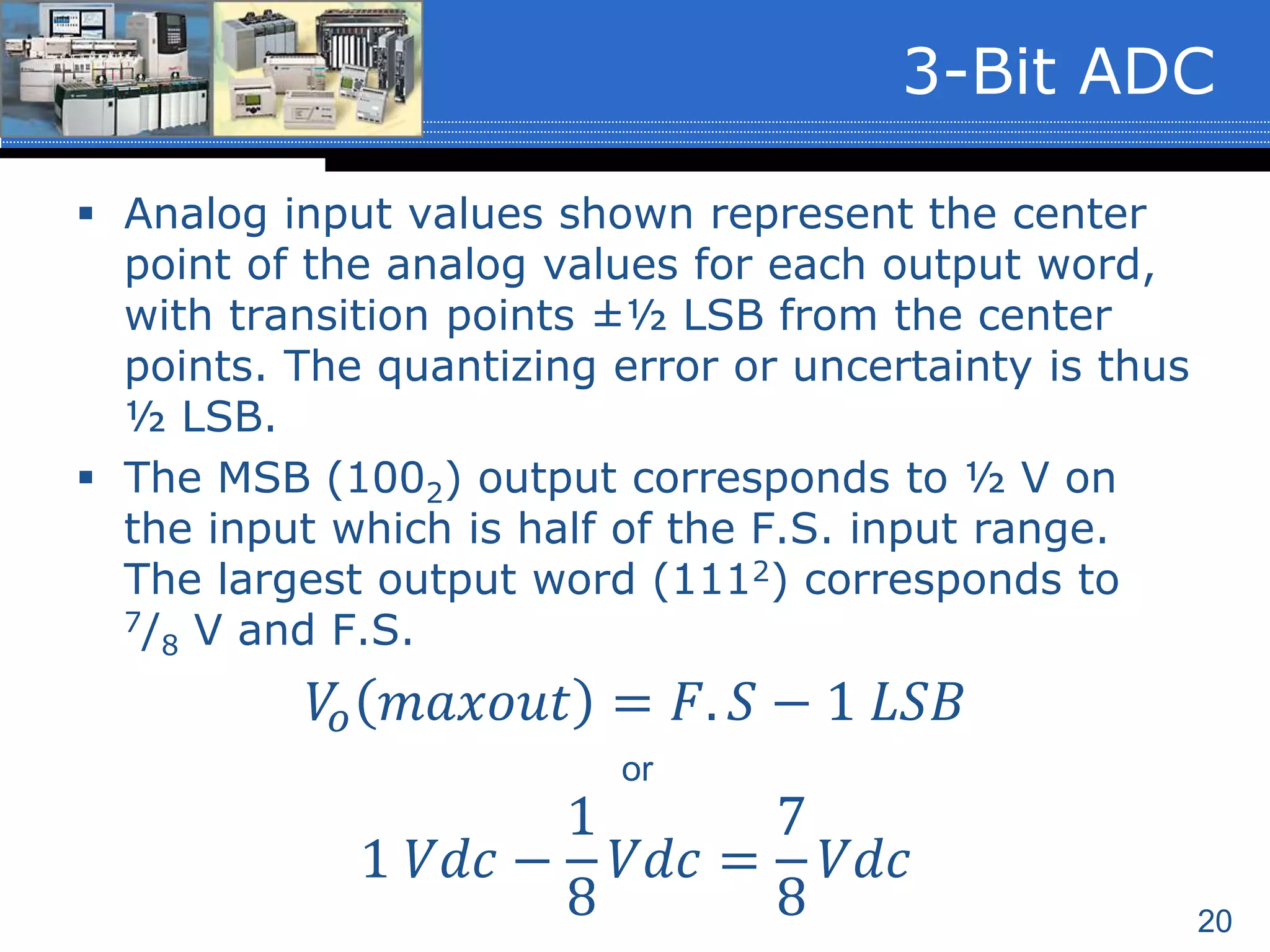

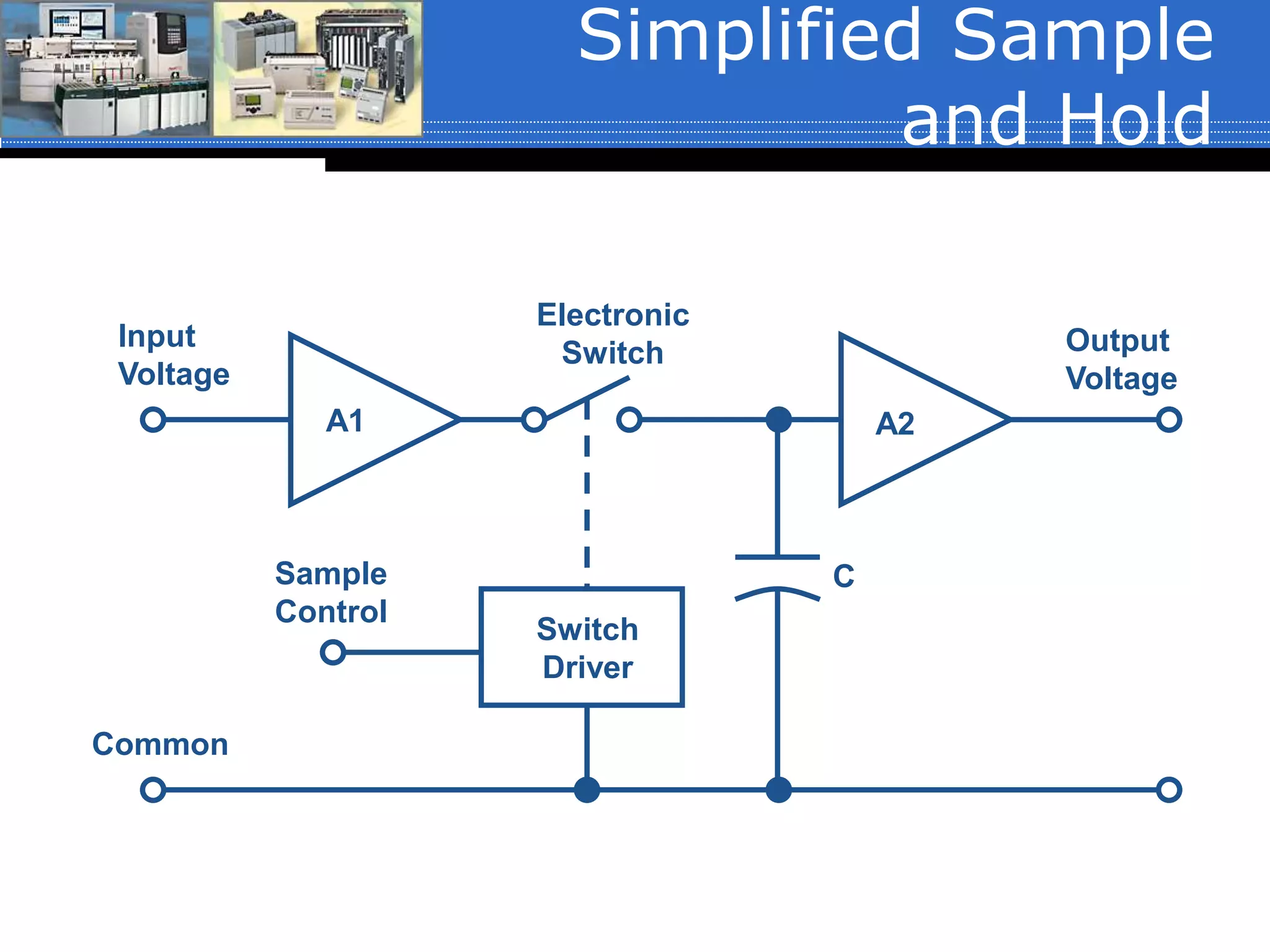

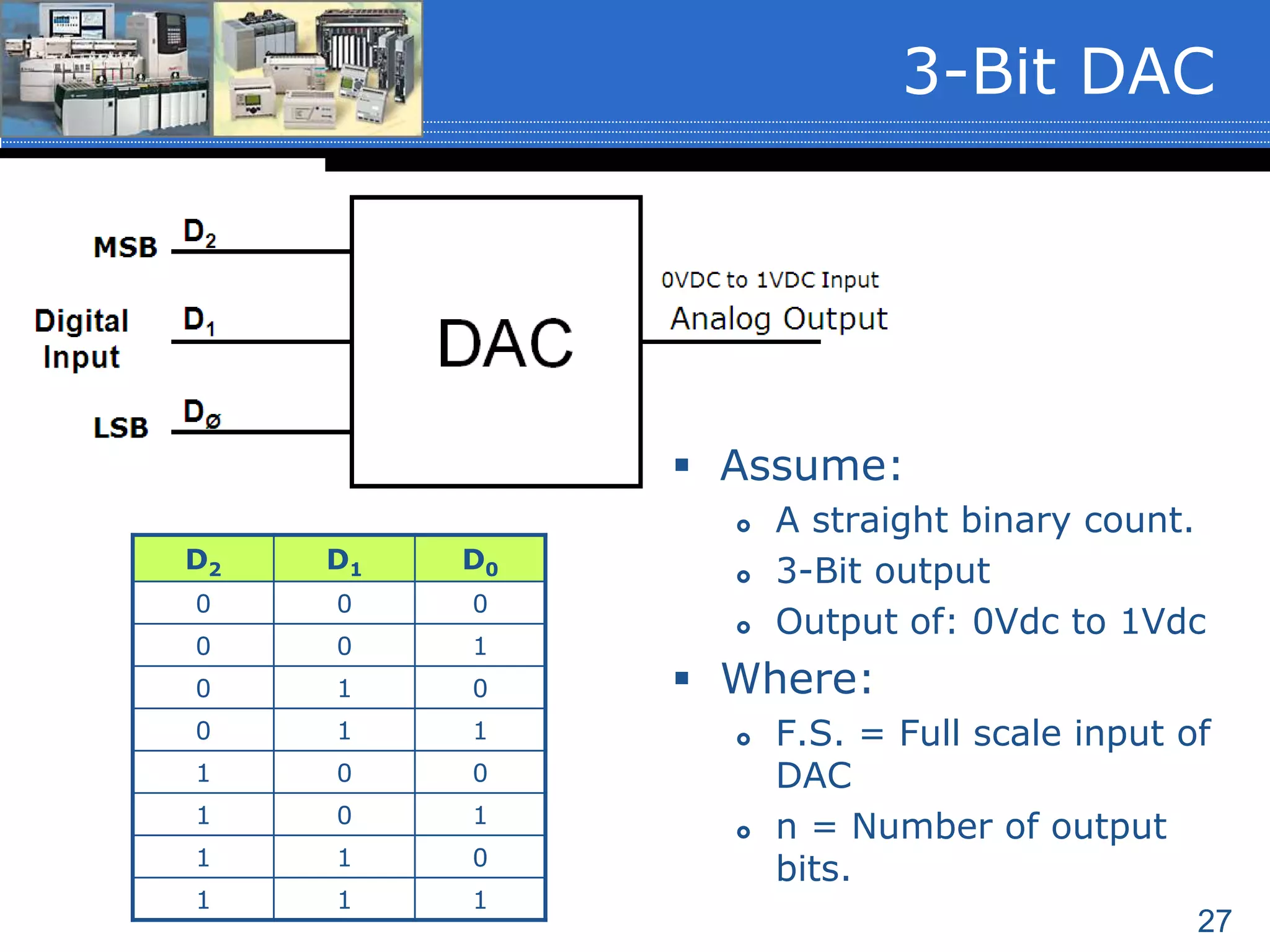

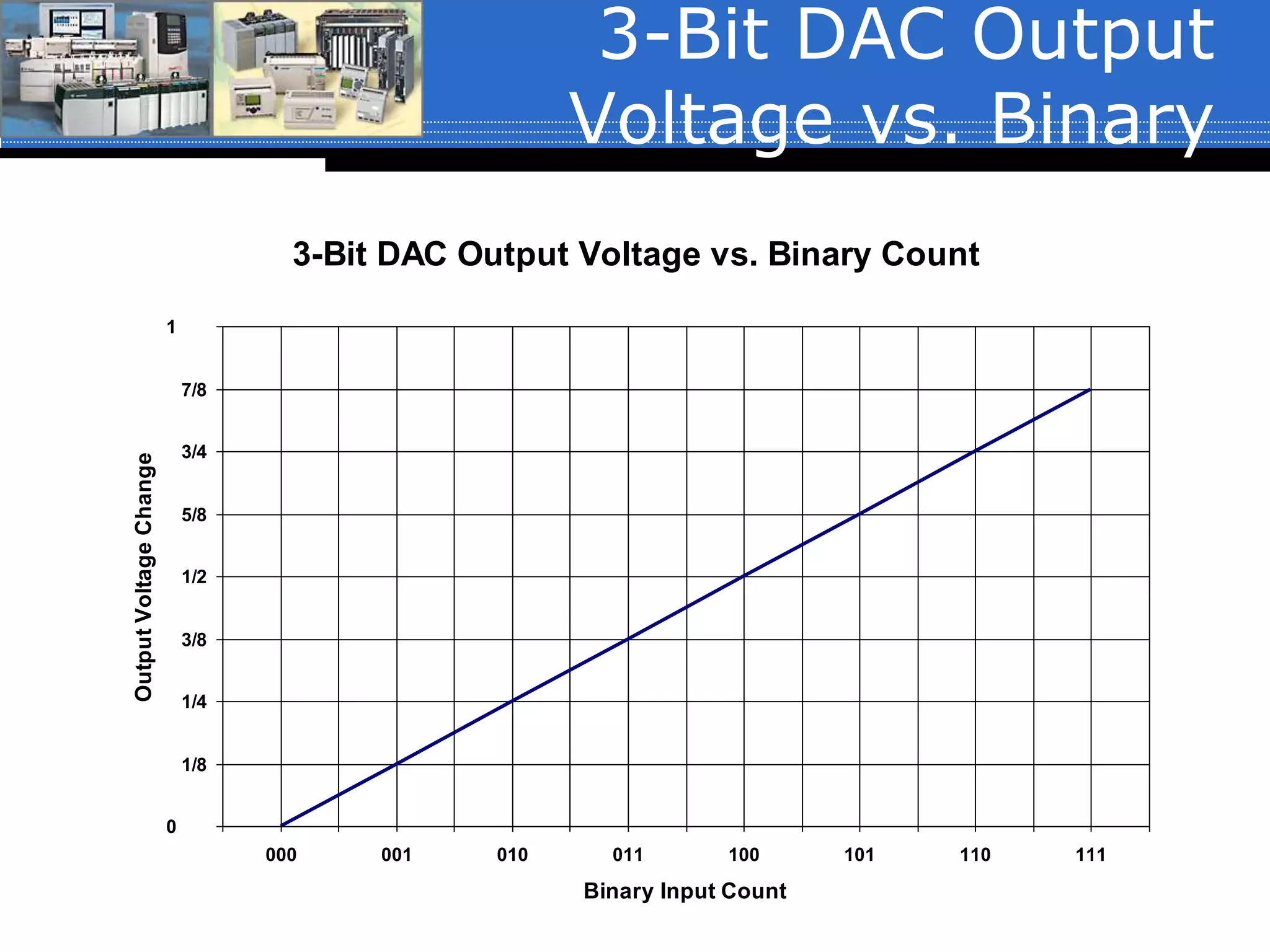

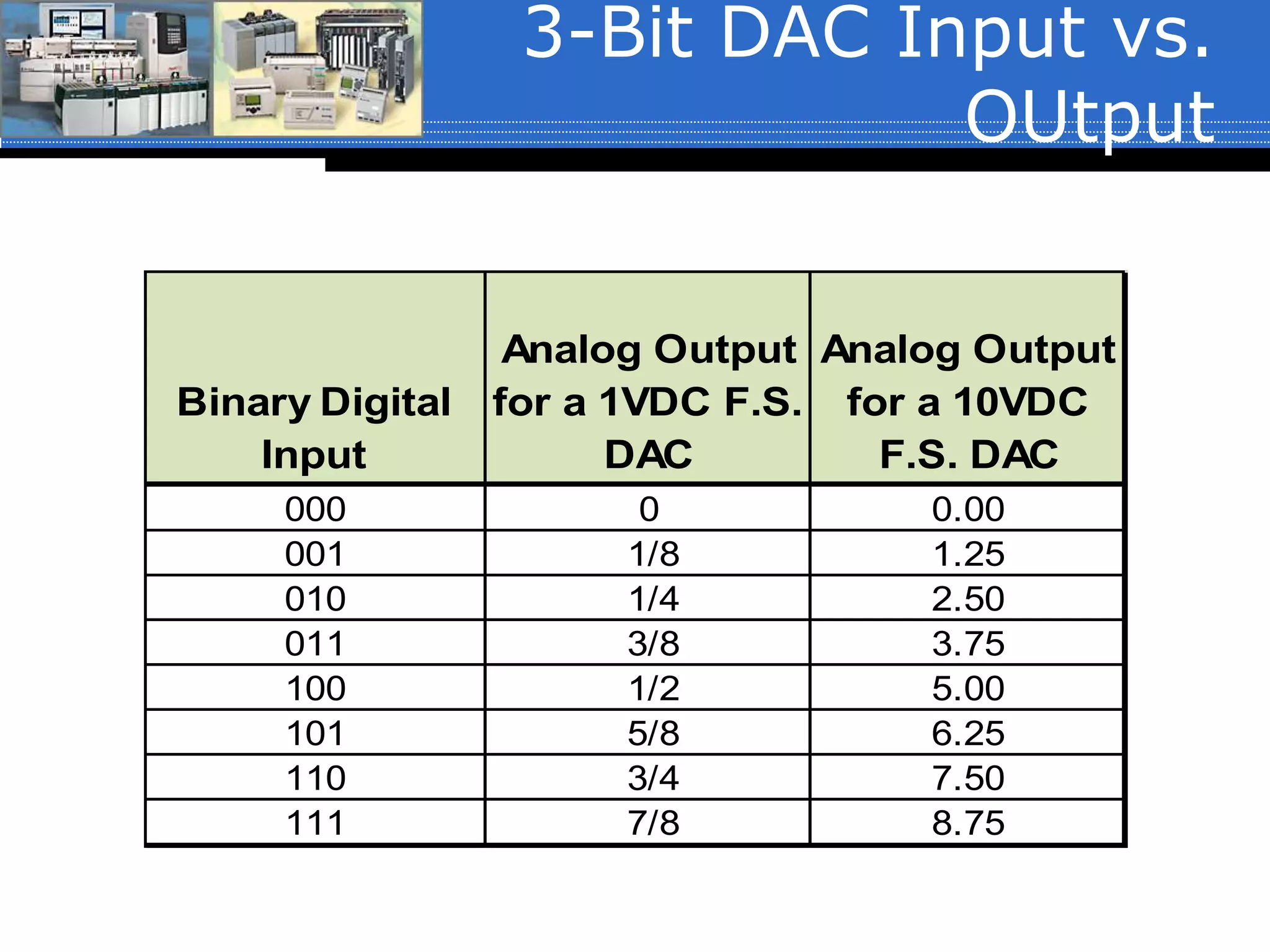

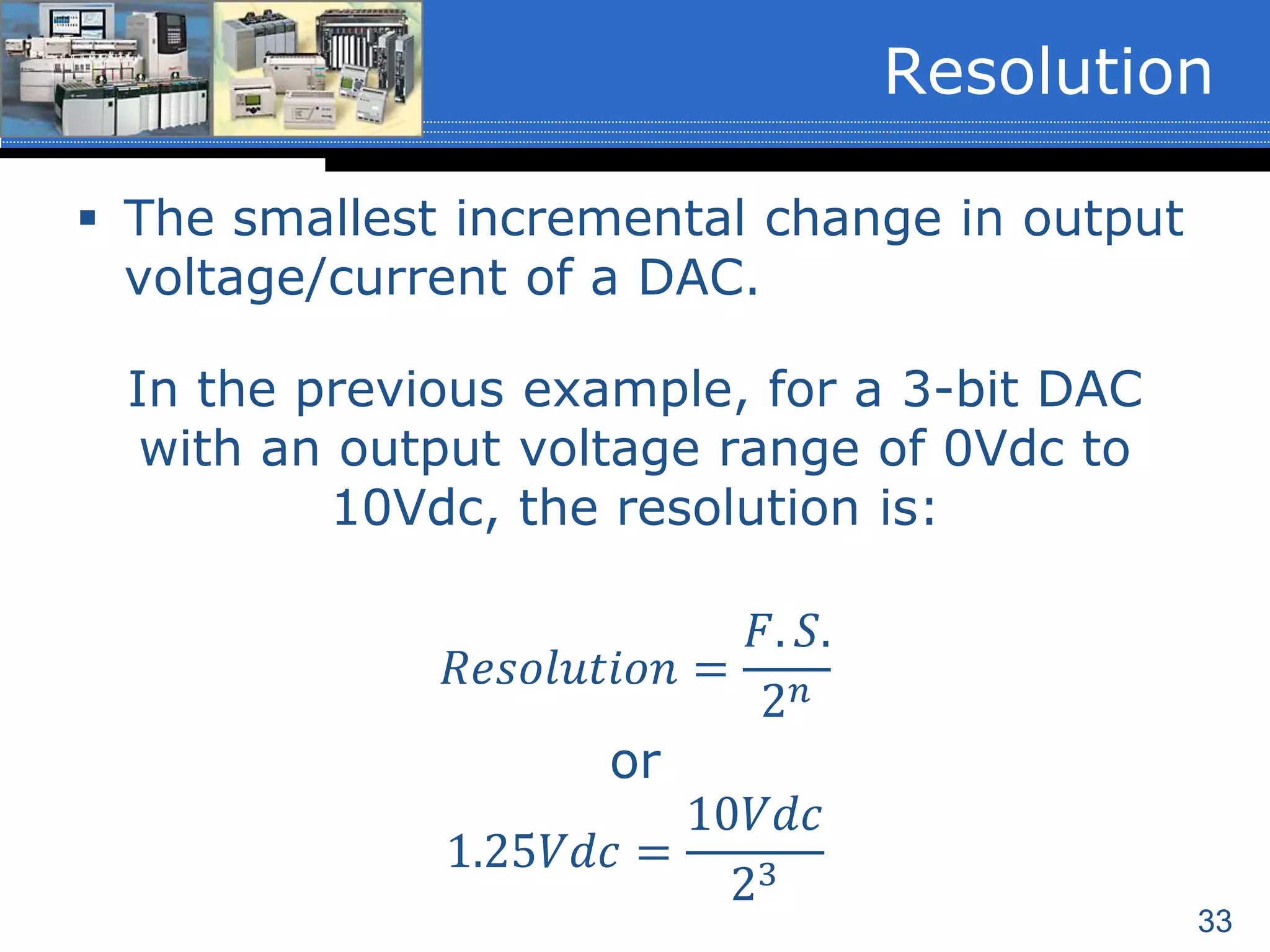

This document discusses analog control systems used with programmable logic controllers (PLCs) and programmable automation controllers (PACs). It describes how analog signals have continuous values between on and off, unlike discrete signals. It then explains that PLCs and PACs use analog input/output modules to interface with field devices that have continuously varying signals, such as temperature sensors, pressure sensors, motors etc. The document provides details on analog signal processing, including analog to digital conversion using ADCs and digital to analog conversion using DACs. It discusses key specifications for analog I/O modules such as resolution, conversion time and settling time.