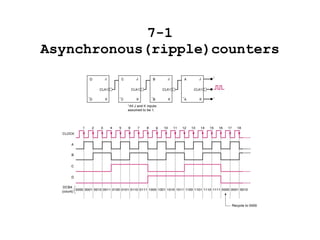

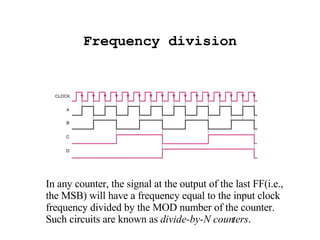

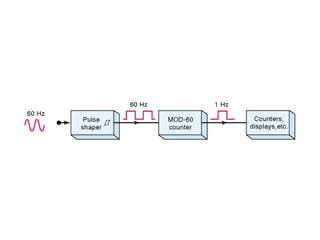

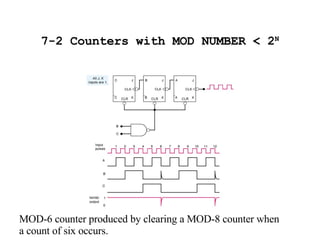

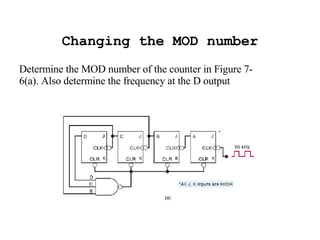

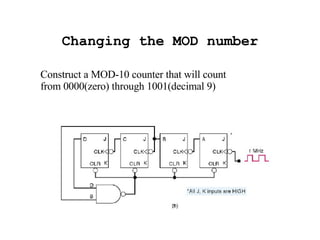

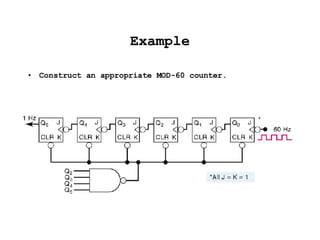

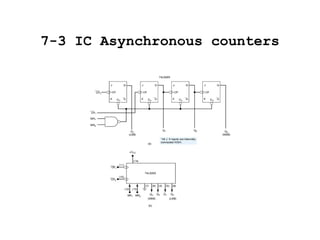

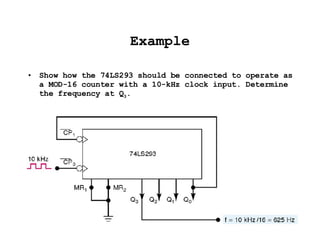

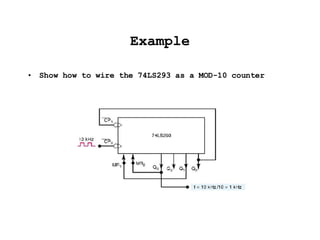

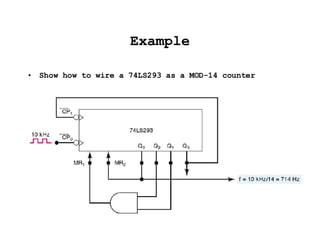

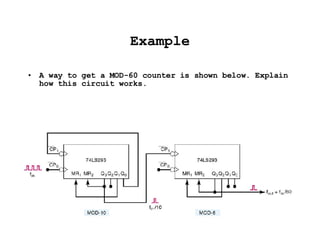

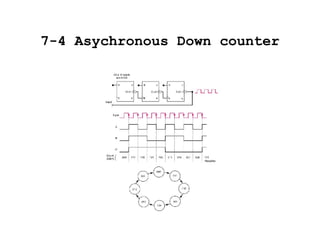

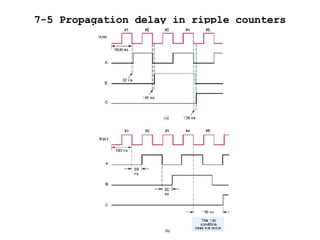

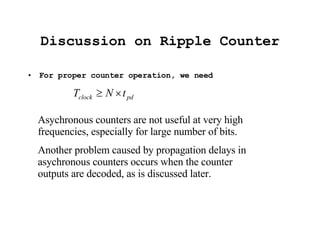

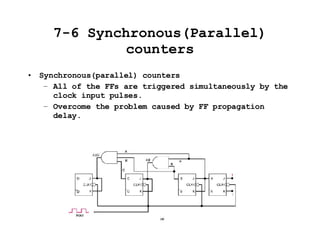

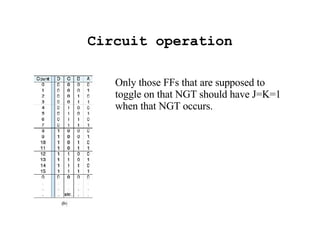

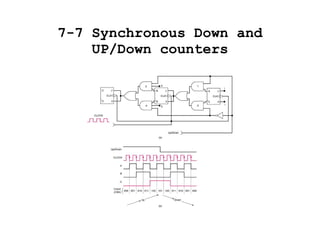

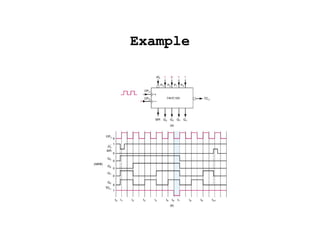

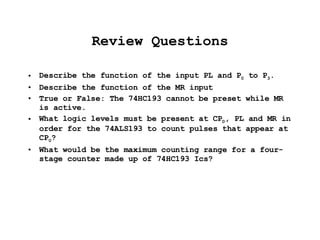

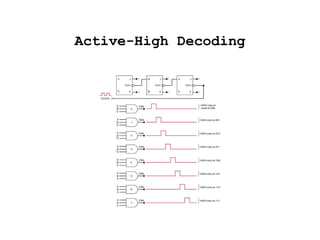

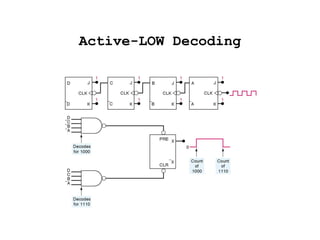

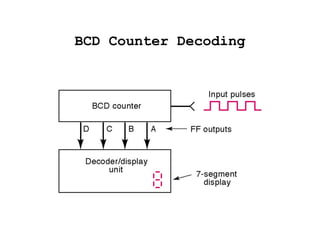

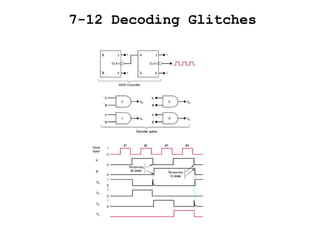

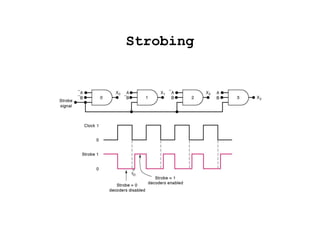

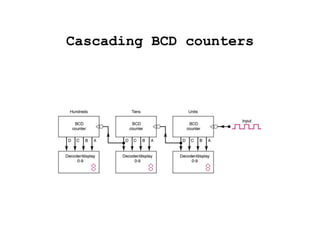

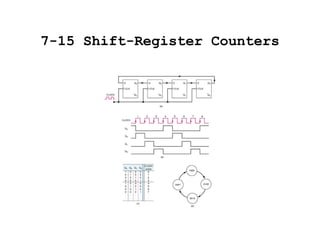

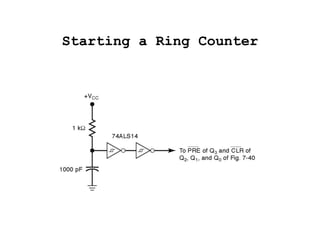

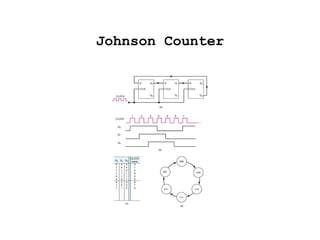

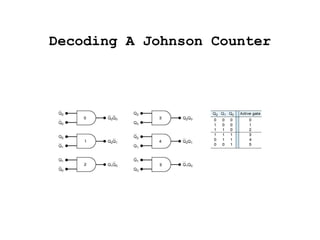

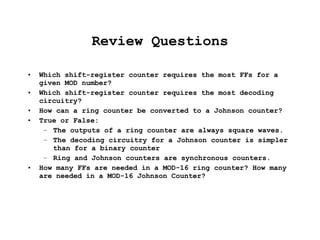

This document discusses different types of counters including asynchronous (ripple) counters, synchronous counters, down counters, and shift-register counters. It provides examples of how to construct various counters using flip-flops and logic gates. It also covers decoding the output states of counters and issues that can arise from propagation delays in asynchronous counters.