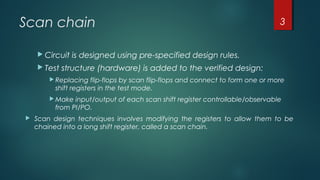

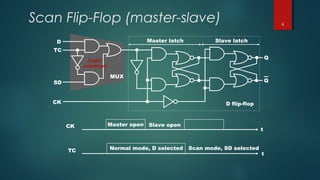

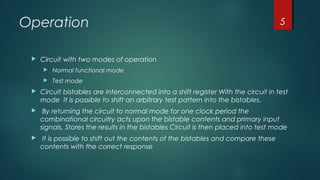

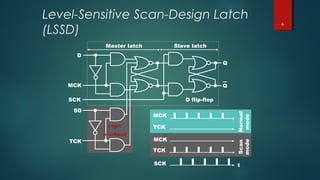

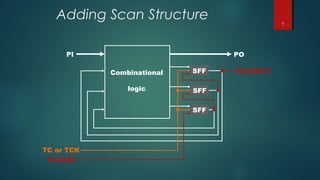

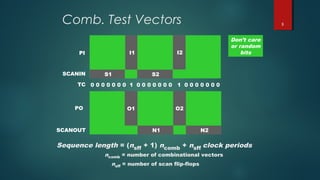

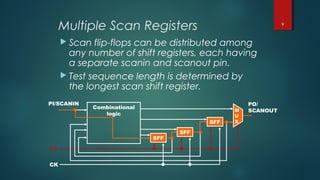

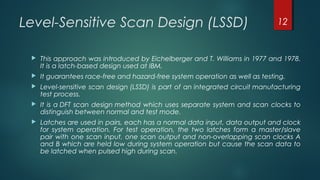

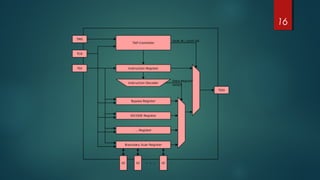

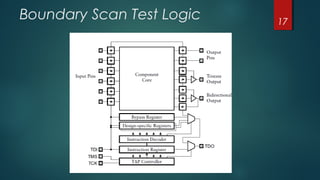

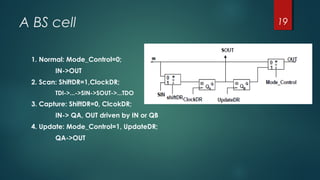

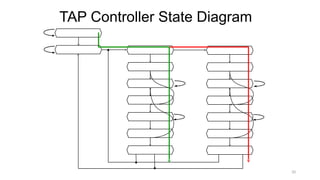

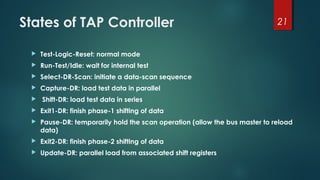

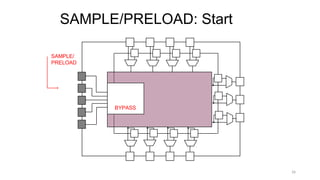

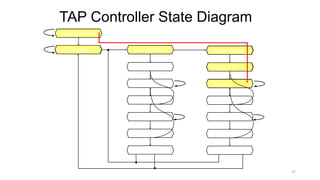

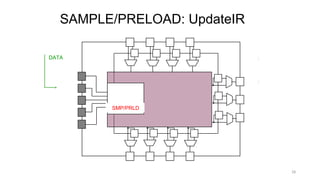

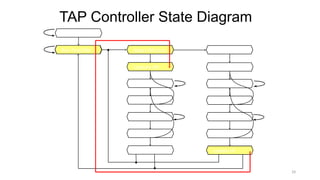

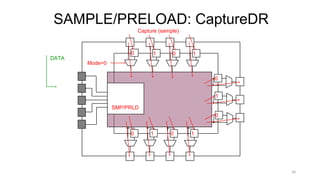

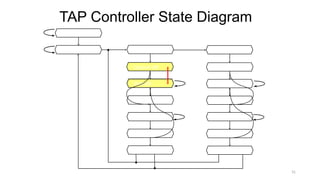

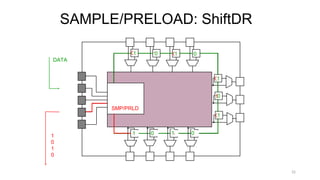

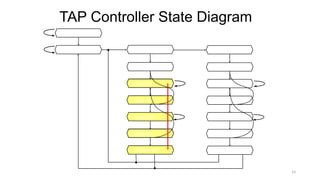

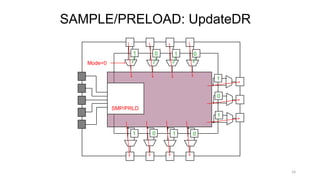

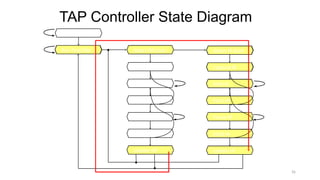

The document discusses level-sensitive scan design (LSSD) and boundary scan methods for testing digital circuits. It describes various design for testability (DFT) techniques, including scan chains and the introduction of a test access port (TAP) used in boundary scan testing. Additionally, the advantages and drawbacks of LSSD, as well as the operational aspects of boundary scan testing, are outlined.