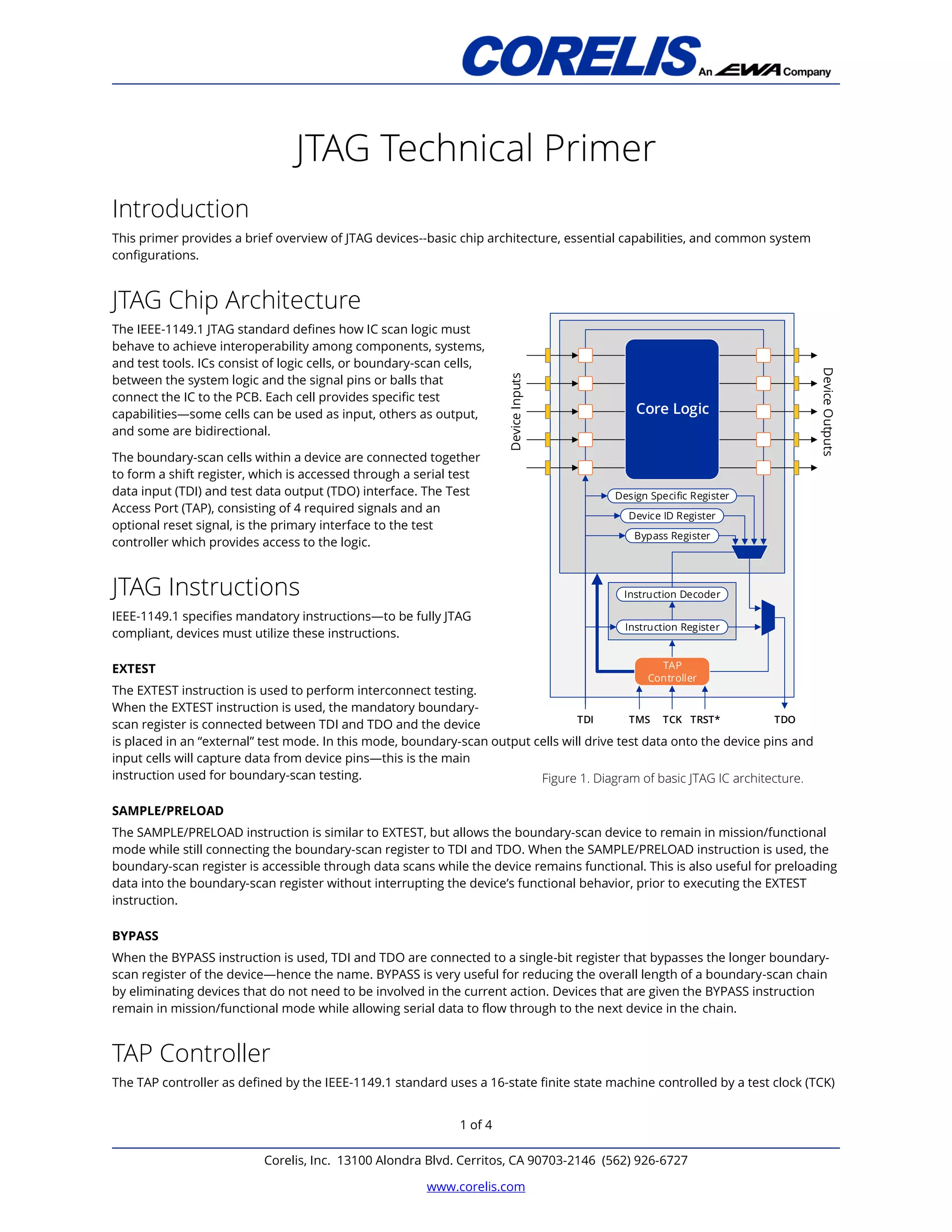

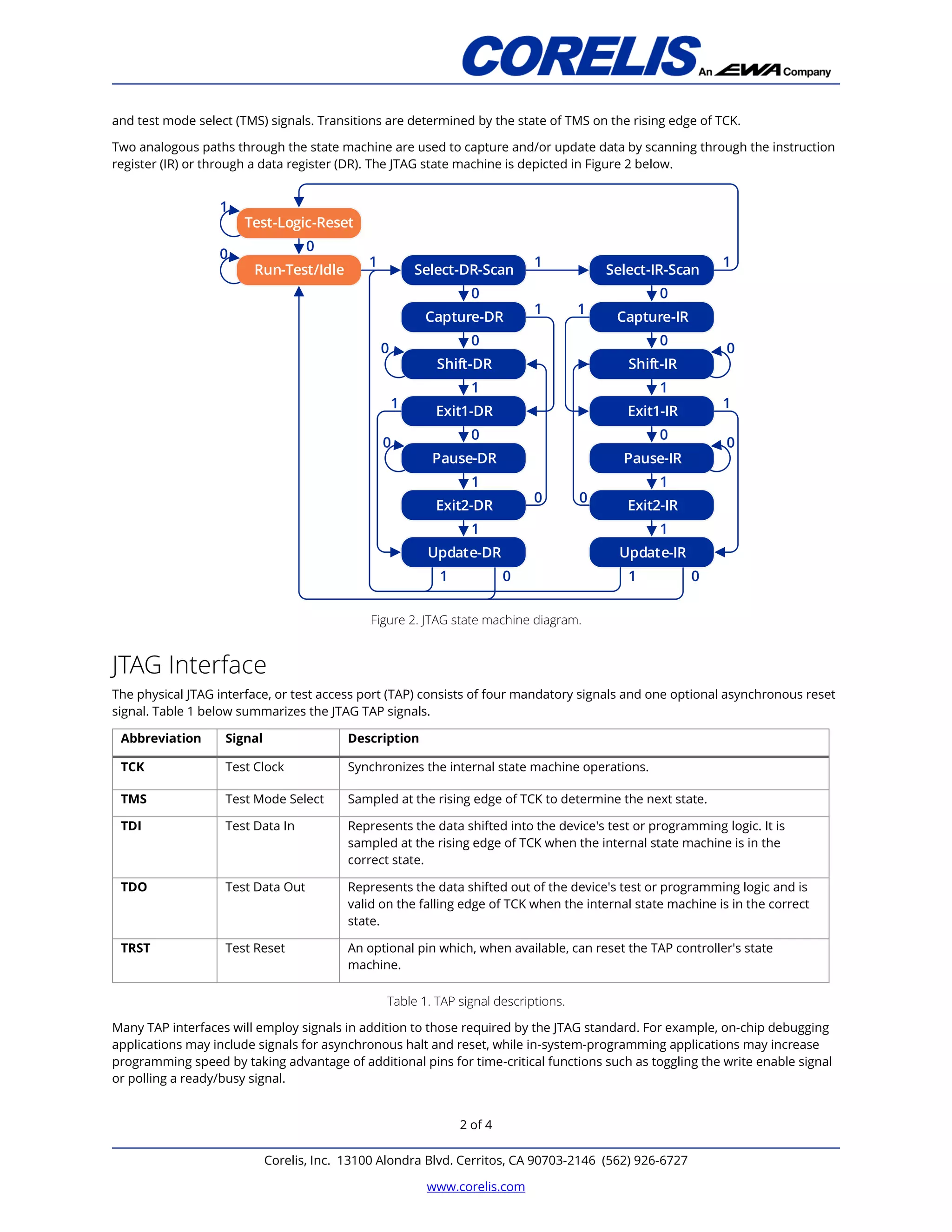

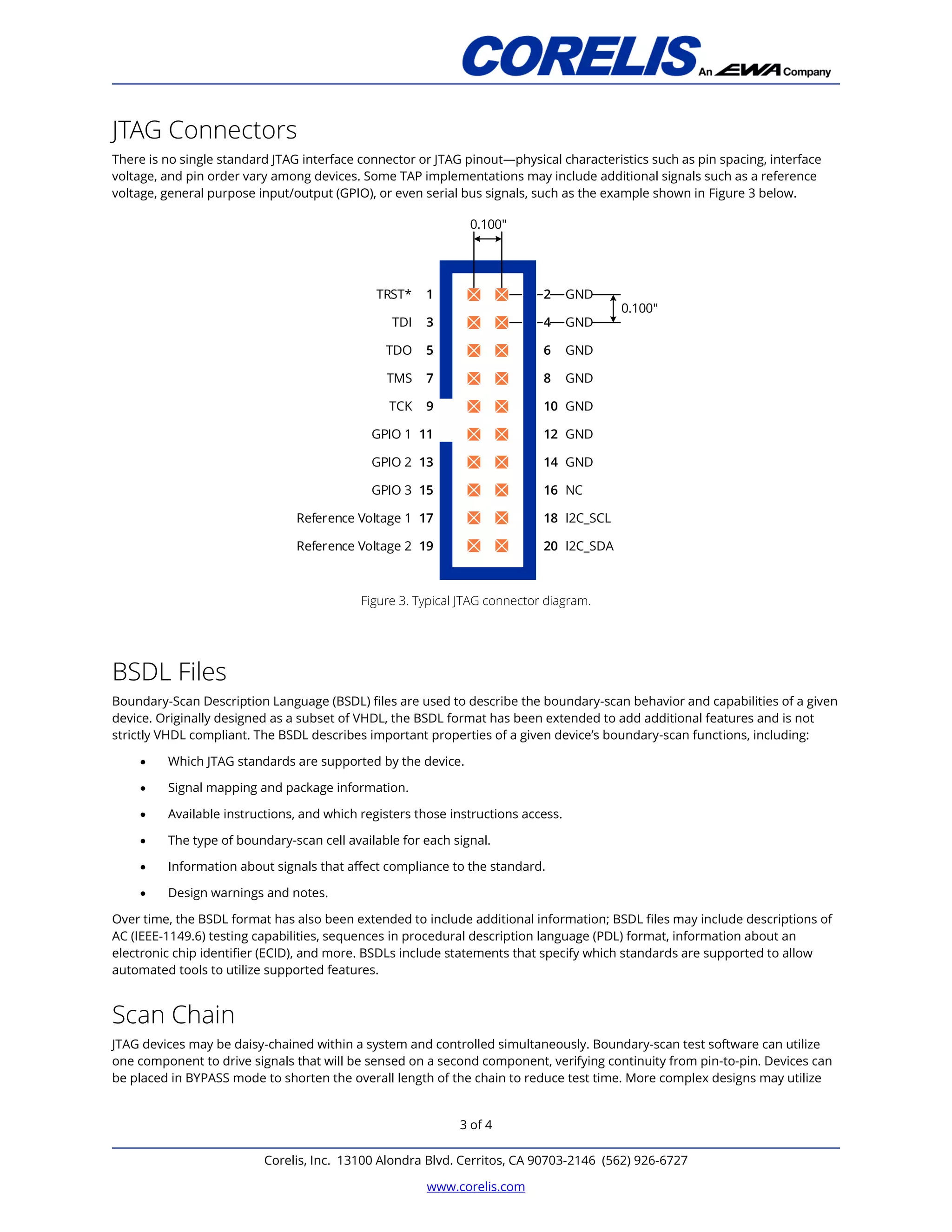

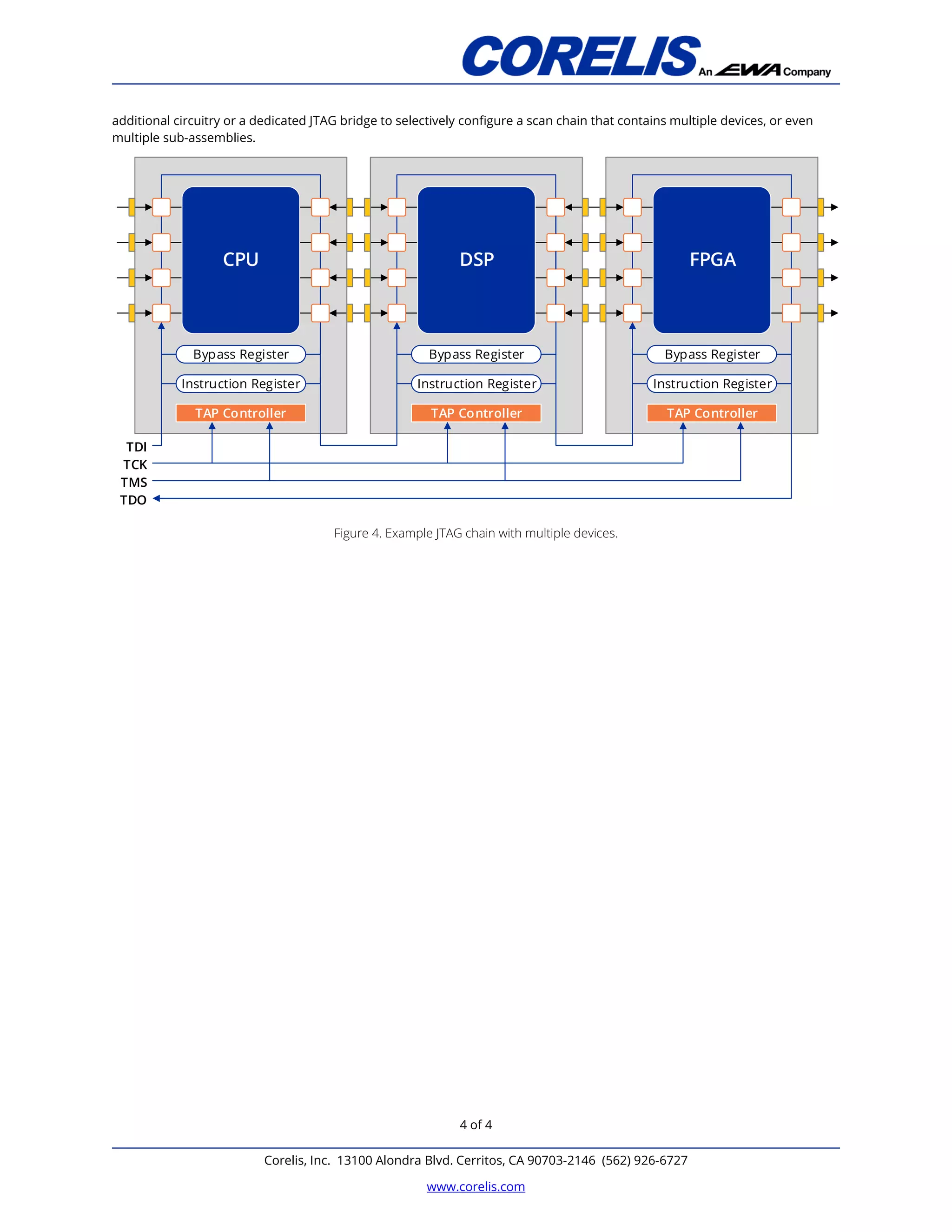

This document provides an overview of JTAG (Joint Test Action Group) devices, including their basic chip architecture, capabilities, and common system configurations. It describes the JTAG standard architecture which defines boundary-scan cells and a test access port. It also summarizes common JTAG instructions, the TAP controller state machine, typical JTAG interfaces and connectors, BSDL description files, and how JTAG devices can be daisy-chained to form a scan chain for testing connections between components.