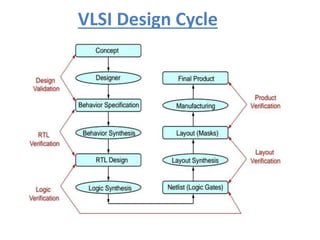

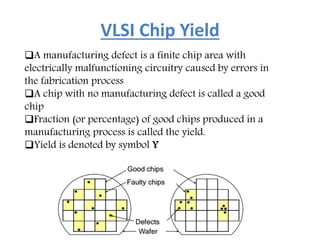

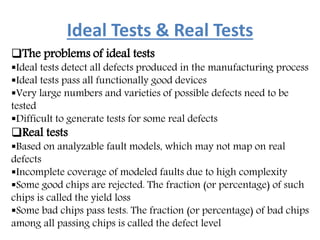

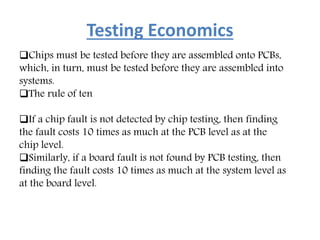

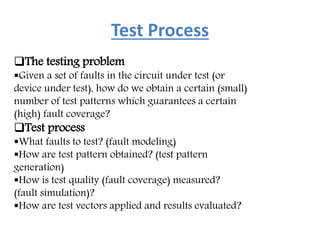

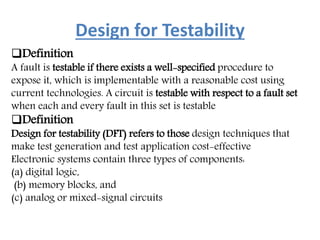

This document discusses VLSI faults and testing. It begins by outlining the VLSI realization process from customer needs to fabrication. It then defines key terms like defects, faults, errors and describes common types of defects from fabrication. The document discusses logical fault models and the role of testing in detecting errors. It outlines different types of testing like production testing and burn-in testing. Finally, it discusses topics like design for testability, fault simulation, and benefits of testing like improved quality and economy of scale.