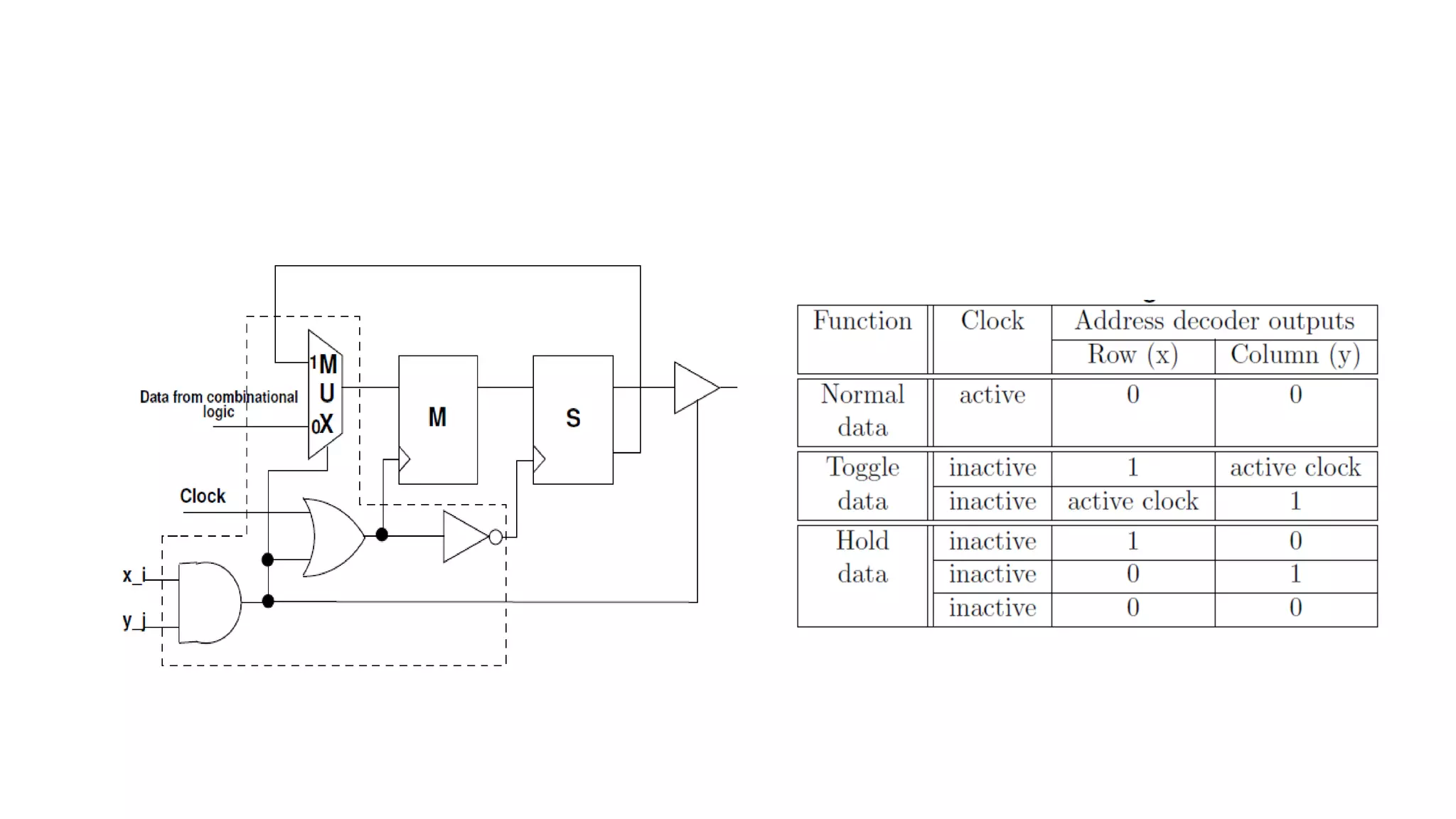

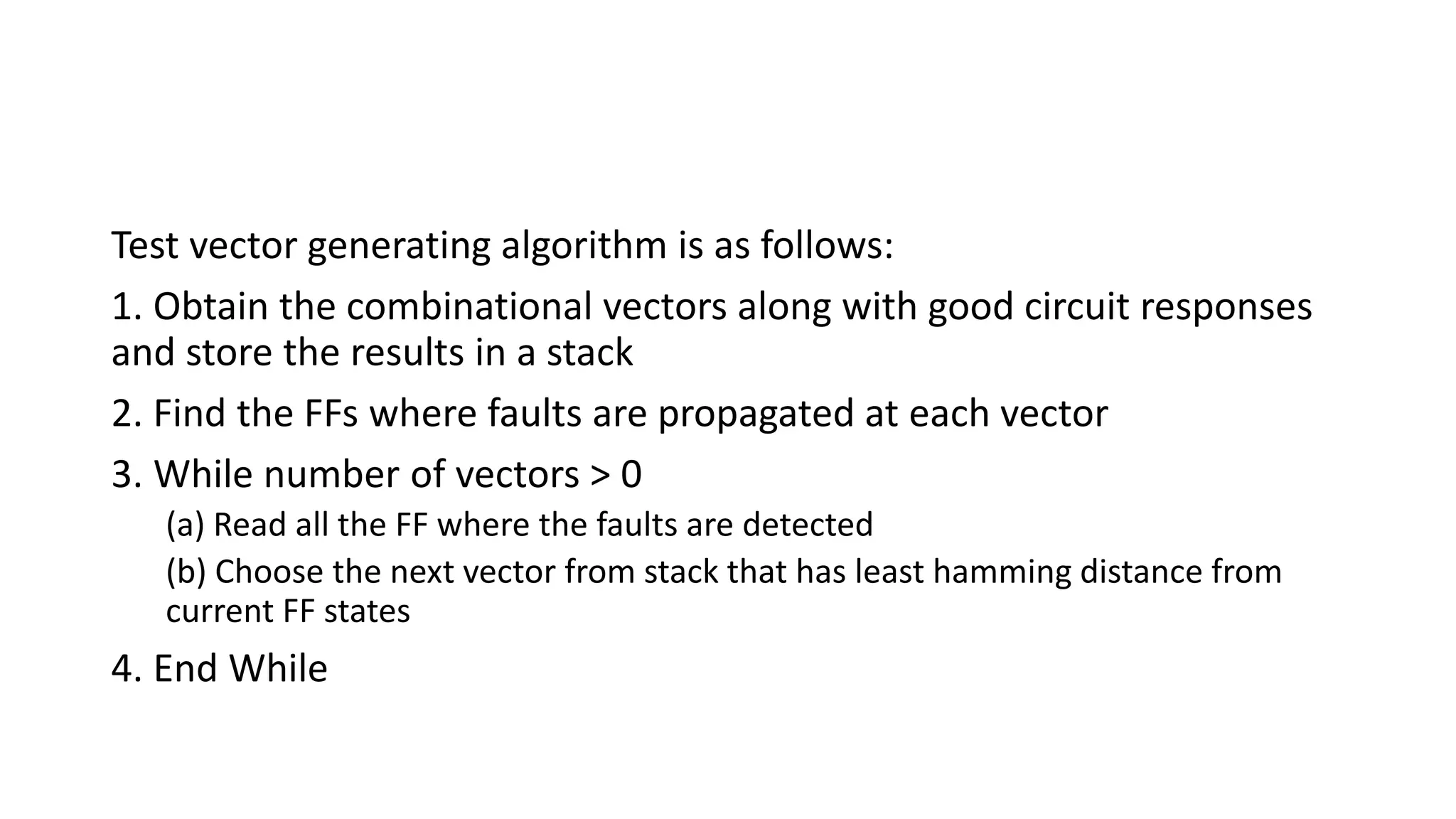

This document discusses limitations of traditional serial scan design for testing integrated circuits and proposes an alternative called Random Access Scan (RAS). RAS addresses three key limitations of serial scan: 1) test data volume, 2) test application time, and 3) test power. In RAS, flip-flops act as addressable memory elements during test mode, reducing time to set and observe flip-flop states compared to serial scan. While RAS requires more gates and test pins than serial scan, it significantly reduces switching activity and power consumption during testing.

![• [1] Dong Hyun Baik, Kewal K. Saluja, Seiji Kajihara, “Random Access Scan: A

solution to test power, test data volume and test time”, Proceedings of the

17th International Conference on VLSI Design, 2004

• [2] H. Ando, “Testing VLSI with Random Access Scan”, in Proc. Of the

COMPCON, Feb. 1980

• [3] V. D. Agrawal, K.-T. Cheng, D. D. Johnson, and T. Lin, “Designing Circuits

with Partial Scan”, IEEE Design & Test of Computers, vol. 5, pp. 8 - 15, Apr.

1988.

• [4] Fan Wang, Auburn University, Dept. of Electrical and Computer

Engineering, “Random Access Scan”, Term Paper, 2006

• [5] www.Wikipedia.org](https://image.slidesharecdn.com/randomaccessscan-140415153707-phpapp01/75/Random-access-scan-12-2048.jpg)