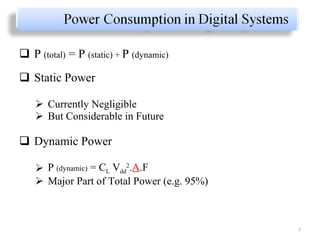

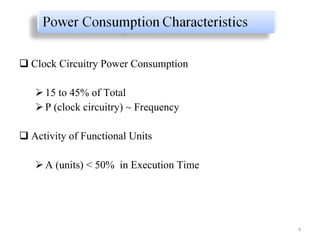

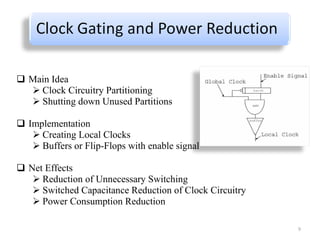

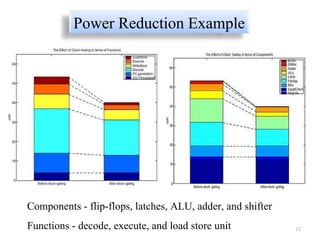

The document discusses power consumption in microprocessors and techniques for power reduction. It notes that dynamic power, which scales with the square of the supply voltage and operating frequency, makes up the majority of total power consumption. Clock circuitry alone can account for 15-45% of total power. Clock gating and data gating are introduced as approaches to reduce unnecessary switching activity and clock distribution by powering down unused modules. An example of applying clock gating at the architectural level is given to turn off parts of a processor's decode, execute, and load/store units to achieve considerable power reduction of up to 25%.