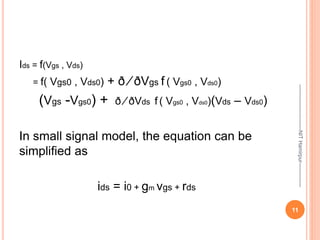

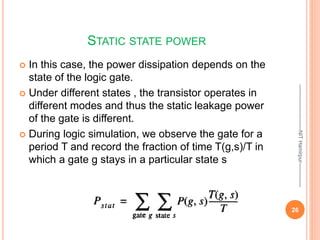

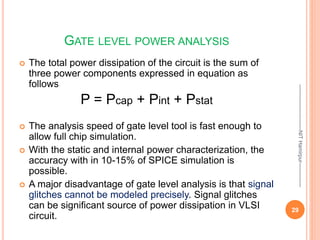

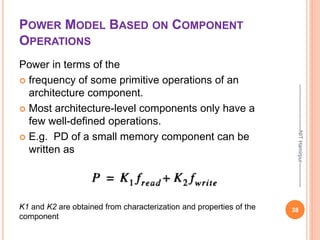

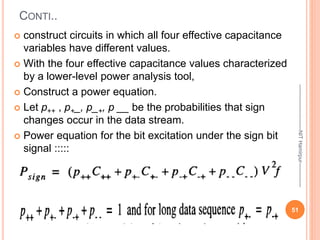

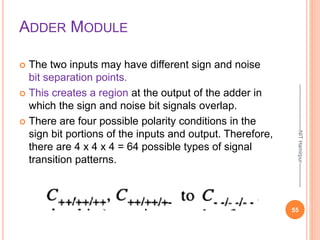

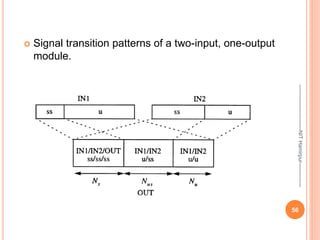

The document discusses various simulation techniques used to estimate power dissipation at different levels of abstraction. It describes the tradeoff between computing resources and accuracy at different levels from algorithm to transistor level. SPICE circuit simulation provides the most accurate results but requires significant computing power. Higher levels of abstraction like gate level, switch level and architecture level analyses provide faster simulation speed at the cost of reduced accuracy. Power models are developed based on activities, component operations and data correlation to capture power at architecture level for large designs.