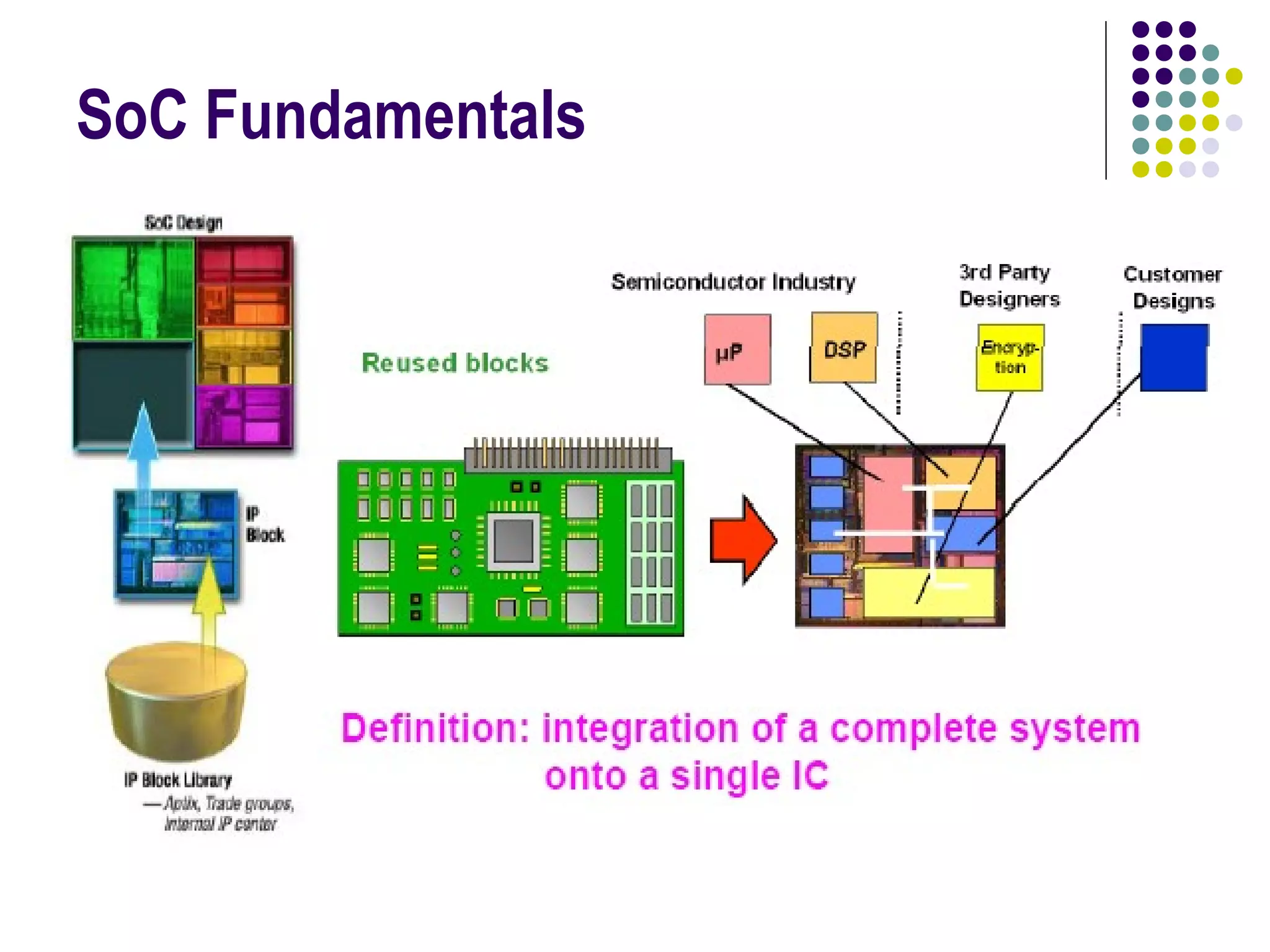

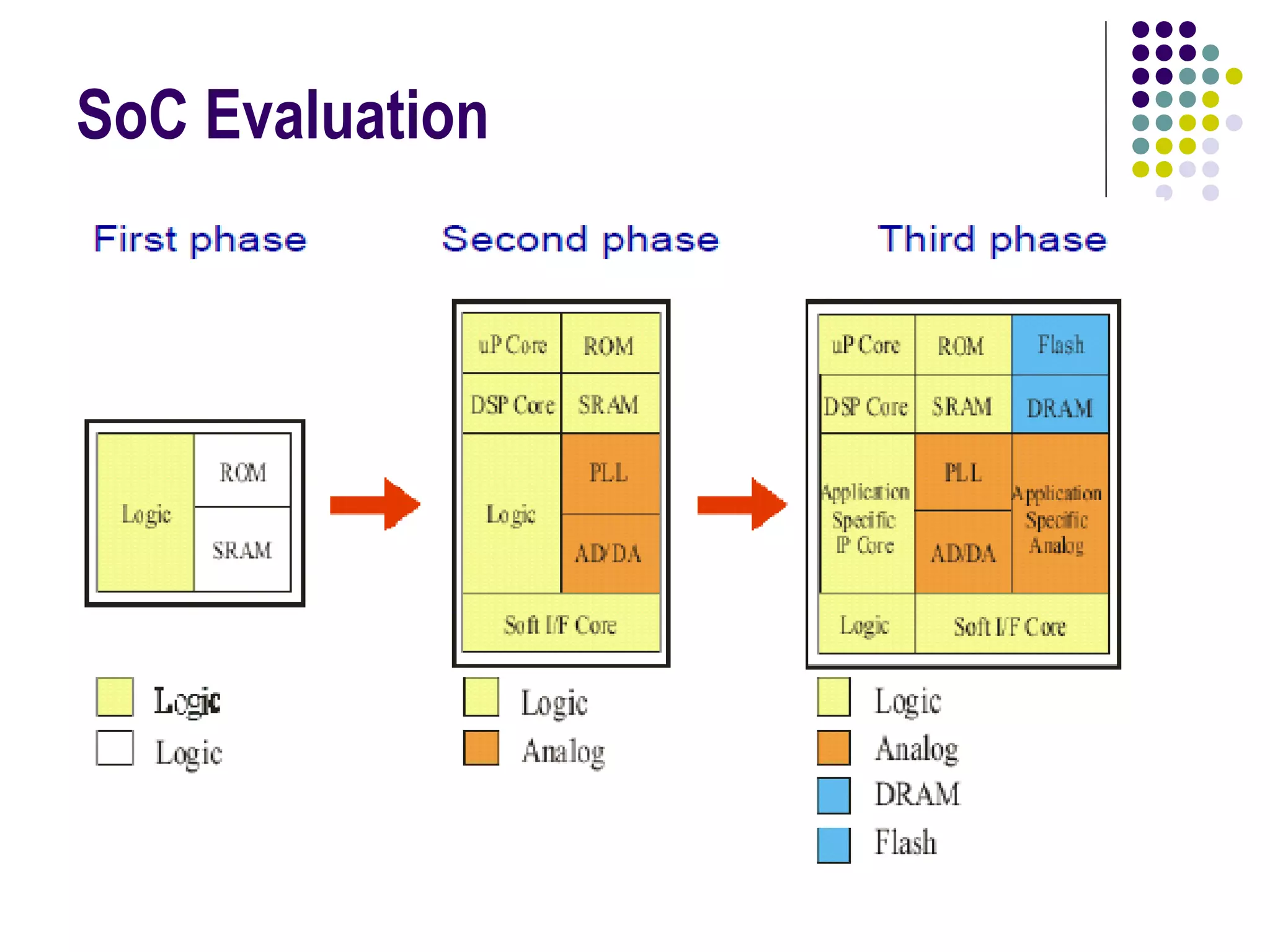

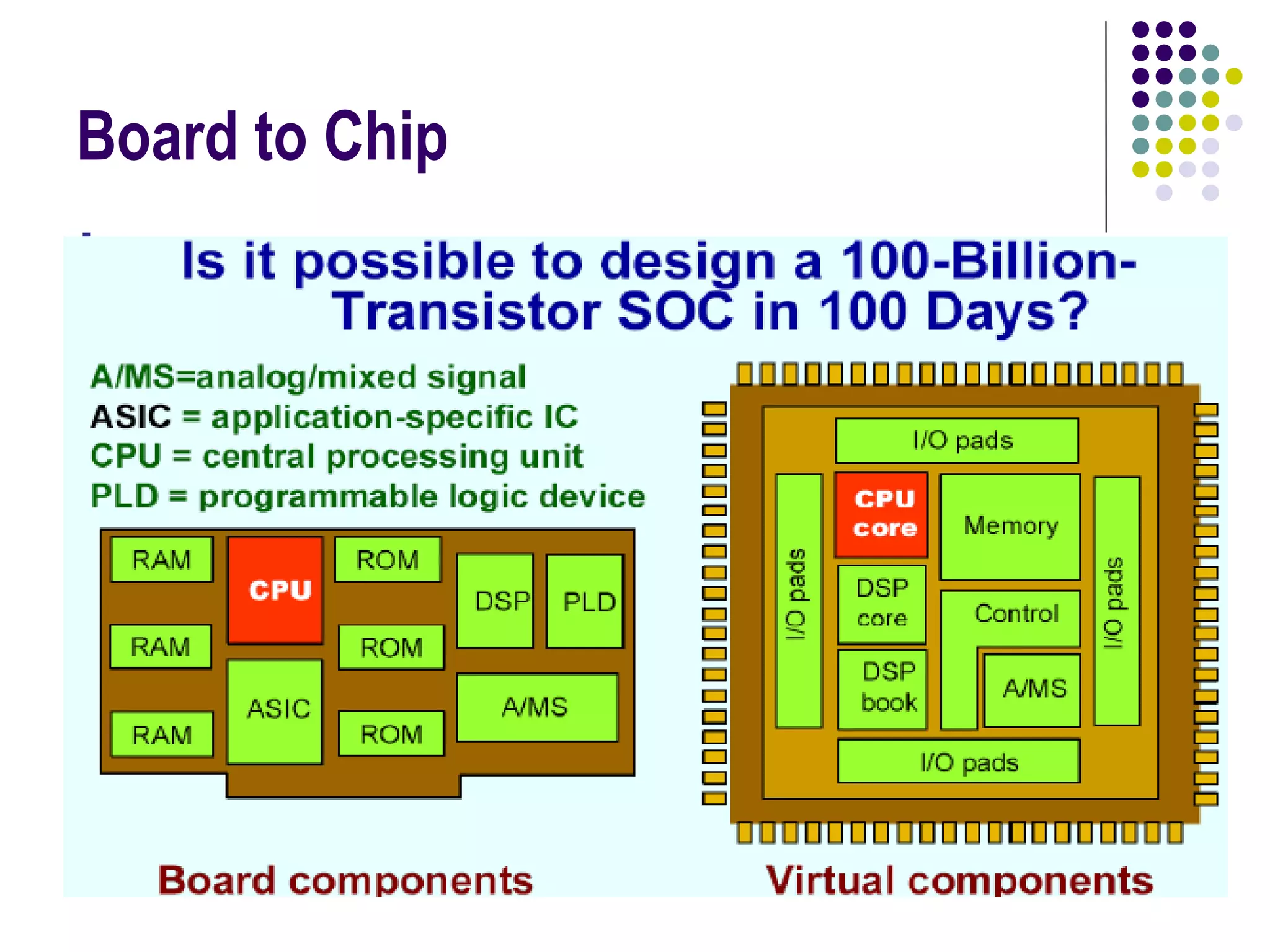

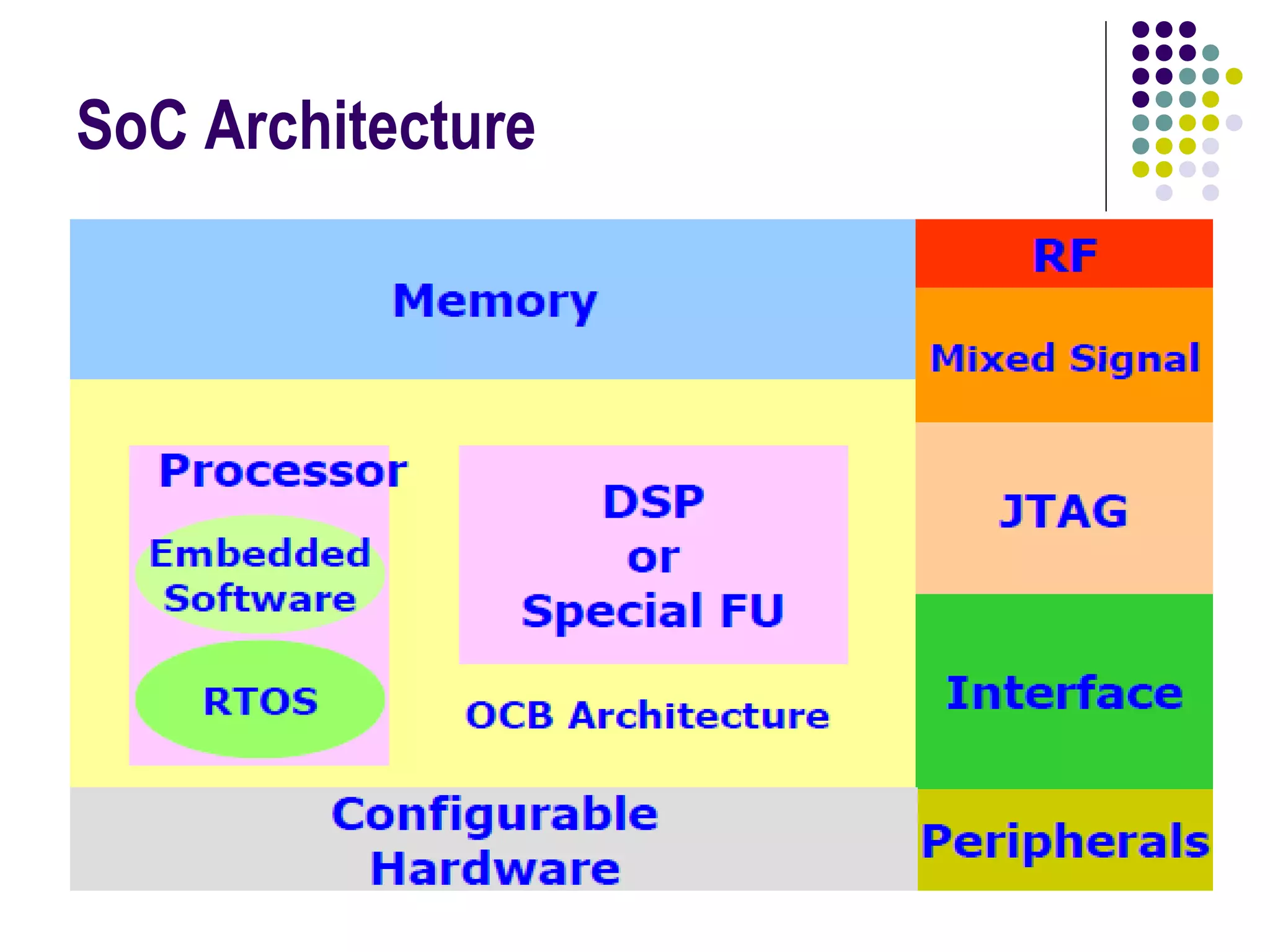

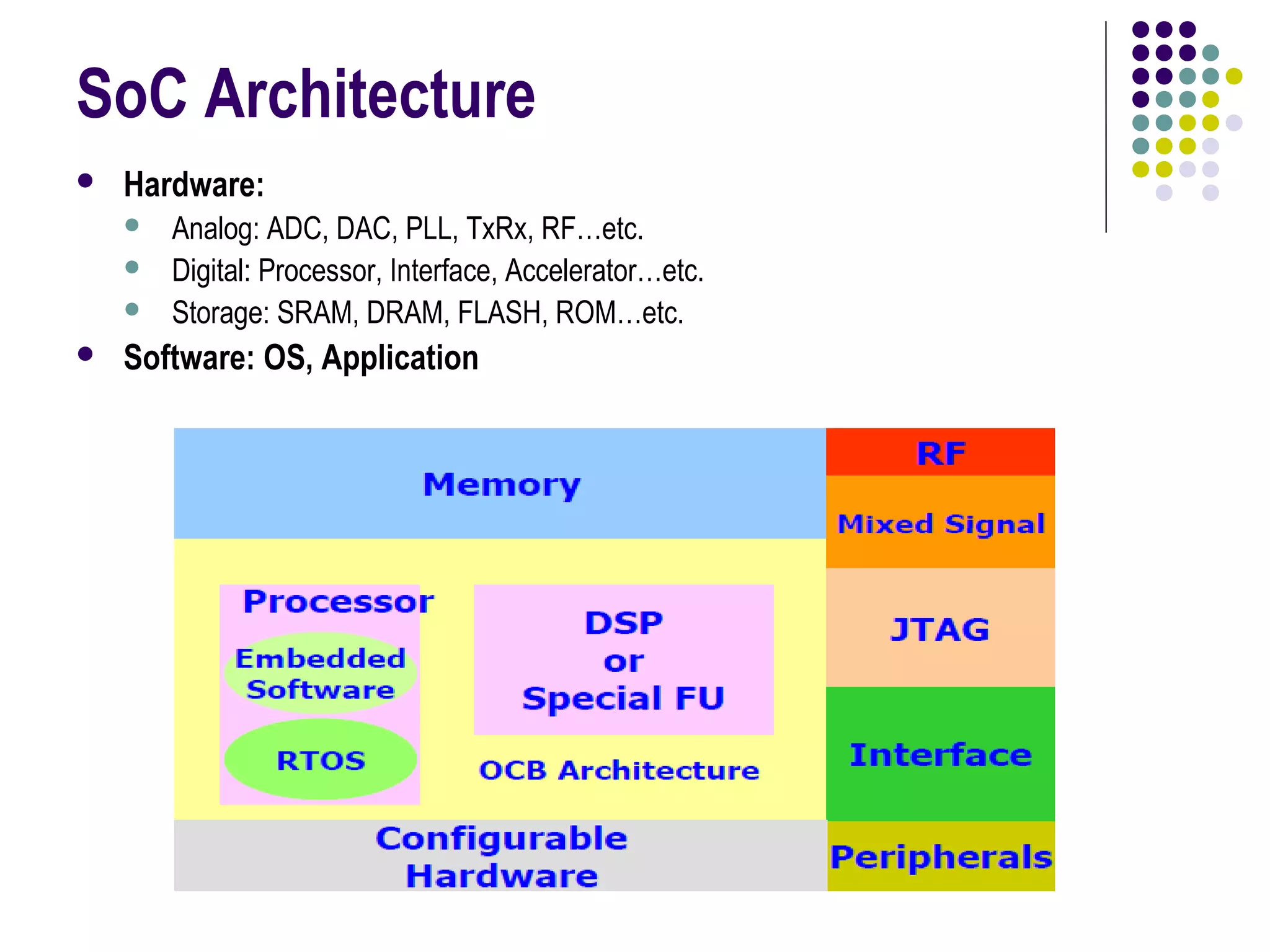

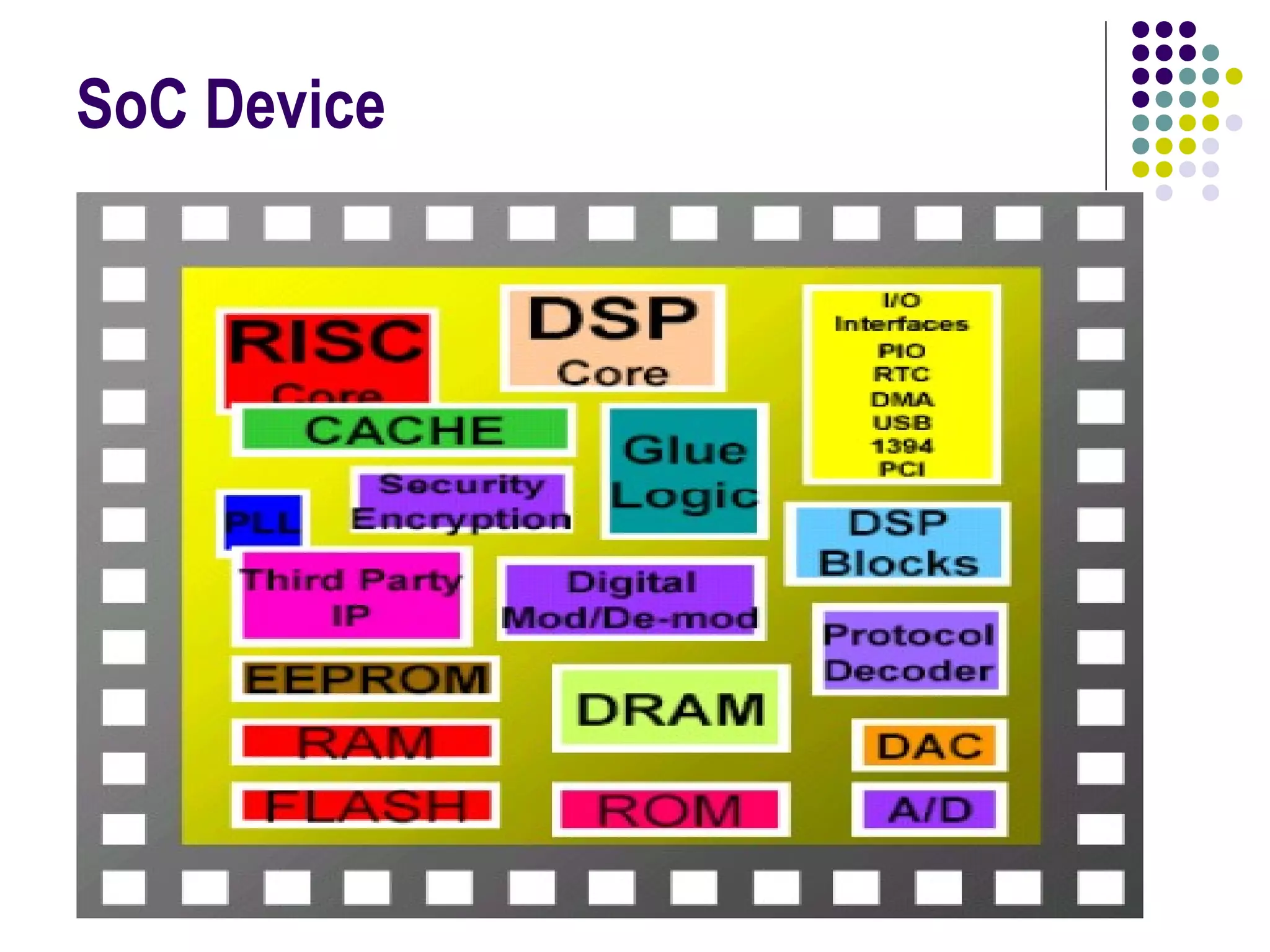

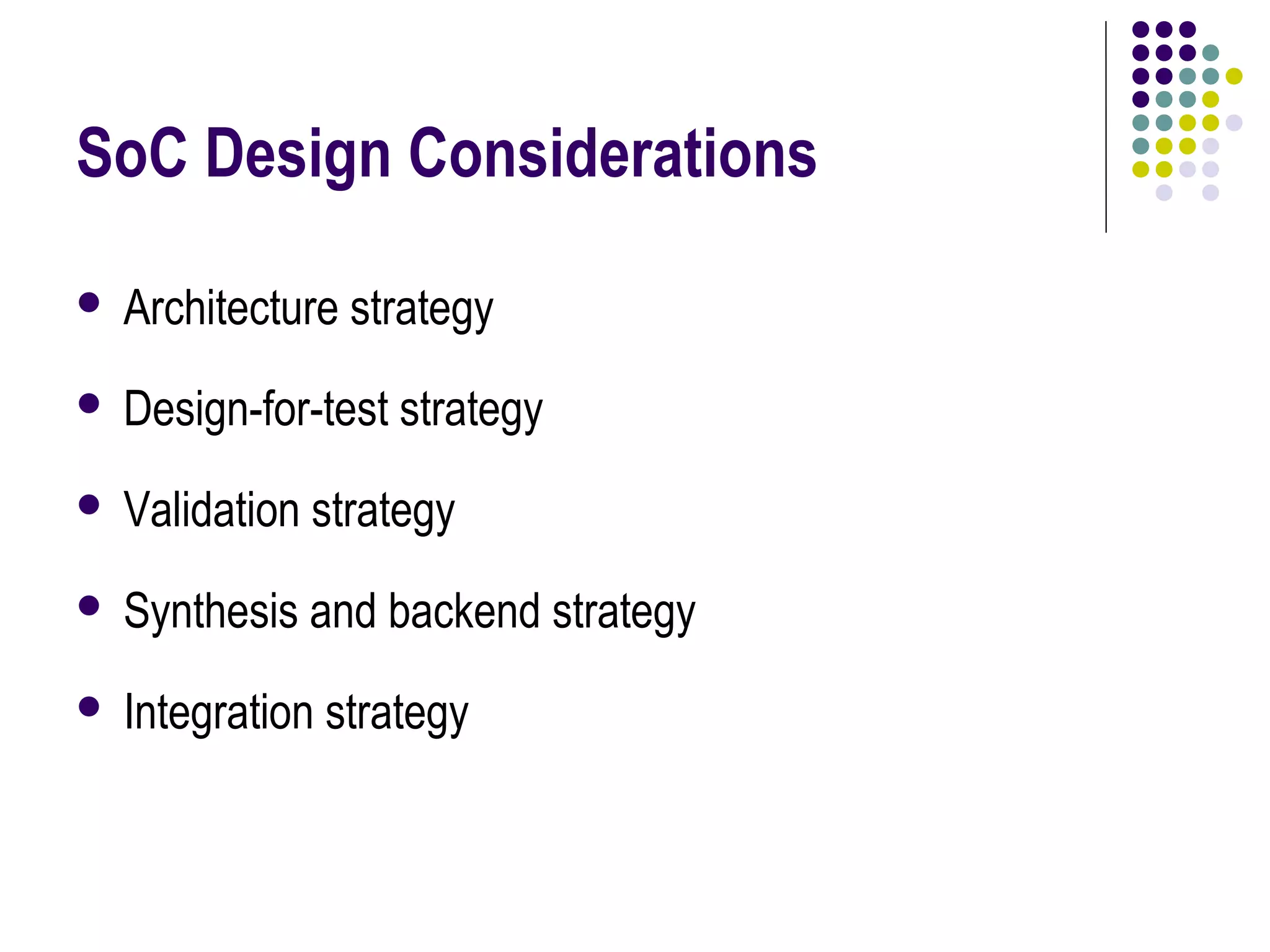

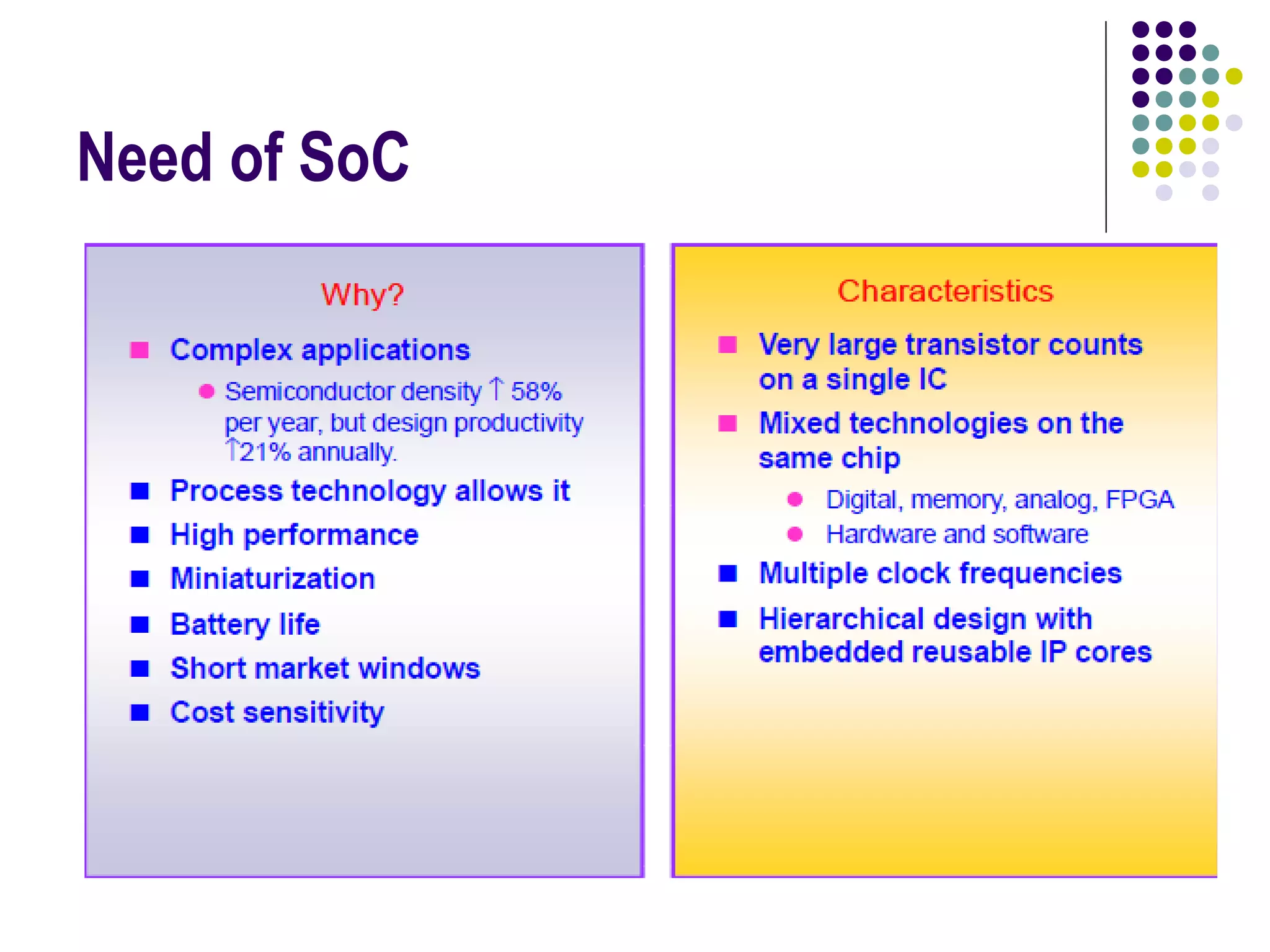

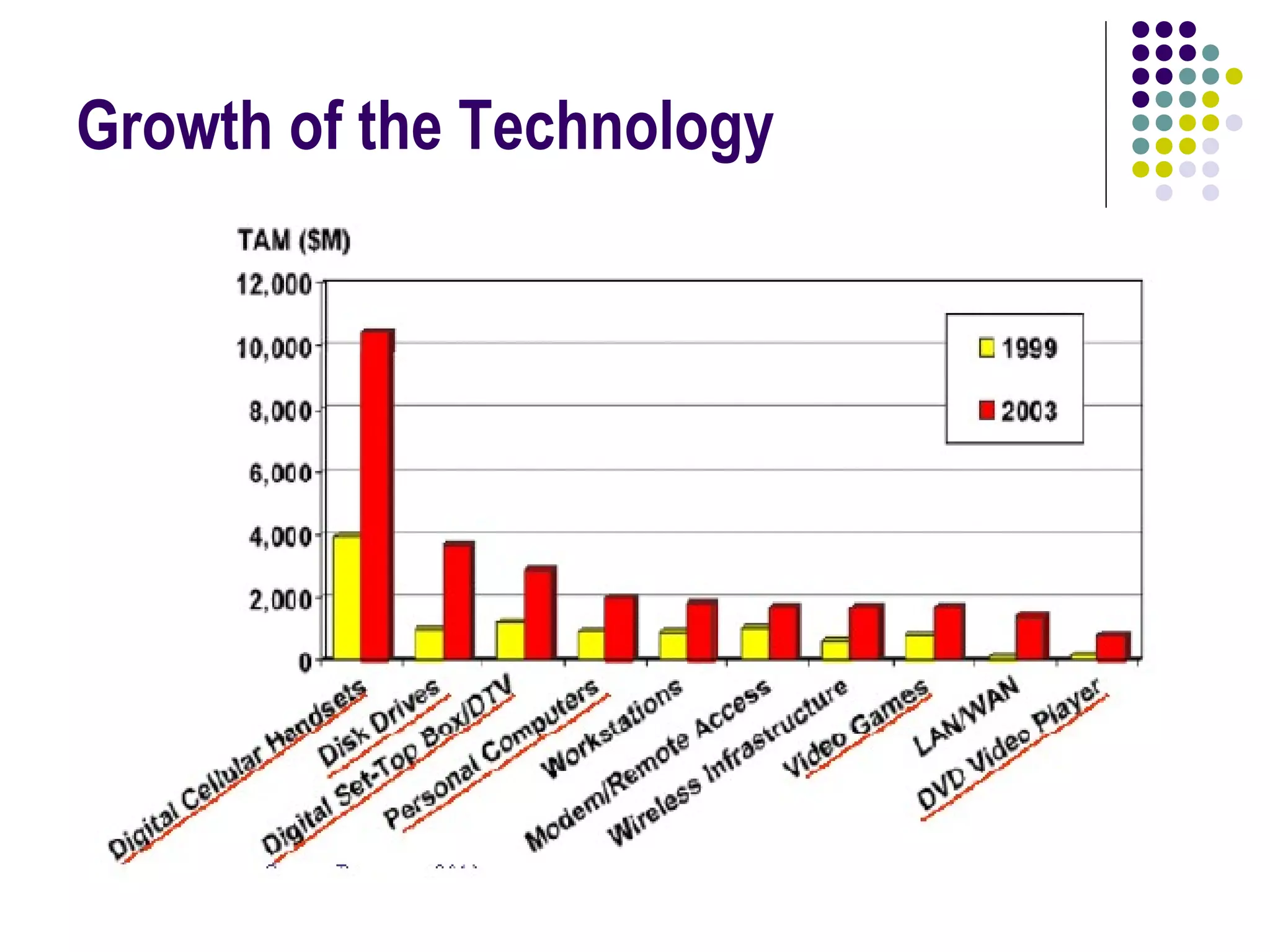

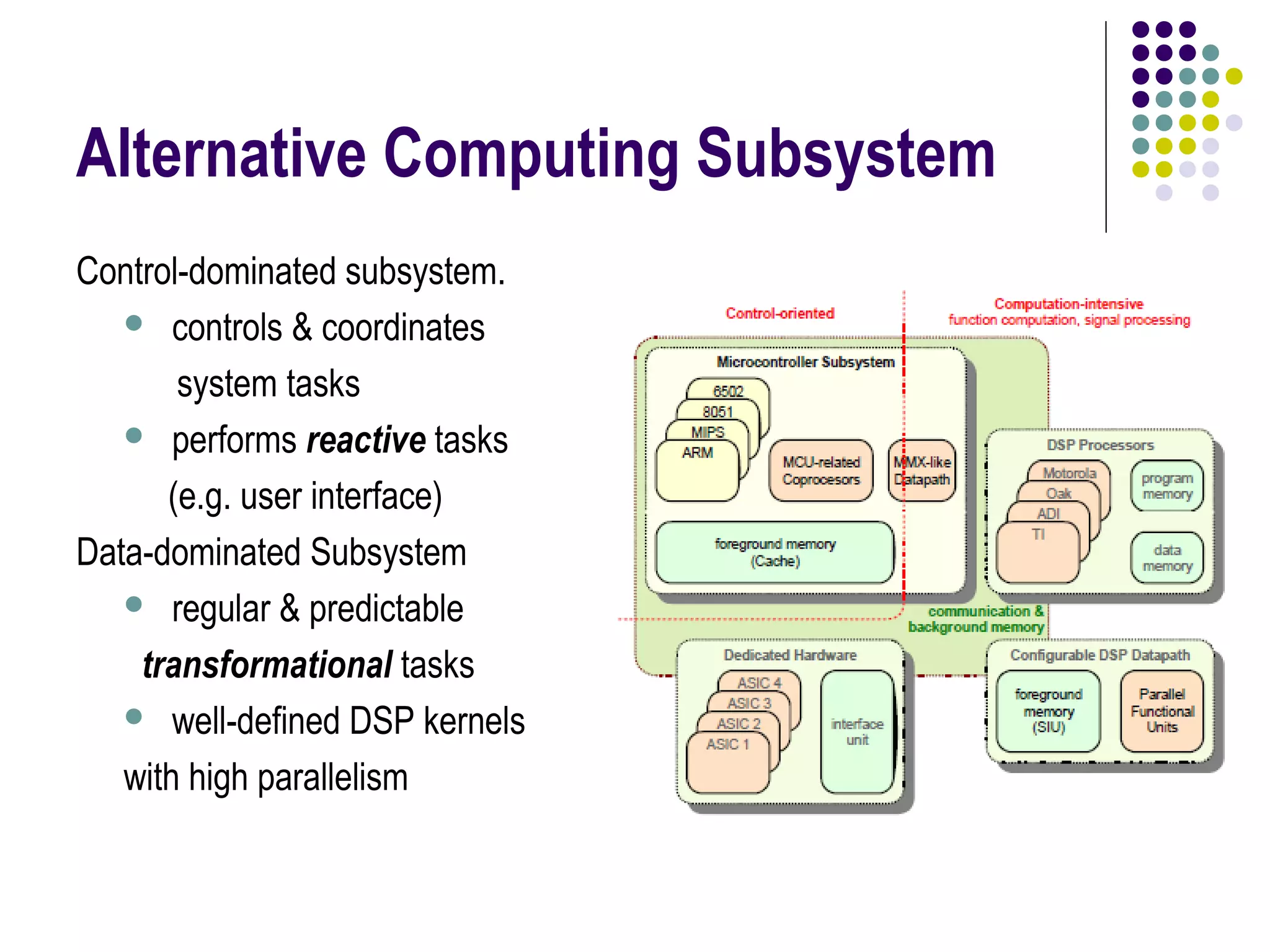

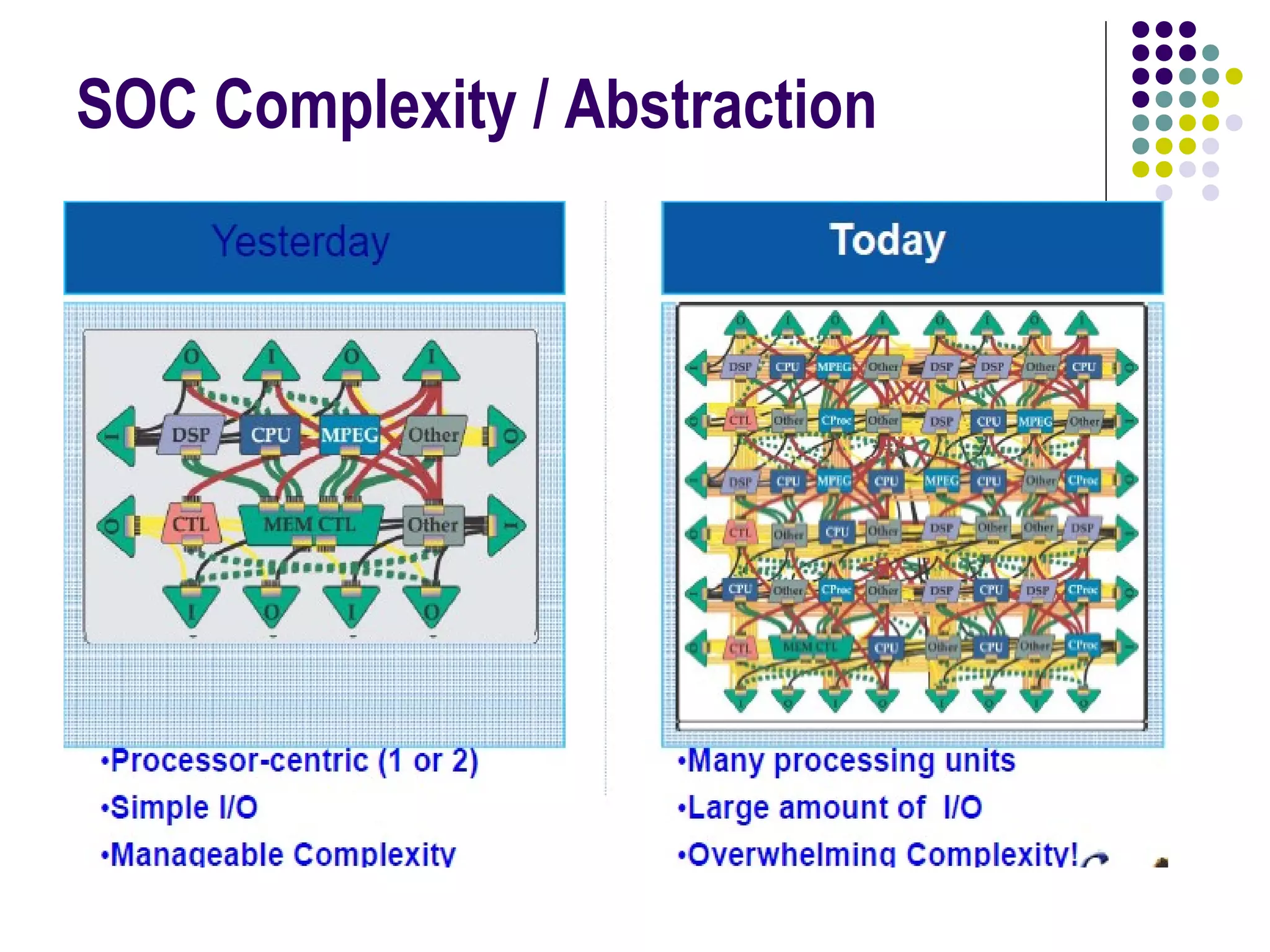

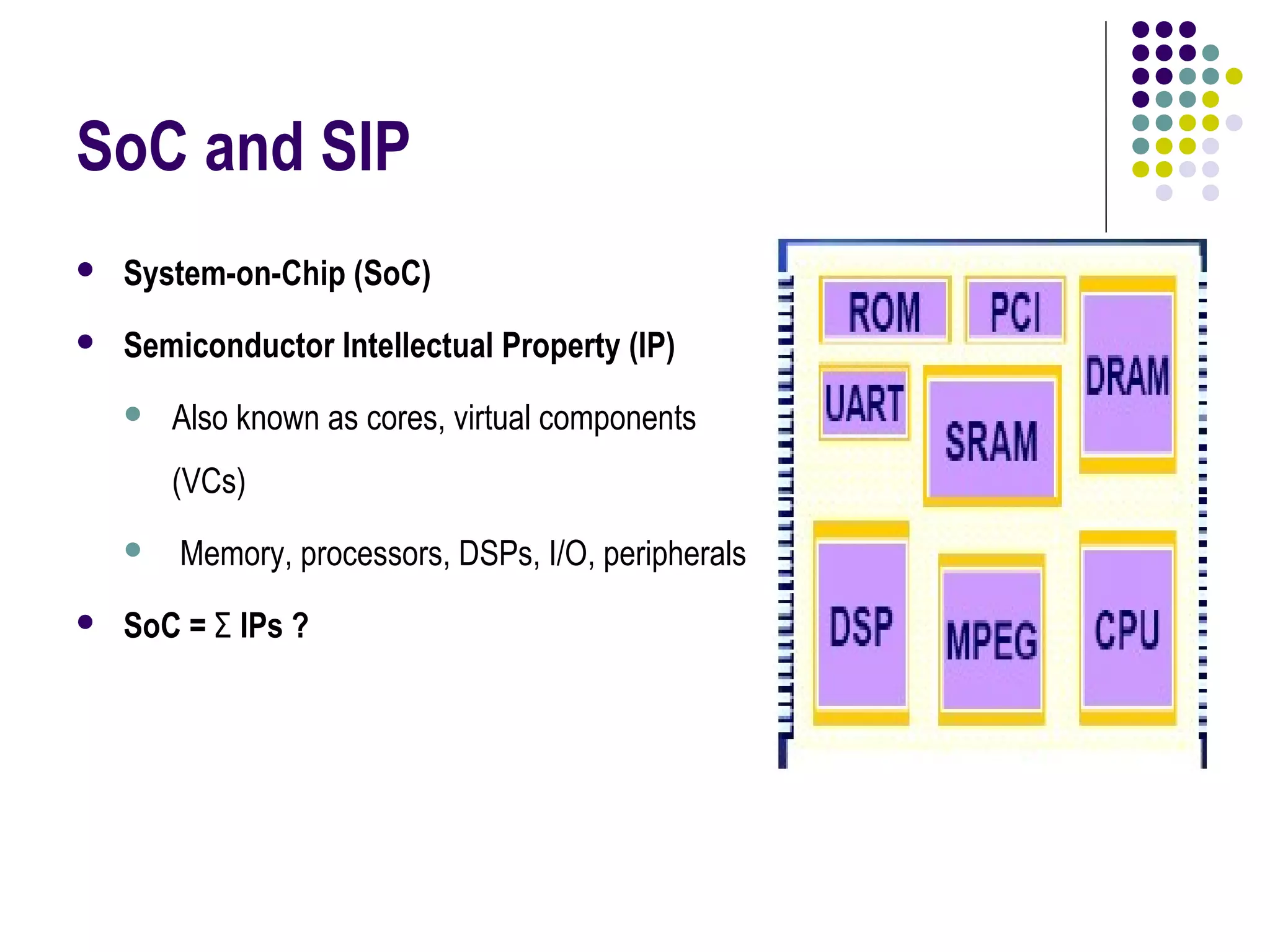

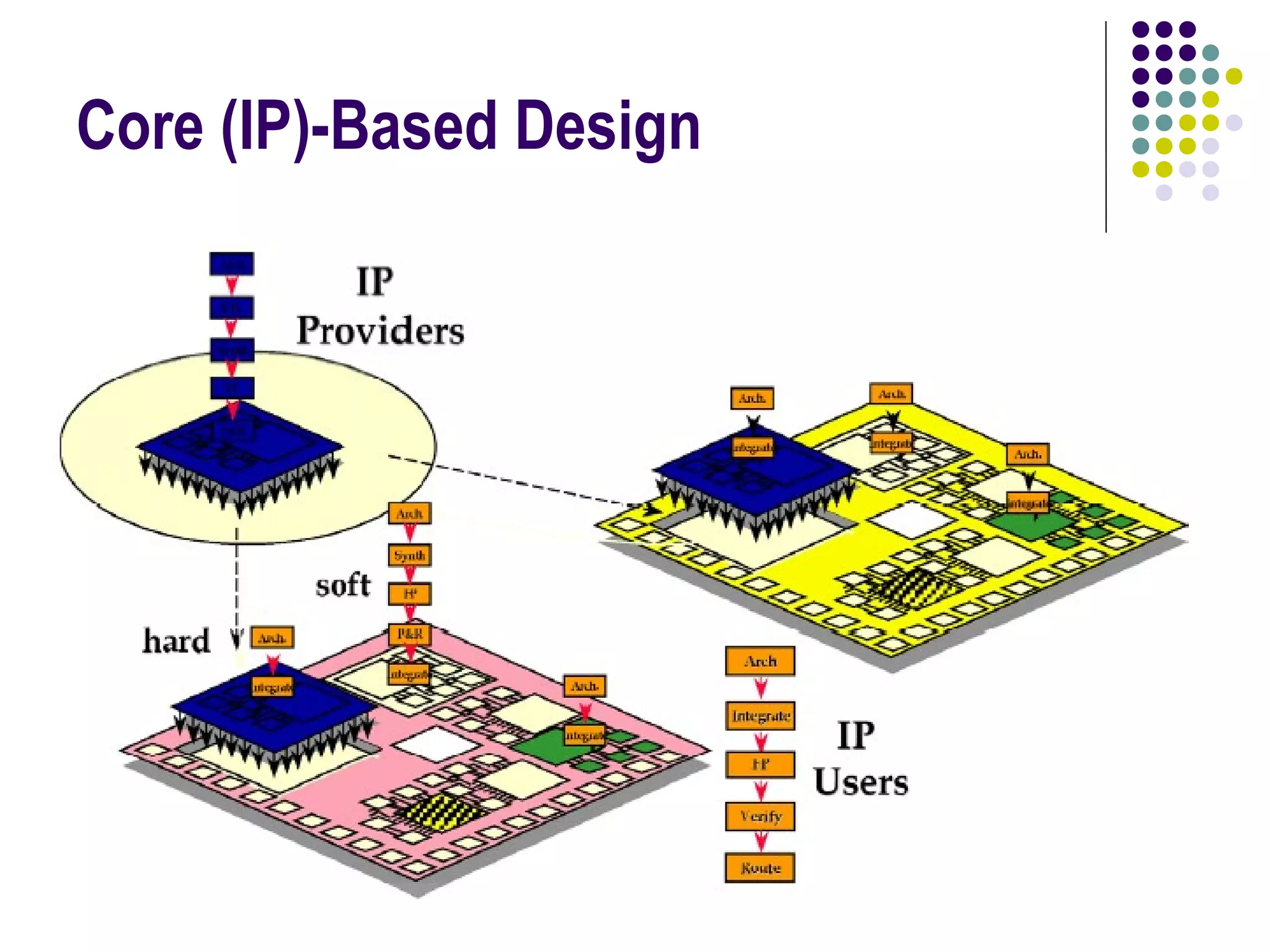

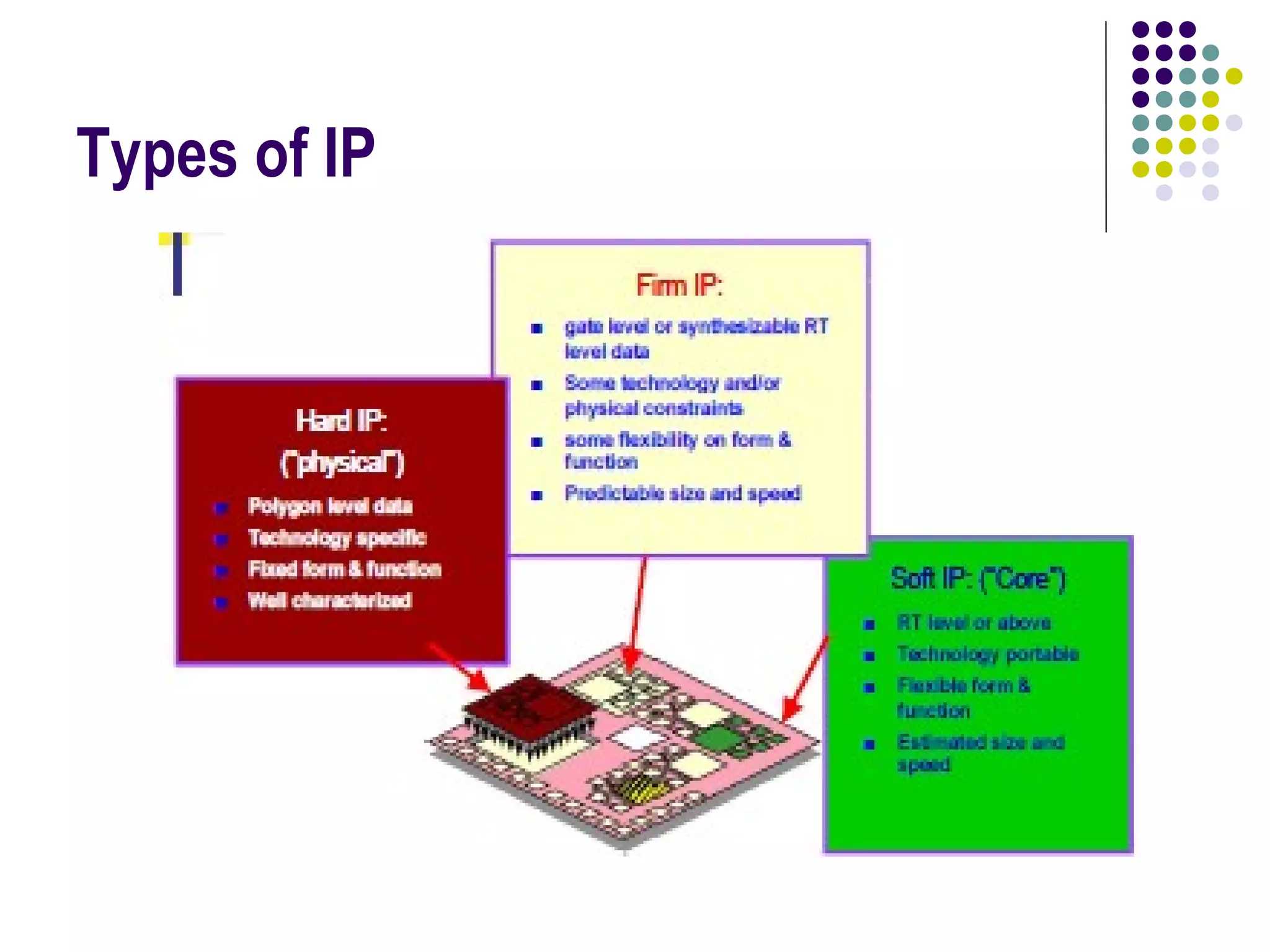

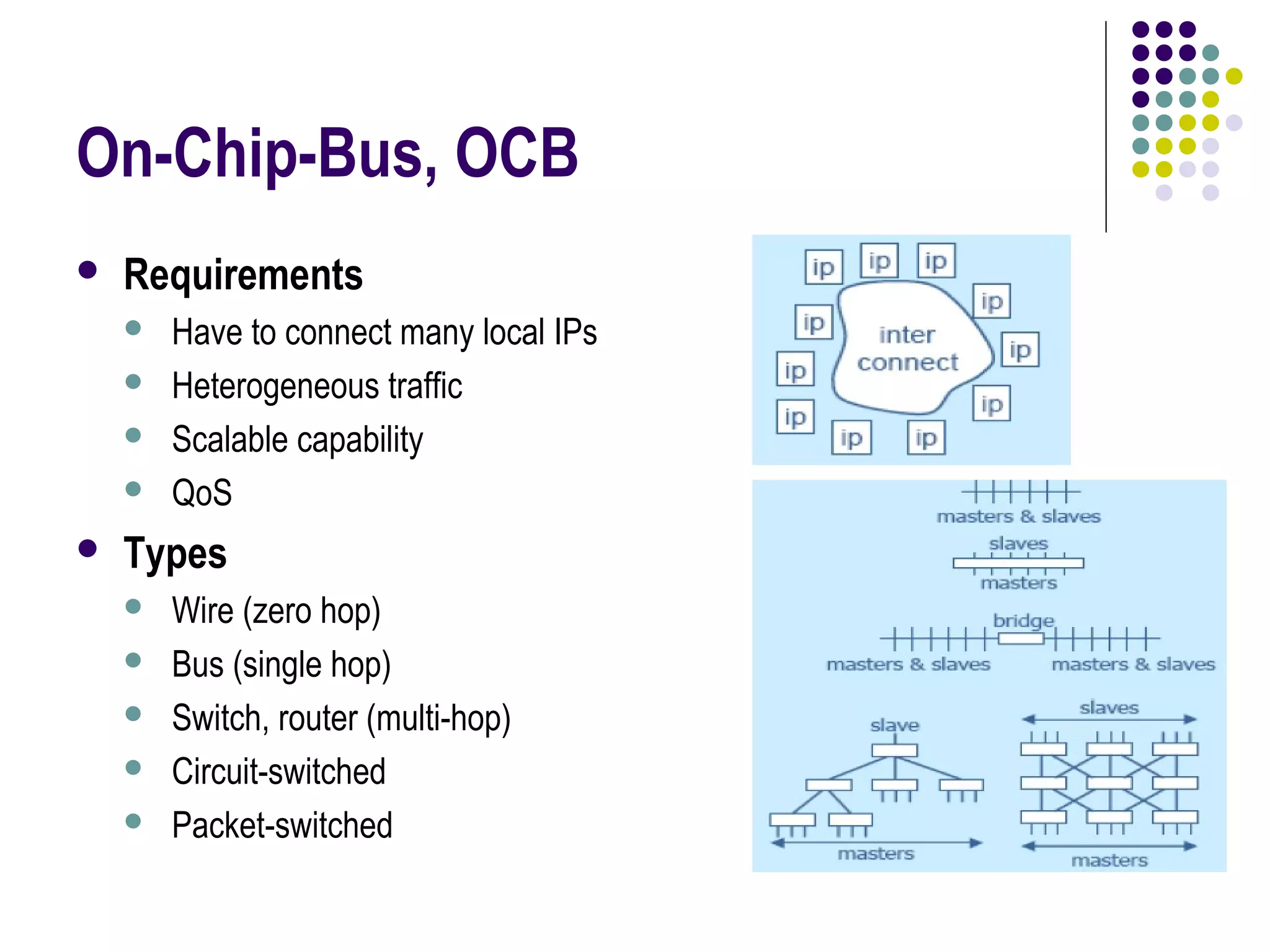

This document provides an overview of system on chip (SoC) design. It discusses that a SoC integrates all components of an electronic system onto a single chip, and that SoC design involves identifying user needs and integrating various intellectual property blocks. The document then covers SoC fundamentals like the use of soft and hard IP cores, the design flow from specification to fabrication, and strategies for addressing SoC complexity through partitioning, abstraction levels, and reuse of pre-designed components.