ZERO WIRE LOAD MODEL.pptx

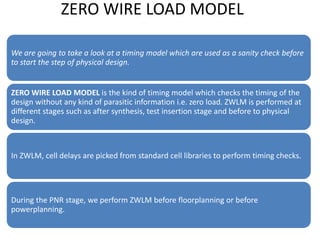

- 1. ZERO WIRE LOAD MODEL We are going to take a look at a timing model which are used as a sanity check before to start the step of physical design. ZERO WIRE LOAD MODEL is the kind of timing model which checks the timing of the design without any kind of parasitic information i.e. zero load. ZWLM is performed at different stages such as after synthesis, test insertion stage and before to physical design. In ZWLM, cell delays are picked from standard cell libraries to perform timing checks. During the PNR stage, we perform ZWLM before floorplanning or before powerplanning.

- 2. Why ZWLM? ZWLM is used to check the quality of Netlist and Constraints specified in SDC File. Ideally, zero wire load timing checks should be clean setup violation; hold violation should be under control because the tool is not aware of the actual position of the cell. If ZWLM timing checks are zero then we can guarantee the quality of netlist and constraints. But ZWLM timing checks are not clean, then we have to double checks the constraints. Setup violation in ZWLM must be zero and small (in term of value) hold violation is acceptable. But large hold violation also pointed something wrong in constraints. Violation in the asynchronous timing path is not considered. At this note of discussion, I wrapped up this topic and we will meet soon with a new topic of floorplanning. Thank you. Have a nice day!!!!

- 3. What is the difference between LVS and LEC in VLSI? LEC and LVS are checks used in different stages of physical design to ascertain the functionality and layout sanity respectively. Both are done at different phases of the PNR flow. LEC starts as early as the front end and goes on till the final tape- out phase whereas LVS is primarily a backend sanity check. LEC (Logic Equivalence Check) is the essential step to ensure the functional check between RTL and netlist as can also be depicted from the Fig. 1. Many EDA companies provide tools to do the check. Layout Versus Schematic (LVS) checking compares the extracted netlist from the layout to the original schematic netlist to determine if they match. The comparison check is considered clean if all the devices and nets of the schematic match the devices and the nets of the layout.

- 4. Tape out The term “tape out” was coined in 70's. Historically, engineered used a magnetic tape to store all the ASIC design files. The event of carrying out the tape to the foundry was thus called “tape out”. Tapeout is the final result of the design process for integrated circuits or printed circuit boards before they are sent for manufacturing. The Tapeout is specifically the point at which the graphic for the photomask of the circuit is sent to the fabrication facility. A photomask is an opaque plate with holes or transparencies that allow light to shine through in a defined pattern. They are commonly used in photolithography and the production of integrated circuits (ICs or "chips") in particular.

- 5. Sanity checks To ensure that the input received from the library team and synthesis team is correct or not. If we are not doing these checks then it creates problems in later stages of design. Basically, we are checking following input files: and make sure that these files are complete and not erroneous. 1. design/netlist checks 2. SDC checks 3. Library checks

- 6. Design checks: Check if current design is consistent or not It checks the quality of netlist and identifies: 1. Floating pins 2. Multidriven nets 3. Undriven input ports 4. Unloaded outputs 5. Unconstrained pins 6. Pin mismatch counts between an instance and its reference 7. Tristate buses with non-tristate drivers 8. Wire loops across hierarchies ICC command: check_design: Checks for multi driven nets, floating nets/pins, empty modules. Pins mismatch, cells or instances without I/O pins/ports etc.

- 7. SDC Checks: 1. If any unconstrained paths exist in the design then PNR tool will not optimize that path, so these checks are used to report unconstrained paths 2. Checks whether the clock is reaching to all the clock pin of the flip-flop. 3. Check if multiple clock are driving same registers 4. Check unconstrained endpoints 5. Port missing input/output delay. 6. Port missing slew/load constraints. ICC command: check_timing

- 8. Library checks: It validate the library i.e. it checks the consistency between logical and physical libraries. It checks the qualities of both libraries. check_library: This command shows the name of the library, library type & its version, units of time, capacitance, leakage power, and current. It shows the number of cells missing, the number of metal or pins missing in the physical and logical library. Ques: what checks you do as you get the netlist before going to the floorplan.?

- 9. Setup time& Hold time • Setup time is the amount of time required for the input to a Flip-Flop to be stable before a clock edge. Hold time is similar to setup time, but it deals with events after a clock edge occurs. Hold time is the minimum amount of time required for the input to a Flip-Flop to be stable after a clock edge.

- 10. Why do we give a keep out margin for macros during placement in VLSI? • Hi we give Keepout margin / halo around the macros so that it dont allow others cells to sit near The macros , and in this way Macros Pins are free to route,If you dont give then it may be possible that Std cells may come and sit near the Macros and this will lead to congestion ( a term in Backend VLSI where Available routing tesources are less than Requirement). • It allows placement of buffers and inverters in its area. • If the macros are moved from one place to another place, Halos will also be moved. But in the case of blockages if the macros are moved from one place to another place the blockages cannot be moved. • Now the above was explaination of 1st part of your ques i.e. Why we give? • Now 2nd part is not always true we dont give keepouts in placement stage to macros infact we do it before the actual placement of cells, so most of time in industry We give keepouts in Floorplanning stage only. • Now there are cases when you can have cells also which may have more pins and requires more routing resources e.g AOI,OAI, Multibit Flops now in these scenario you need to give keepouts around cells and it is called as cell padding. • Please see the attached diagram,hope it may help you.

- 11. Why do we give a keep out margin for macros during placement in VLSI? • Multiple reasons might be there depending on which technology you would be implementing the design. From a net delay perspective it gives enough distance between two boundary routes of abutted macros so that there is no extraneous coupling capacitance pickup • Keep out margin is a type of hard placement blockage which don’t allow the tool to place std cells in that area during any stage. It is added during floor planning around all the macros based on the physical implementation guidelines. But, this placement blockage sticks to the macro and is moved automatically unlike the usual placement blockage. • The margin is decided based on the macro. If it’s an external PHY or any analog macros, read the documentation that comes along with the IP and follow accordingly. Around the PHY, the vendor might expect 10 to 15um. For memories, usually 2 to 3 um based on the pin densities. • In Cadence tools, it is also called Halo. It need not be uniform in all the sides. • Sometimes, keep out margin is also added for the std cells like AOI, OAI etc. to spread them as these are high pin density cells especially their drive strength D1 cells. In this case, it is called cell/instance padding in Cadence tools. It is added to mitigate the local congestion.

- 12. Latch-up issue in the CMOS design Technically latch-up is the phenomena of activating the parasitic BJTs in a CMOS circuit which forms a low impedance path between the power and ground terminals. This low impedance path draws a large current and heats up the IC (Integrated Chip) which cause permanent damage of IC. Latch-up prevention techniques: Simply put, latchup prevention/protection includes putting a high resistance in the path so as to limit the current through supply and make β1 *β2 < 1. This can be done with the help of following techniques: Surrounding PMOS and NMOS transistors with an insulating oxide layer (trench). This breaks parasitic SCR structure. Latchup Protection Technology circuitry which shuts off the device when latchup is detected

- 13. • Blockages used in Physical Design mainly for two purpose, Placement and Routing. • Placement Blockages: There are mainly three types. • Hard Blockage- No cell is allowed to place in specified region. • Soft Blockage- Only buffers/inverters needed for optimization are allowed to place in specified region. • Partial Blockage- Any type of cells are allowed to place but only for defined area of specific region. (like 60% of specified area) • Routing Blockages: There are mainly two types. • Hard Blockage- Any type of net is not allowed to route through specified region. • Signal Blockage- Any type of data and clock signal net is not allowed to route through specified region, but power net is allowed to route.

- 14. The 6 important inputs of the PD (in no particular order) are: 1) Gate level Netlist :– Format= .v · Given by Synthesis team. · It is a synthesized and an optimized netlist which contains information of all the logical connections of the standard cells and macros. · It has cell info, net info, pin/port information. 2) Physical library :- Liberty Exchange Format (LEF) · File format = .lef(Cadence), .FRAM(Synopsys). · Given by Vendor. · It contains all the physical information of all the standard cells and macros. · Info such as – shape, size, symmetry, orientation of the cells are present. · Pin information like- pin names, direction, shape, antenna related info are also defined.

- 15. 3) Technology file :- · Format = .techlef (Cadence), .tf(Synopsys). · Given by Foundry. · It contains all the metal layer info like – shape, color, width, pitch, area, spacing between metal layers, base layer info, resistance (per sq. unit). · It contains technology node info. · It has unit info (Ex: ns). · Tech file is written in ASCII format. 4) TLU+ file:- · Format = .tlup · Given by Fab team. · It has RC parasitic info per unit length of the metal. · RC values are used to calculate the net delay. · Either .tlup file or .itf file is used.

- 16. 5) Logical library :- · Format = .lib, .db · Given by Vendor. · It contains functional and timing information of all the cells. · Timing details such as cell delays, setup time, hold time. · Design rules – max capacitance, max transition, max fanout are defined. · It also has PVT(Process Voltage Temperature) parameters. · Cell delays are checked from lookup table. 6) SDC:- Standard Design Constraints :- · Format = .sdc · Given by Synthesis team. · This contains all the timing constraints. · Constraints – Clock definitions, input delay, output delay, clock latency, clock uncertainity. · Exceptions – Mutlicycle path, false path, disable timing arc, half cycle path details are described. A few other files are also used – · MMMC :- Multi-Mode Multi-Corner file It is used to generate different analysis views based on different delay corners and constraints modes. · UPF :- Unified Power Format This file is used when a single chip uses multiple voltages.

- 17. • In Physical aware synthesis, we will provide floor plan DEF as one of the input to the synthesis tool. Floor plan DEF will contains the physical information like placement of macros, placement of input & output ports, die area & placement blockages. Also, RC co- efficient file can be given as input to synthesis tool for better calculation of wire resistance & capacitance compared to wire load model method. • Advantages of Physical aware synthesis: • Gives better PPA (power, performance, area) • Will give better timing correlation between synthesis and PnR results • Improvement in Power • PnR run time also reduces because of lesser violations

- 18. Why don't we do routing before CTS in VLSI Physical Design? • Routing means Providing physical connectivity to all the logical connections in your design,where actual lay down of metal layer will occur and also track is assigned for each metal layer. • But if you have idea of Physical synthesis you will know that we don't senthesize HFN and clock nets during synthesis so first task is to synthesize these two before routing then that's why HFN synthesis is done in placement and clock nets are synthesize in CTS . But ques here can be raised why we need to synthesize these two,so let me help you if you don't synthesize HFN or clock nets then port of such HFN may drives numerous logic and if you route your design here only then they will consume almost all the routing resources which me leads Congestion and apparently leads to thousands of shorts in your design which you will die of fixing :( • P.S: some companies will do a trial route in each intermediate stage to check approximate number of shorts and open.

- 19. Drive strength • Drive strength simply means how much strength it needs to drive output cap/load. More is the drive strength, lesser will be the internal resistance, more is the current can be drawn from vdd and quickly, lesser is time it will take to charge the output cap, and finally lesser will be the delay. Drive strength is a measure of how much load a standard cell can drive. The load is nothing but the combined capacitance of all its fanouts (other cells being driven by our cell).The strength of cells used in the design is a tradeoff between leakage and speed. High strength -> high leakage and higher speed and low strength -> low leakage and slower speed.

- 20. How are insertion delay and timing interrelated in VLSI PD? What would happen to timing violations if insertions delay increased or decreased? • The simple answer is that you will face timing issues. When we build the clock tree, we cravingly want the global skew in any clock tree or skew group to be minimal. It means the capture and launch path delay (ID: Insertion Delay) is balanced. The design is already has the optimized data path with the ideal clock during placement and now it’s ensured that the clock reaches at all the flop clock pins at the same time as much as possible. When there is a large differences in launch and capture clock path, it’s very difficult to close timing in further stages. This is the only stage and also the critical stage of PNR where we keep our hands in the clock network. So, you have to make sure that ID in a clock tree do not have much standard deviation. If you do so, you will not get setup and hold violations post CTS with a huge negative slack. But it’s not the case. There is always a considerable amount of skew post CTS. This is why, we do post CTS optimization keeping the clock network untouched or playing around with the useful skew. • To answer your second question, to avoid timing violations, it’s sufficient that we maintain the same ID throughout the clock tree. I have stated earlier that we need to bring down the skew as much as possible. But be it a big or small latency, as long as you make the skew littlest, your design free from timing issues. Still, why the design architect always wanted the ID as low as possible. Due to the following reasons, • The clock network will have smaller common clock chain of inverters/buffers so that the OCV impact is less. Besides when the derates are applied, the clock path delay will worse if there is a long chain. • Secondly, it will decrease the number of clock inverters/buffers. They are the highly power consuming cells as their toggle rate is 200%. So, it will bring down the clock tree network power. • Thirdly, when the number of cells are reduced in any stage, it always helps in improving the congestion. • I hope that I answered your question !!

- 21. The setup time is the interval before the clock where the data must be held stable. The hold time is the interval after the clock where the data must be held stable. Hold time can be negative, which means the data can change slightly before the clock edge and still be properly captured. Most of the current day flip-flops has zero or negative hold time. • Hello, the insertion delay concept comes into picture in clock tree synthesis. • While building the clock tree ,cts starts building the clock from the clock source to the sinks . • Once The clock is built, the clock signal has to travel from the source to the sinks. The amount of time taken by the clock signal to travel from source to sinks is called the insertion delay. • Ex. At point A the clock source was there, so clock started building from point A, it has to reach the sinks (flops) points B,C,D (flops) . So from point A to point B C D the clock signal has to travel but in between it will build some logic to balance all three sinks because signal has to reach 3 sinks B C D at a time it is called SKEW Balancing( main aim of CTS) • The amount of time taken by clock signal from point A to B C D is called insertion delay. • You can refer to LATENCY concepts for more in depth information.

- 22. • There are multiple number of ways through which you can decrease the cell delay • Decrease the output load of that cell • Improve the transition time of signal which is input to that cell • You can use LVT cells ( Transistors with lower threshold voltages) they have less delay but more leakage power • Sizing also helps you to play with the delay. Increasing the size will see less resistance of the cell hence cell delay will be less • More the voltage, cell delay will be less . But generally we have fixed voltages present in the design.

- 23. What is a SDF file related to VLSI Physical Design? • SDF stands for Standard delay format. • It gives information on the timing data extensively used in backend VLSI design flows. • SDF gives information about • Path delays • Interconnect delays • Timing constraints • Tech parameters affecting delays • Cell delays. • SDF file is also used in the back annotation of delays in the gate level simulations for mimicking the exact Si behavior.

- 24. Power calculation and planning • A VLSI chip in the semiconductor industry is intended to perform a specific operation and has to communicate with the outside world through various signals. To have this signal flow to the chip and out of the chip we need a power supply. Hence proper power planning became an essential part of the planning process in the back-end of the VLSI chip design. • An appropriate power supply network must be constructed by considering many aspects such as design methodologies and considerations and the process technology used. • Let us consider an example to estimate the total VLSI Chip power, what are the things the designer should plan for?. The first thing the designer can make use of low Vth (threshold voltage) devices and dynamic CMOS circuits for the design. Second thing designed should make use of low power clock gating techniques and the Third, avoid the switching noise by placing decoupling capacitors.

- 25. Key points to be considered during power planning • Generally, the power planning process is an iterative process that includes, • 1. One must simulate that the higher power dissipation components in the design in the early power planning process. • 2. The total VLSI chip power must be quantified at the early stage. • 3. The total power of the chip and the total maximum power density of the chip must be analyzed. 4. Power fluctuations of the VLSI chip must be thought and analyzed. • 5. The clock gating process will include inherent and add fluctuations to chip power, those must be taken care of. • Also Maximum, Minimum and Averaged power distribution analysis and Multicycle power fluctuations should be considered.