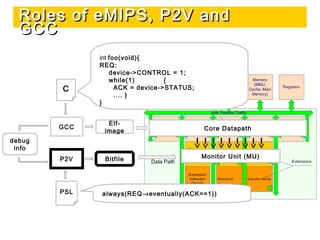

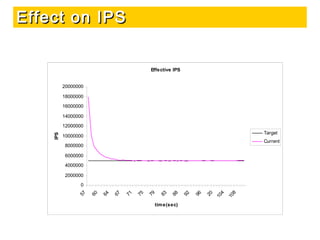

This document provides an overview of the eMIPS project, which allows for dynamically extensible processors using an FPGA. The eMIPS processor extends itself at runtime using extensions that are safe for multi-user operating systems. Applications include speeding up execution with application-specific CPUs, monitoring software in real-time, loadable debugging support, and loading/unloading peripherals and processor cores dynamically. The document describes the eMIPS workstation, binaries with hardware acceleration, assertion-based verification, extensible peripherals and tools like an extensible debugger. It also covers using hardware extensions to optimize the instruction set architecture, and the Giano real-time simulation framework.