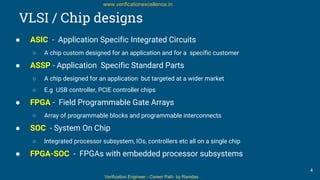

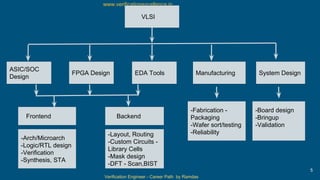

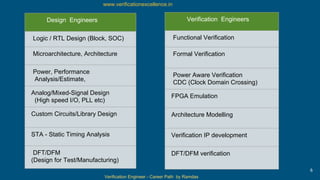

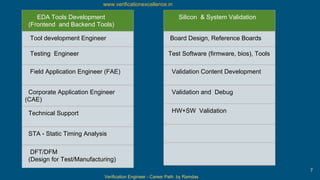

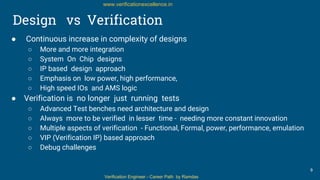

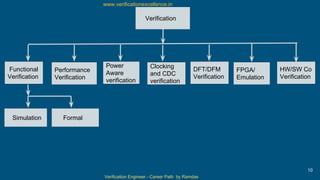

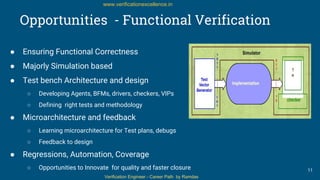

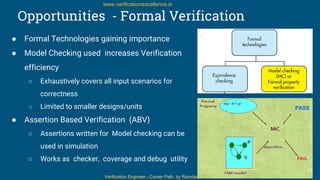

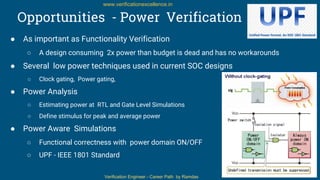

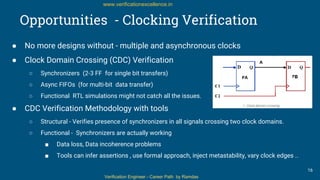

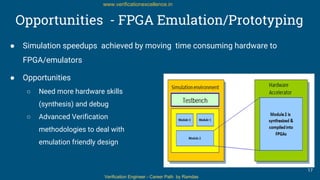

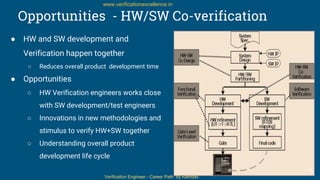

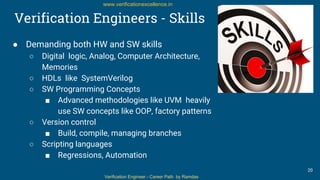

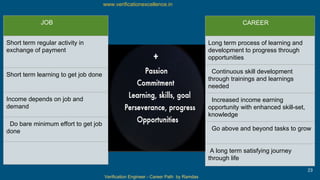

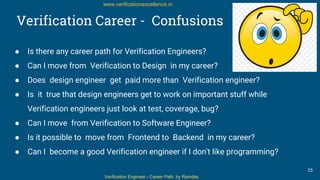

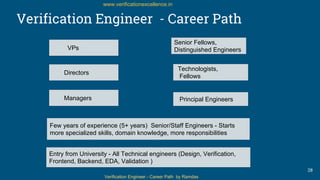

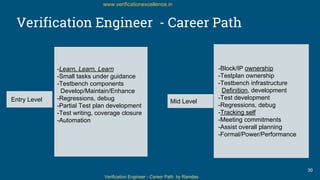

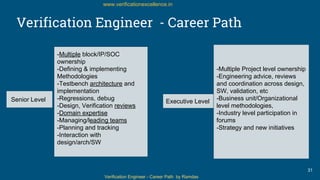

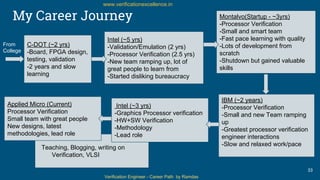

The document outlines the career path and opportunities for verification engineers in the VLSI domain, emphasizing the increasing complexity of designs and the critical role of verification. It covers various aspects such as job categories, skills required, and the importance of functional, formal, performance, and power verification. Additionally, the document discusses the potential for career advancement and the need for continuous learning and innovation in verification engineering.